JPEG2000 EBCOT encoder based on Avalon bus

A technology of encoders and arithmetic encoders, applied in the field of EBCOT encoders, can solve problems such as poor flexibility, complicated process, and slow speed, and achieve the effect of saving resources and increasing encoding speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

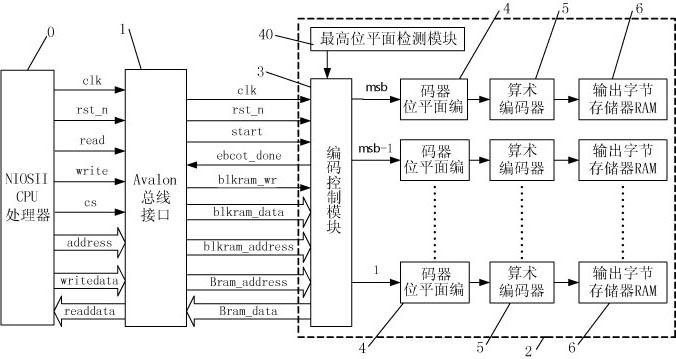

[0010] Specific implementation mode one, combine figure 1 Describe the present embodiment, based on the EBCOT encoder of Avalon bus JPEG2000, it comprises NIOSIICPU processor 0, Avalon bus interface 1 and EBCOT Tier-1 encoder 2, and described EBCOT Tier-1 encoder 2 is internally solidified with the highest bit plane detection module 40 , encoding control module 3, a plurality of bit plane encoders 4, a plurality of arithmetic encoders 5, a plurality of output byte memory RAM6, the NIOSIICPU processor 0 is connected with the EBCOT Tier-1 encoder 2 through the Avalon bus interface 1,

[0011] NIOSIICPU processor 0 sends start signal start to encoding control module 3 through Avalon bus interface 1, encoding control module 3 starts encoding after receiving start signal start, NIOSIICPU processor 0 writes signal blkram_wr, encoding block data signal blkram_data and encoding block through encoding block The address signal blkram_address writes coefficient data to the EBCOTTier...

specific Embodiment approach 2

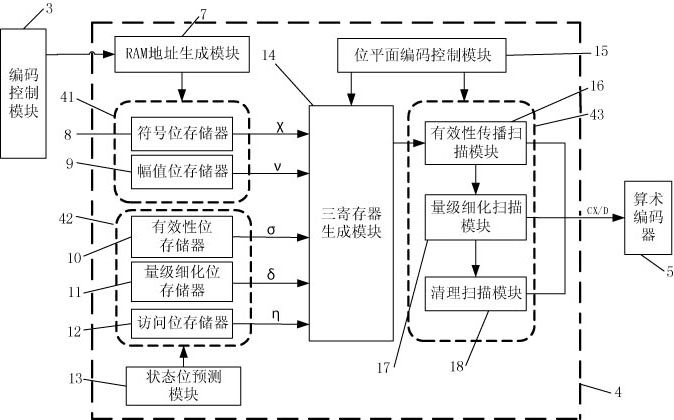

[0015] Specific implementation mode two, combine figure 2This embodiment is described. This embodiment is a further description of the bit-plane encoder 4 in the first embodiment. The bit-plane encoder 4 includes a RAM address generation module 7, a wavelet coefficient random access memory RAM41, a state bit random access memory RAM42, a state Bit prediction module 13, three register generation module 14, bit plane coding control module 15, three scanning coding module 43, described wavelet coefficient random access memory RAM41 is made up of sign bit memory 8 and amplitude value bit memory 9, and described status bit random access memory RAM42 is made up of validity bit memory 10, magnitude refinement bit memory 11 and access bit memory 12, and described three-scan encoding module 43 is made up of validity propagation scanning module 16, magnitude refinement scanning module 17 and cleaning scanning module 18 ,

[0016] The image information output by the encoding control ...

specific Embodiment approach 3

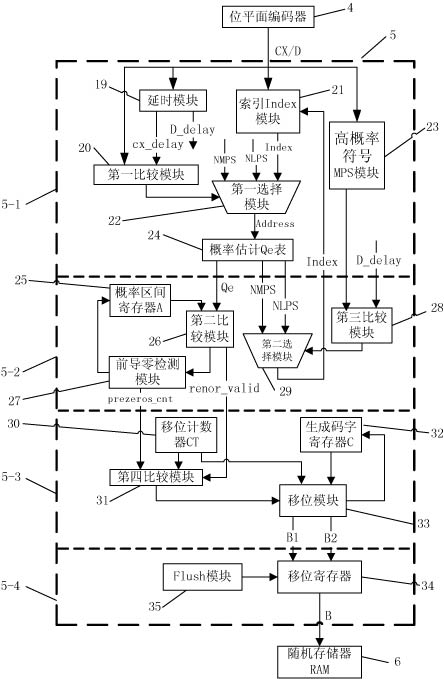

[0027] Specific implementation mode three, combine image 3 Describe this embodiment, this embodiment is a further description of the arithmetic encoder 5 in the specific embodiment one, the arithmetic encoder 5 includes four-stage pipeline modules: the first-stage pipeline module 5-1, the second-stage pipeline module 5- 2. The third stage pipeline module 5-3 and the fourth stage pipeline module 5-4,

[0028]The first-stage pipeline module 5-1 includes a delay module 19, a first comparison module 20, an index Inder module 21, a first selection module 22, a high probability symbol MPS module 23 and a probability estimation Qe table 24, and the delay module 19 , the first comparison module 20, the index Inder module 21 and the high-probability symbol MPS module 23 simultaneously receive the context vector CX and decision information D of the encoded information sent by the bit-plane encoder 4, and the delay module 19 converts the context vector CX of the received encoded infor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More