Low-voltage resistive random access memory and preparation method thereof

A resistive variable memory and resistive variable technology, applied in the direction of electrical components, etc., can solve the problems of increasing process steps, high turn-on voltage and turn-off voltage, difficulties, etc., to achieve large application prospects, turn-off current optimization, low resistance variable voltage and resistance The effect of variable current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

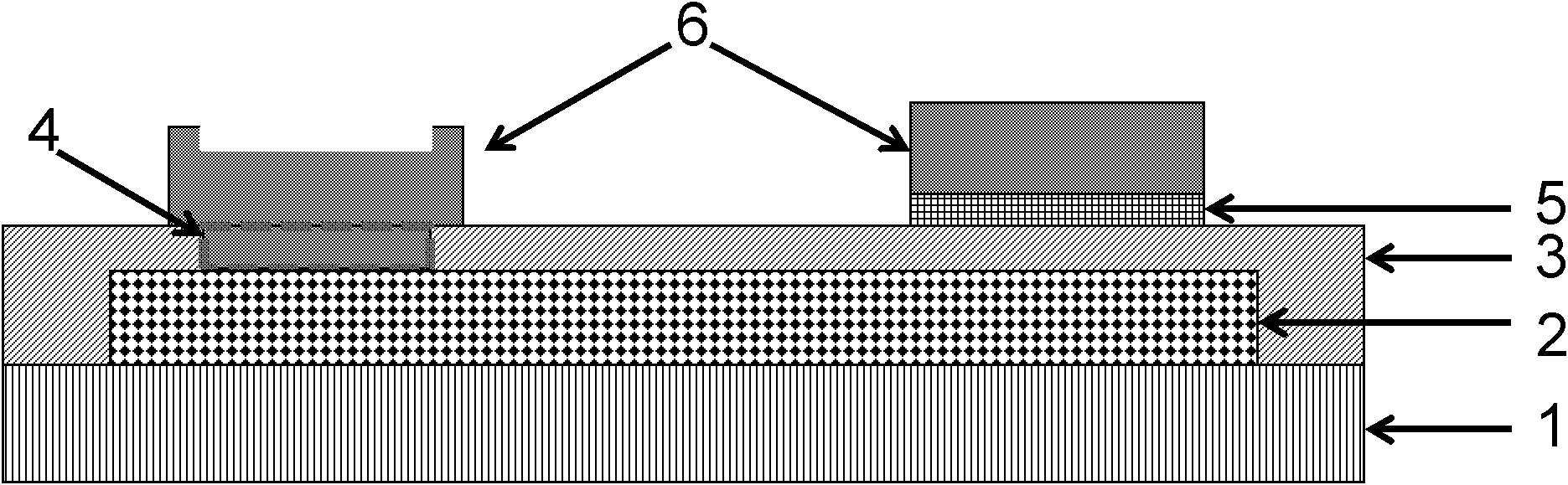

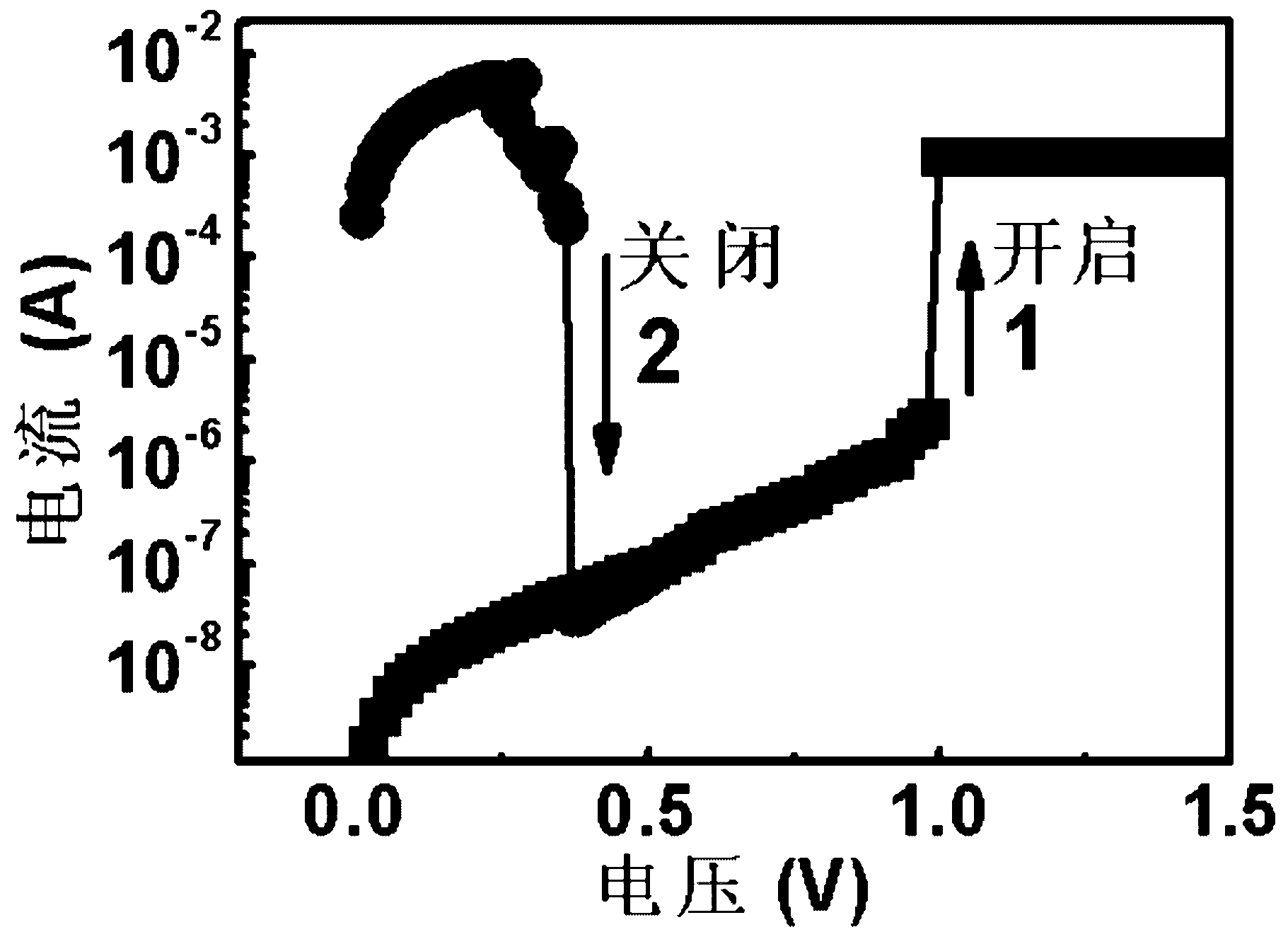

[0028] The schematic diagram of the cross-sectional structure of the resistive memory made in this embodiment is as follows: figure 1 As shown, the preparation process of the resistive variable memory of this example is described below in combination with the schematic cross-sectional structure.

[0029] 1) First, a layer of W metal is prepared on the silicon substrate 1 by physical vapor deposition (PVD) method or other film-forming methods in the IC process, and the bottom electrode is patterned using standard photolithography techniques to form the bottom electrode 2 .

[0030] 2) Adjust N in PECVD 2 O and SiH 4 The ratio of gas flow to SiH 4 :N 2 O=50:100, the resistive material layer SiO was prepared 0.4 N 0.4 . The PECVD process parameters are as follows: power=60W, air pressure=550mtorr, temperature=300°C.

[0031] 3) Define the bottom electrode lead-out hole by photolithography and etching;

[0032] 4) Same as the bottom electrode, the top electrode and its pr...

Embodiment 2

[0041] 1) First, a layer of W metal is prepared on the silicon substrate 1 by physical vapor deposition (PVD) method or other film-forming methods in the IC process, and the bottom electrode is patterned using standard photolithography techniques to form the bottom electrode 2 .

[0042] 2) Adjust N in PECVD 2 O and SiH 4 The ratio of gas flow to SiH 4 :N 2 O=30:150, the resistive material layer SiO was prepared 0.7 N 0.5 . The PECVD process parameters are as follows: power=60W, air pressure=550mtorr, temperature=300°C.

[0043] 3) Define the bottom electrode lead-out hole by photolithography and etching

[0044] 4) The top electrode and its protective electrode are prepared by PVD method or other film-forming methods in the IC process, and the protective electrode is platinum, titanium or gold.

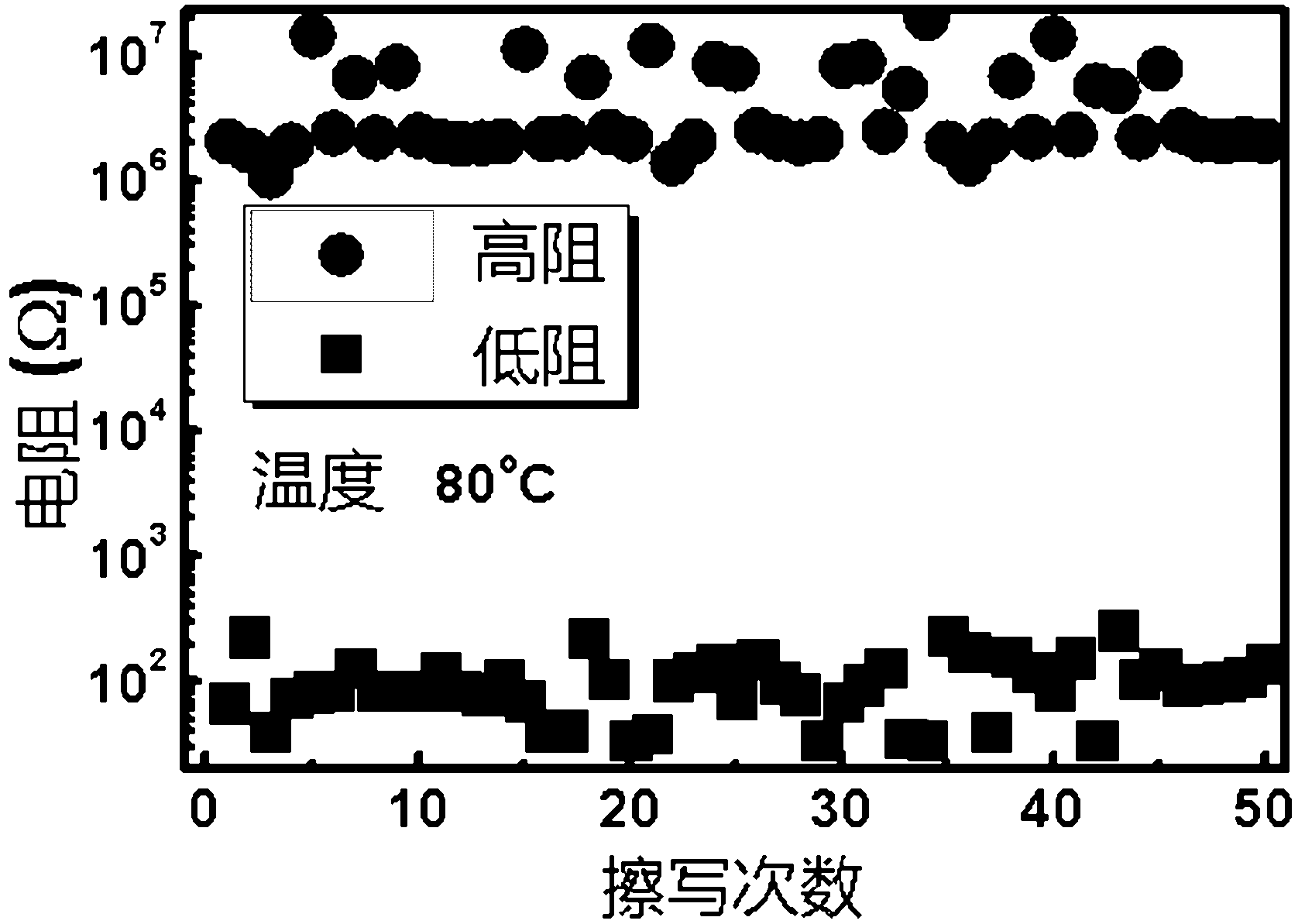

[0045] The resistive memory (W / SiO 0.7 N 0.5 / Cu) is similar to the resistive memory made in Example 1 in its resistive characteristics, erasable characteristics and retent...

Embodiment 3

[0047] 1) First, a layer of Pt metal is prepared on the silicon substrate 1 by PVD method or other film-forming methods in the IC process, and the bottom electrode is patterned using standard photolithography techniques to form the bottom electrode 2 .

[0048] 2) Adjust N in PECVD 2 O and SiH 4 The proportion of SiH 4 :N 2 O=14:150, the resistive material layer SiON was prepared 0.6 . The PECVD process parameters are as follows: power=60W, air pressure=550mtorr, temperature=300°C.

[0049] 3) Define the bottom electrode lead-out hole by photolithography and etching;

[0050] 4) The top electrode and its protective electrode are prepared by PVD method or other film-forming methods in the IC process, and the protective electrode is platinum, titanium or gold.

[0051] The resistive memory (Pt / SiON) prepared in this embodiment 0.6 / Cu) is similar to the resistive memory made in Example 1 in its resistive characteristics, erasable characteristics and retention characterist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More