Method for preparing chip of high-voltage planar fast-recovery diode

A manufacturing method and diode technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increasing processing cycle and cost, increasing PN junction emission efficiency, deteriorating diode recovery characteristics, etc., achieving processing cycle and Effects of cost simplification, high yield, process cycle and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

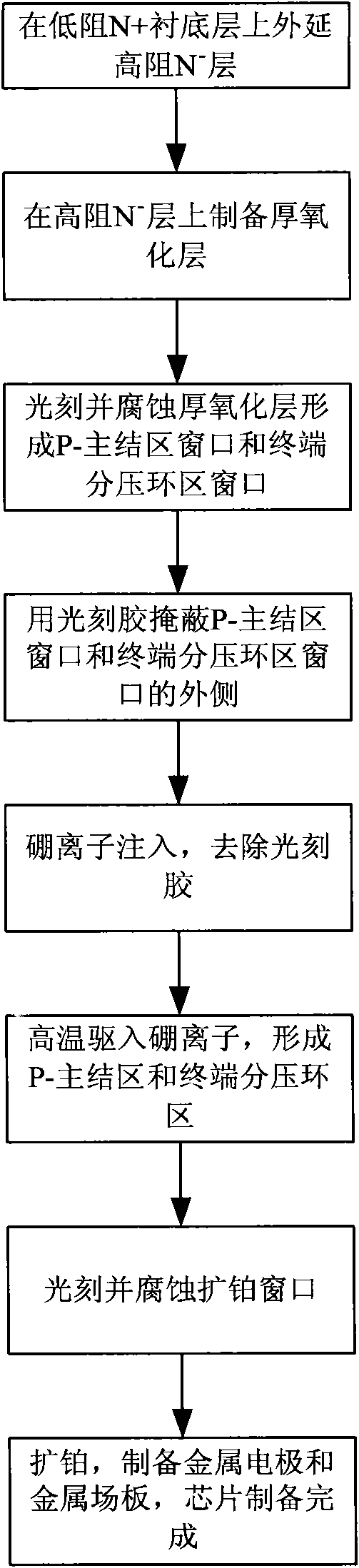

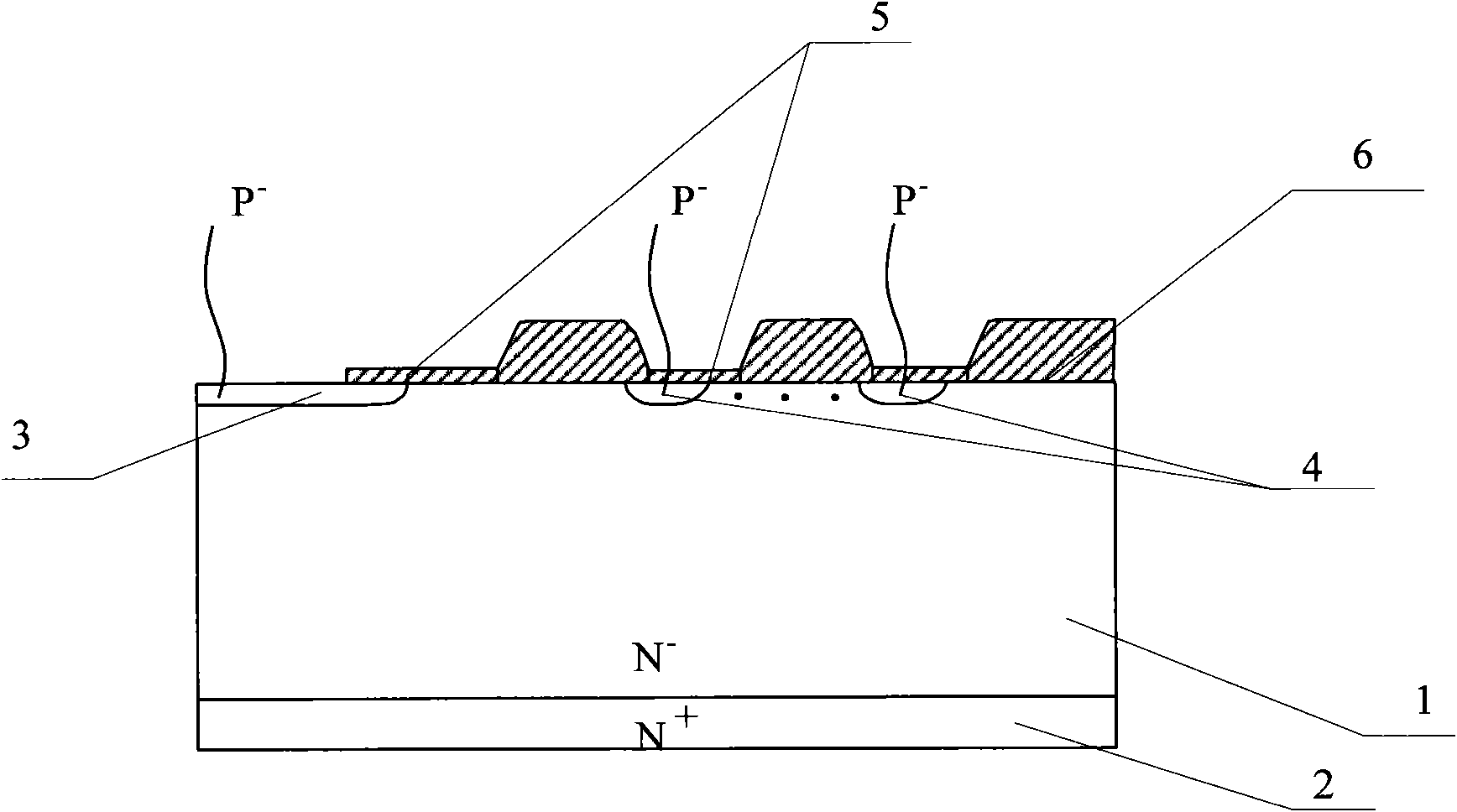

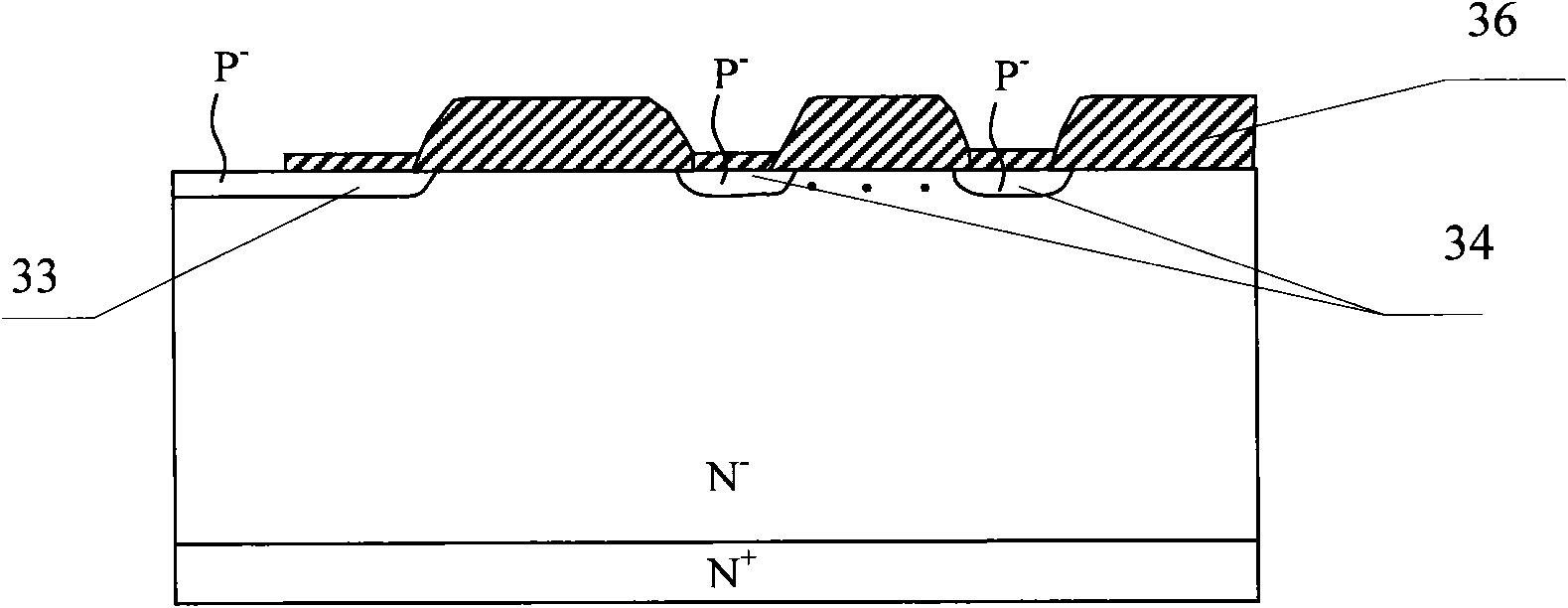

[0047] at low resistance N + Epitaxial preparation of high resistance N on substrate layer 2 - Layer 1, the high resistance N - Prepare a 1 micron thick oxide layer 6 on the layer 1, photolithography and etch the thick oxide layer 6 to form a 2 mm P - Main junction area window and 10 µm termination voltage divider ring area window; mask P with 0.5 µm photoresist - 10 microns outside the window of the main junction area, and 4 microns outside the window of the terminal pressure-dividing ring area; the energy used is 30-100 KeV, and the dose is 1×10 12 cm -2 After boron ion implantation, the photoresist is removed; boron ions are driven in at a high temperature of 1050 degrees to form P - main junction area 3 and terminal voltage divider ring area 4, P - The depth of the main junction region 3 and the terminal voltage divider ring region 4 is 1.5 microns, and the peak doping concentration of the high-concentration region of the PN junction is at 2×10 15 cm -3 , and simult...

Embodiment 2

[0049] at low resistance N + Epitaxial preparation of high resistance N on substrate layer 2 - Layer 1, the high resistance N - Prepare a 1 micron thick oxide layer 6 on the layer 1, photolithography and etch the thick oxide layer 6 to form a 3.5 mm P - Main junction area window and 20 µm termination voltage divider ring area window; mask P with 0.6 µm thick photoresist - 20 microns outside the window of the main junction area and 10 microns outside the window of the terminal pressure dividing ring area; the energy is 30-100KeV, and the dose is 1×10 14 cm -2 After boron ion implantation, the photoresist is removed; boron ions are driven in at a high temperature of 1100 degrees to form P - main junction area 3 and terminal voltage divider ring area 4, P - The depth of the main junction region 3 and the terminal voltage divider ring region 4 is 2 microns, and the peak doping concentration of the high-concentration region of the PN junction is at 1×10 17 cm -3 , and simult...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More