Method for preparing silicon germanium on insulator (SGOI) by layer transfer technology

A technology of multi-layer materials and epitaxial materials is applied in the field of preparing silicon-germanium on insulators, and using layer transfer technology to prepare silicon-germanium-on-insulator materials, which can solve problems such as inability to prepare high-speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

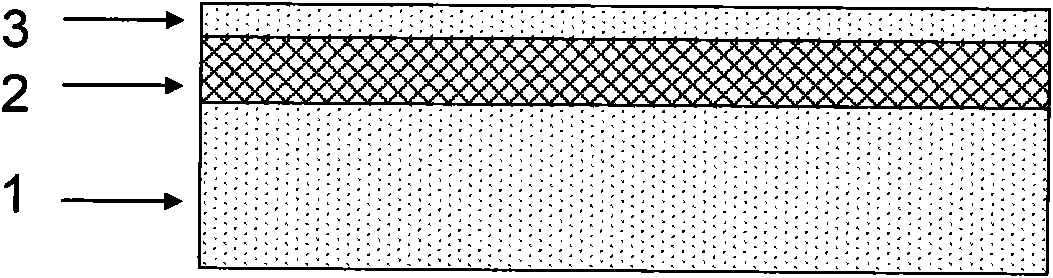

[0017] 1. Sequential epitaxy of Si on bulk silicon substrates using chemical vapor deposition 1-x Ge x 、Si epi For two different films, where 01-x Ge x Thickness of the film, making it less than the critical thickness, while ensuring Si epi thicker than Si 1-x Ge x Thickness (see attached figure 1 ).

[0018] 2. Take a piece of silicon substrate material, prepare SiO on the surface of silicon substrate by thermal oxidation, or plasma enhanced chemical vapor deposition (PECVD), or other methods 2 , SiO 2The thickness is generally 200nm ~ 1um.

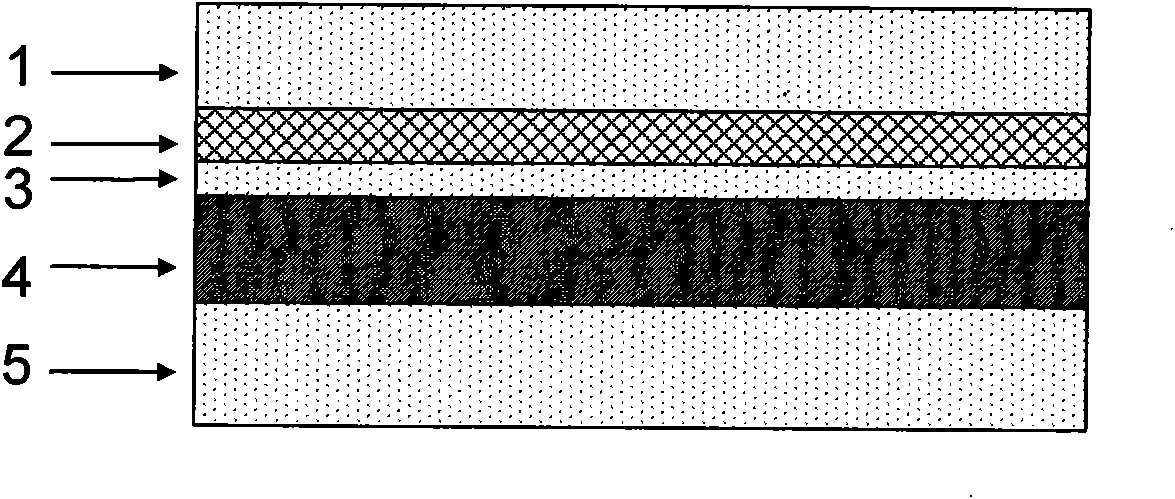

[0019] 3. Bond the material prepared in step 1 with the material prepared in step 2 (see attached figure 2 ).

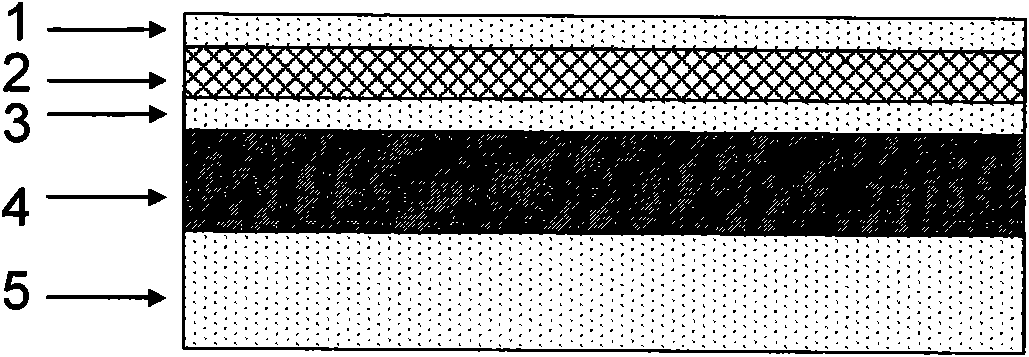

[0020] 4. By grinding, remove the material obtained in step 3 and Si 1-x Ge x Adjacent bulk Si (see attached image 3 ).

[0021] 5. A chemical solution with a high Si: SiGe etching ratio including TMAH (tetramethylammonium hydroxide) or KOH chemical solution is used as a selective etching solution to etch the re...

Embodiment 2

[0025] 1. Sequential epitaxy of Si on bulk silicon substrates using chemical vapor deposition 1-x Ge x 、Si epi Two different films, where 01-x Ge x Thickness of the film, making it less than the critical thickness, while ensuring Si epi thicker than Si 1-x Ge x Thickness (see attached figure 1 ).

[0026] 2. H + or He + Take 5×10 16 cm -2 ~1×10 17 cm -2 dose, select the appropriate energy, and inject it from the upper surface of the material prepared in step 1 into the silicon substrate layer of the epitaxial material close to the Si 1-x Ge x place for the film (see attached Figure 6 ), the preferred recommended dose is 6×10 16 cm -2 , the preferred implanted ion is H + .

[0027] 3. Take a new piece of silicon substrate material, prepare SiO on the surface of the silicon substrate by thermal oxidation, or plasma enhanced chemical vapor deposition (PECVD), or other methods 2 , SiO 2 The thickness is generally 200nm ~ 1um.

[0028] 4. Bond the material pre...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More