Patents

Literature

84results about How to "Improve lattice quality" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Epitaxial growth method and structure for preventing electronic leakage and defect extension

ActiveCN103560190AStop the leakValid entryPolycrystalline material growthFrom chemically reactive gasesOptoelectronicsElectron blocking layer

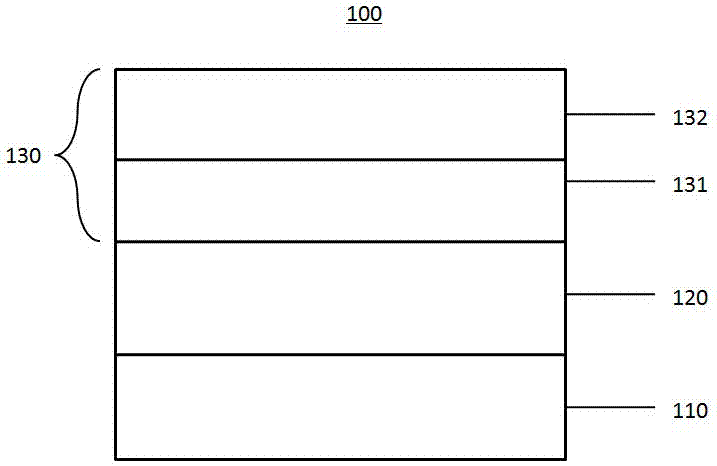

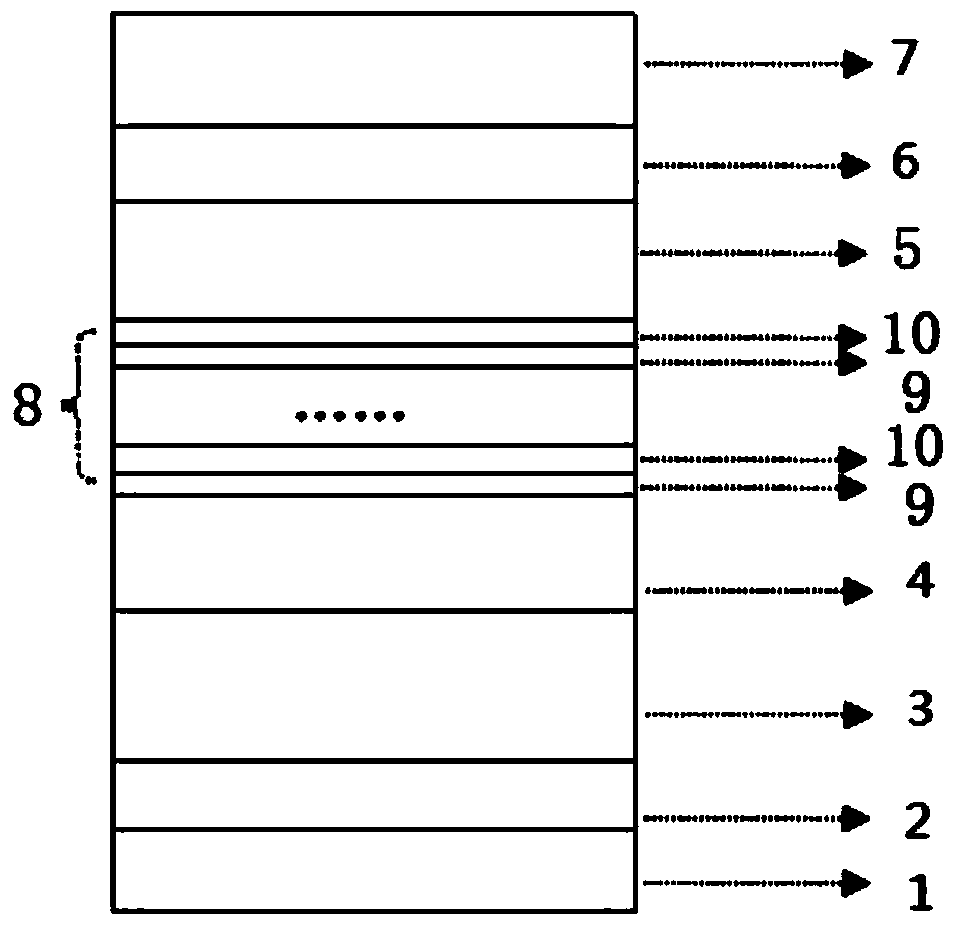

The invention provides an epitaxial growth method for preventing electronic leakage and defect extension. An electronic barrier layer with a thickness of 8-25nm is grown between a grown multiple quantum well InxGa[1-x]N layer and a grown P type GaN layer through NH3, TMGa and TMA1. The electronic barrier layer comprises 2-6 groups of double-layer structures, and the content of Al of a UAlGaN layer of each double-layer structure is 15%-50% less than that of a UAlGaN layer of the previous double-layer structure. According to the epitaxial growth method and structure for preventing electronic leakage and defect extension, the UAlGaN / UGaN structure with Al content reduced layer by layer is adopted to serve as the electronic barrier layer, single energy level height distribution of a traditional P-spacer energy band is changed, the resisting effect on hole injection is weakened, and light emitting efficiency of an MQW is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

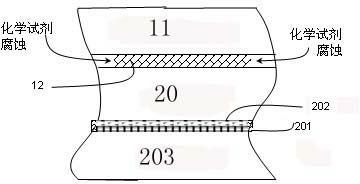

Method for lift-off of light-emitting diode substrate

ActiveUS8507357B2Reduce dislocation densityImprove lattice qualitySemiconductor/solid-state device manufacturingSemiconductor devicesDislocationLight-emitting diode

The present invention discloses a method for lift-off of an LED substrate. By eroding the sidewall of a GaN epitaxial layer, cavity structures are formed, which may act in cooperation with a non-fully filled patterned sapphire substrate from epitaxial growth to cause the GaN epitaxial layer to separate from the sapphire substrate. The method according to an embodiment of the present invention can effectively reduce the dislocation density in the growth of a GaN-based epitaxial layer; improve lattice quality, and realize rapid lift-off of an LED substrate, and has the advantages including low cost, no internal damage to the GaN film, elevated performance of the photoelectric device and improved luminous efficiency.

Owner:QUANZHOU SANAN SEMICON TECH CO LTD

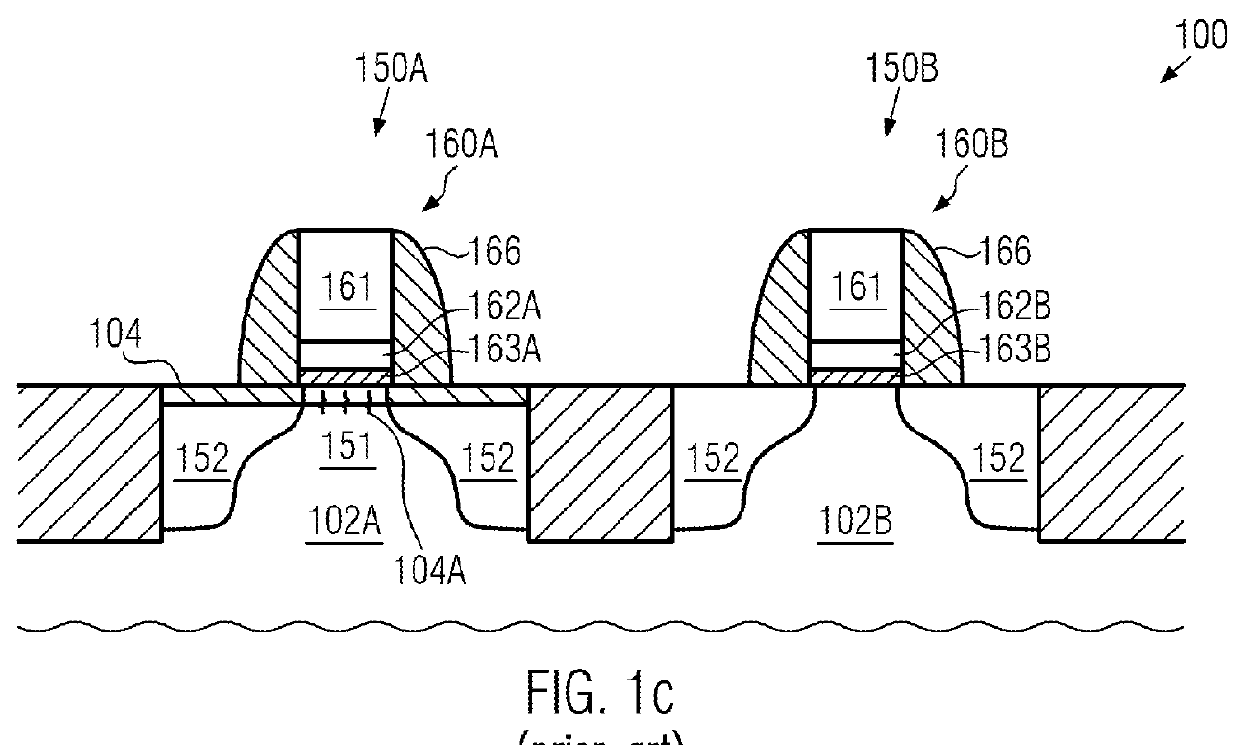

Reduction of Defect Rates in PFET Transistors Comprising a Silicon/Germanium Semiconductor Material by Providing a Graded Germanium Concentration

InactiveUS20120161249A1Reduced lattice mismatchImprove lattice qualityTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor alloys

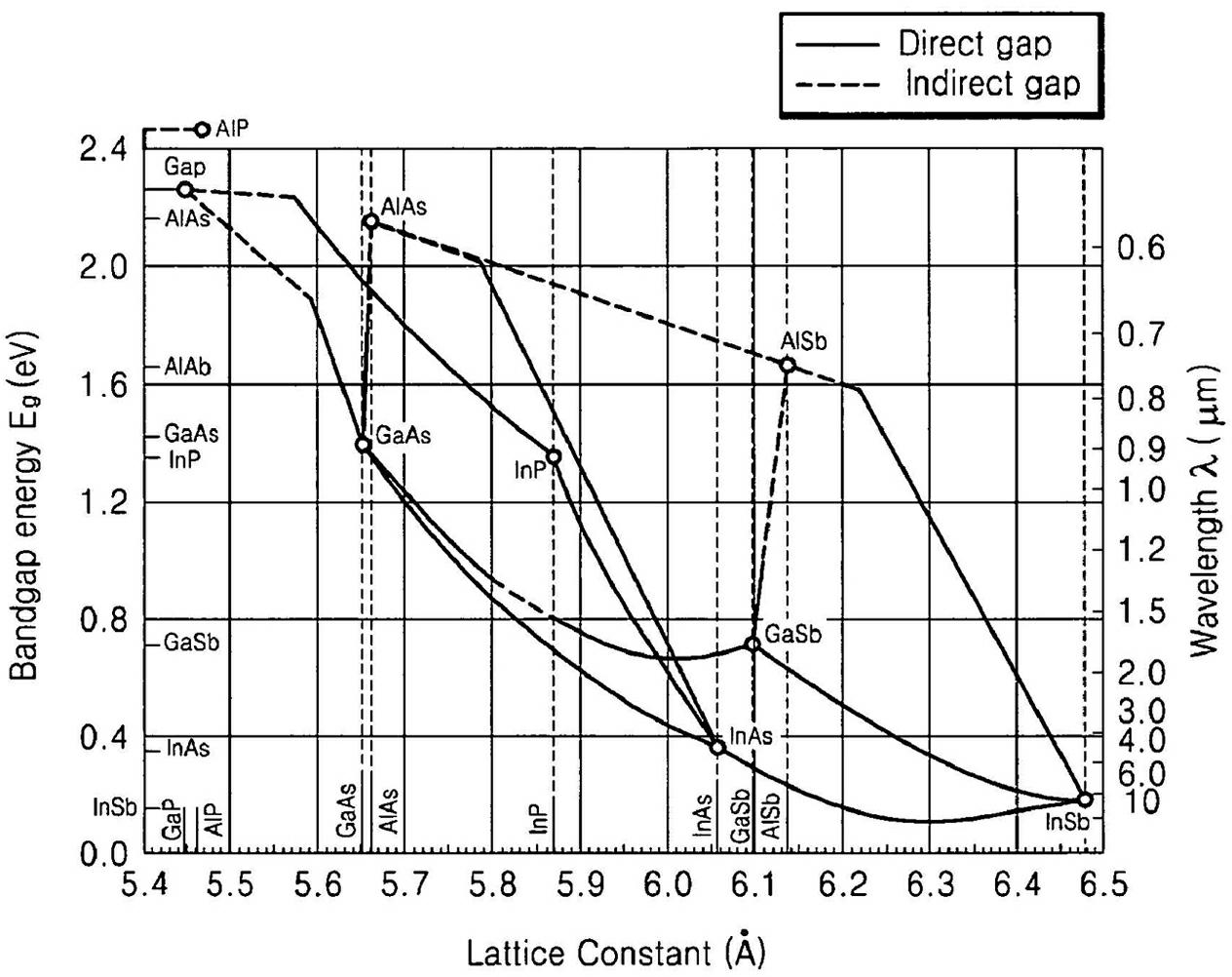

When forming sophisticated gate electrode structures in an early manufacturing stage, the threshold voltage characteristics may be adjusted on the basis of a semiconductor alloy, which may be formed on the basis of low pressure CVD techniques. In order to obtain a desired high band gap offset, for instance with respect to a silicon / germanium alloy, a moderately high germanium concentration may be provided within the semiconductor alloy, wherein, however, at the interface formed with the semiconductor base material, a low germanium concentration may significantly reduce the probability of creating dislocation defects.

Owner:GLOBALFOUNDRIES INC

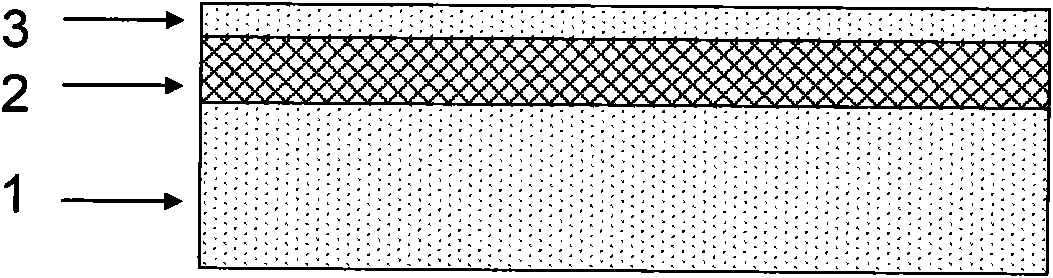

Method for preparing silicon germanium on insulator (SGOI) by layer transfer technology

InactiveCN101866874AHigh bonding strengthImprove lattice qualitySemiconductor/solid-state device manufacturingDislocationGermanium

The invention relates to a method for preparing silicon germanium on insulator (SGOI) by the layer transfer technology, comprising the following steps: extending multiple layers of materials which are in the structure of Siepi / Si1-xGex on silicon, wherein the x is more than 0 and less than 1, and the Siepi is the upper surface of the extended material; controlling the thickness of the extended thin film which is in the structure of Si1-xGex to be less than the critical thickness so as to ensure that the extended thin film is fully strained; transferring the multiple layers of materials which are in the structure of Siepi / Si1-xGex to support materials which are in the structure of SiO2 / Si by the layer transfer method to form multiple layers of materials which are in the structure of Si1-xGex / Siepi / SiO2 / Si; and annealing to enable the layer of material which is in the structure of Si1-xGex to be relaxed wherein the dislocation generated in the annealing process is mainly distributed in the layer of material which is in the structure of Siepi, so that the layer of material which is in the structure of Si1-xGex keeps high lattice quality; and continuously extending a layer of thin film which is in the structure of Si on the layer of material which is in the structure of Si1-xGex by a extending method, and keeping the layer of thin film which is in the structure of Si stressed to obtain the SGOI which is in the structure of Si / Si1-xGex / Siepi / SiO2 / Si.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

Substrate material for mercury cadmium telluride material growth by liquid phase epitaxy method and preparation thereof

InactiveCN101348941AImprove lattice qualityQuality improvementPolycrystalline material growthLiquid-phase epitaxial-layer growthMaterial growthProcess equipment

The invention relates to a substrate material used for the growth of a mercury cadmium telluride material by a liquid phase epitaxy method. On the basis of the prior substrate material, a layer of cadmium zinc telluride single-crystal film completely matched with the lattice constant of mercury cadmium telluride is grown. The substrate material of the invention has the advantages that an epitaxial film has high lattice quality, and compositions can be flexibly adjusted according to the lattice constants of short wave, medium wave and long wave mercury cadmium telluride materials; meanwhile, the cadmium zinc telluride film has even compositions; the method adopts mature process, and has the advantages of simpler process equipment, short process cycle and low cost; and the substrate material with large area, high quality and high composition evenness can be provided for an infrared focal plane detector.

Owner:11TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

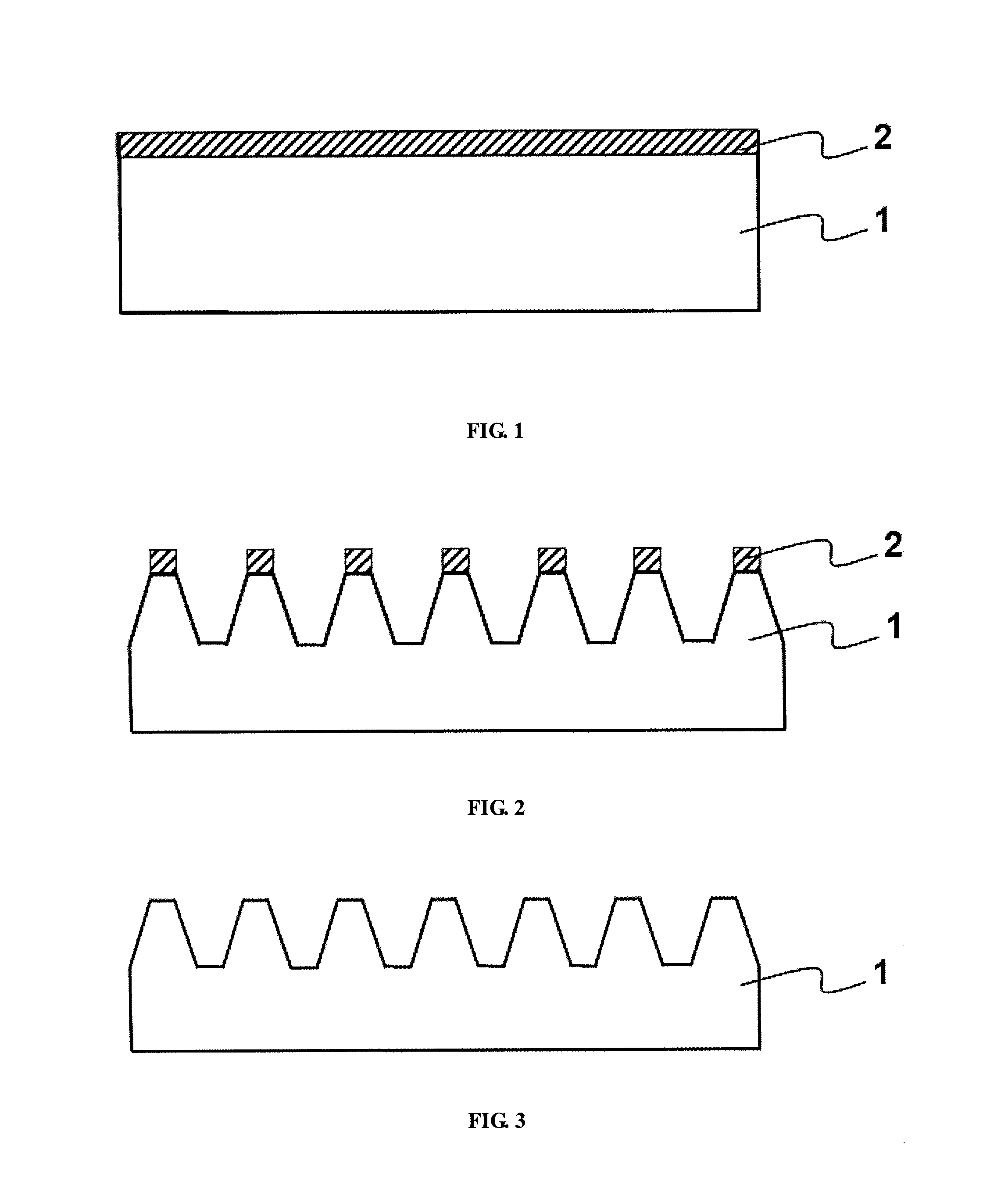

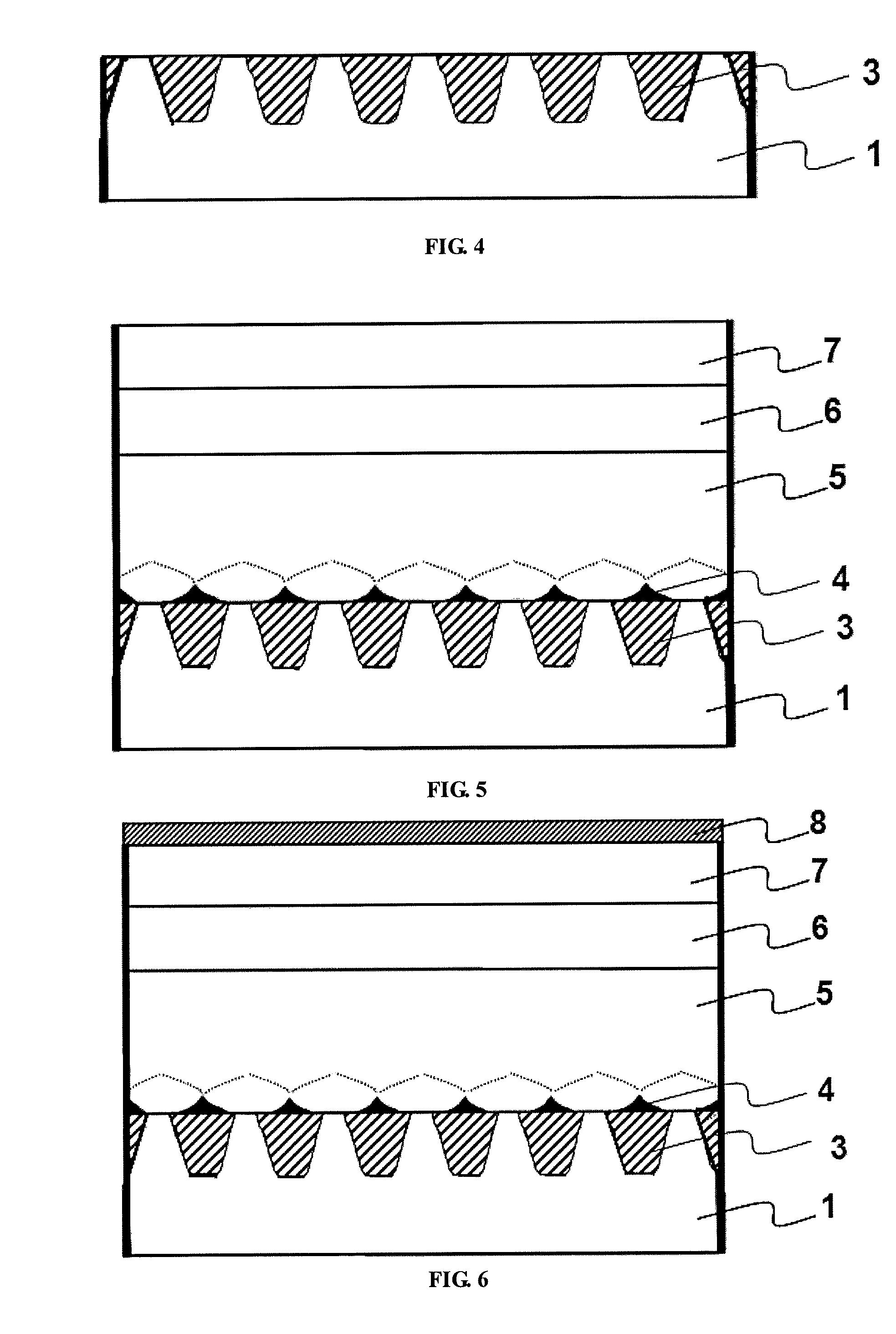

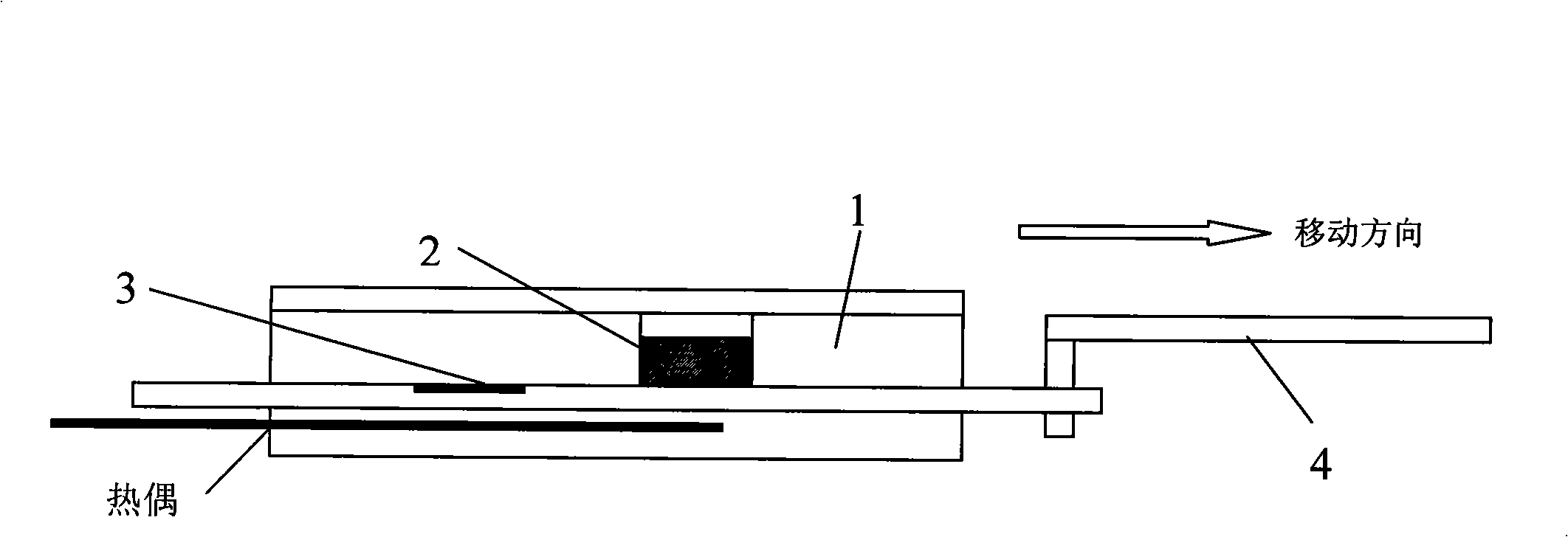

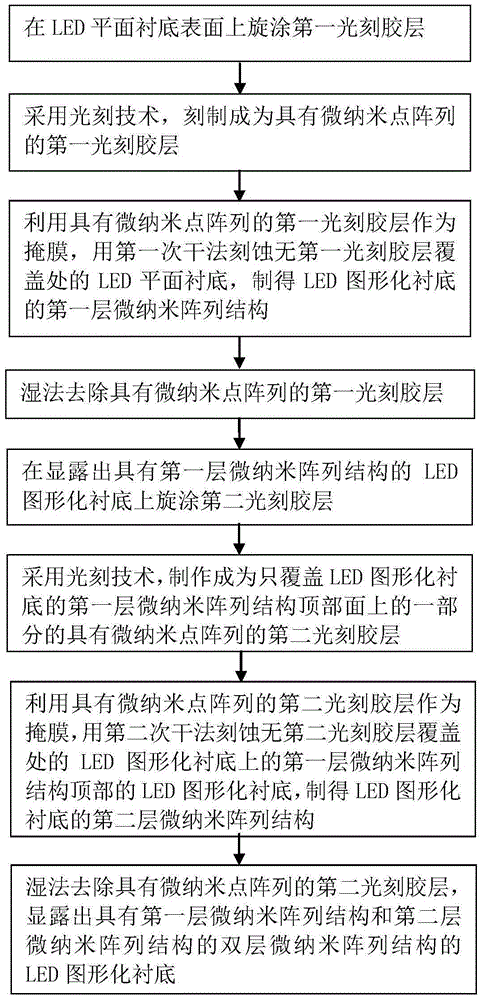

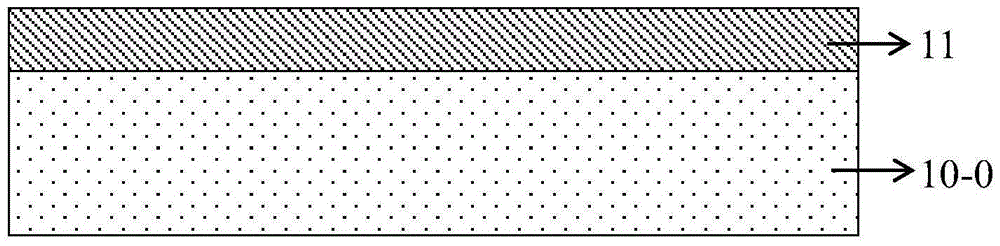

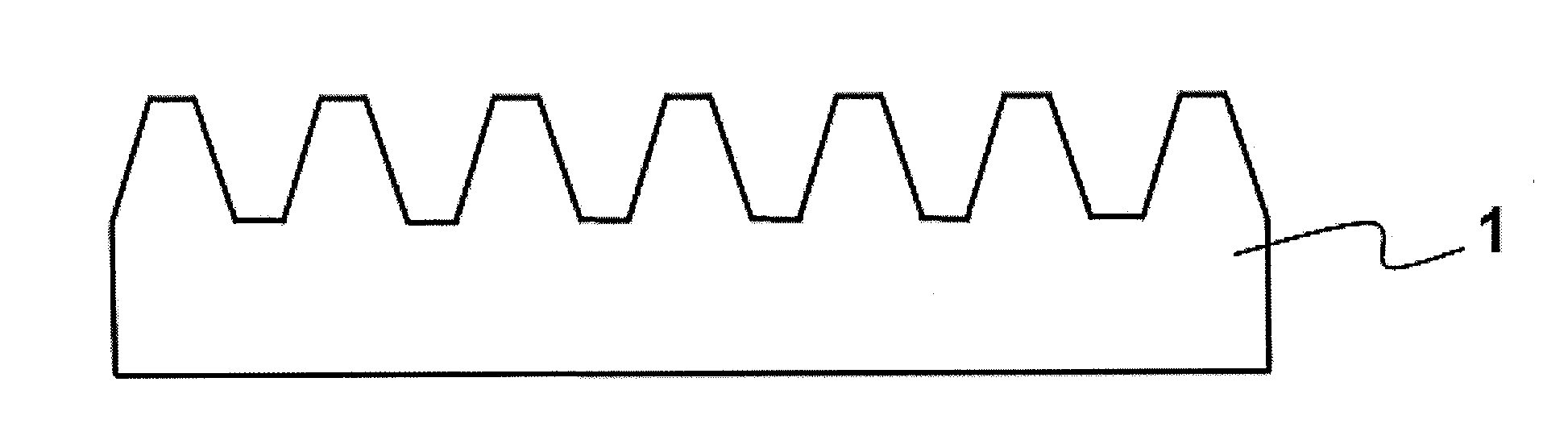

Manufacturing method for LED patterned substrate with double-layer micro-nano array structure

ActiveCN105226144AImprove lattice qualityImprove light extraction efficiencySemiconductor devicesMicro nanoOptoelectronics

The invention discloses a manufacturing method for an LED patterned substrate with a double-layer micro-nano array structure, and relates to a semiconductor device. The manufacturing method comprises the following steps: performing spin-coating to obtain a first photoresist layer; manufacturing a first photoresist layer with a micro-nano spot array; performing primary dry etching; removing the first photoresist layer with the micro-nano spot array by using a wet method; performing spin-coating to obtain a second photoresist layer; manufacturing a second photoresist layer with a micro-nano spot array; performing secondary dry etching; and removing the second photoresist layer with the micro-nano spot array by using the wet method, thus manufacturing the LED patterned substrate with the double-layer micro-nano array structure. According to the method disclosed by the invention, due to the design of the first layer of micro-nano structure, the crystal lattice quality of GaN is improved; due to the design of the second layer of micro-nano structure, the light extraction efficiency of an LED is improved; the defect that the improvement on the crystal lattice quality of GaN and the maximum improvement on the light extraction efficiency of the LED can not be compatible in the prior art is overcome.

Owner:HEBEI UNIV OF TECH

Multiple quantum well structure and light-emitting diode thereof

ActiveCN107086258ARate of blocking migrationAlleviate lattice differencesSemiconductor devicesHigh current densityPotential well

The invention relates to the field of semiconductor technologies, in particular to a multiple quantum well structure and a light-emitting diode thereof. The multiple quantum well structure comprises a stress release layer, an electron collecting layer and a light emitting layer, wherein the light emitting layer comprises a plurality of potential barrier layers and potential well layers which grow alternately, at least one potential barrier layer is of a GaN / AlxInyGa(1 x y)N / GaN structure, 0<x<=1, 0<=y<1, and the rest potential barrier layers are of a GaN structure. The light-emitting diode at least comprises a substrate, and a buffer layer, an N-type layer, a multiple quantum well structure layer, an electron blocking layer, a P-type layer and a P-type contact layer which are arranged on the substrate sequentially. According to the multiple quantum well structure and the light-emitting diode thereof, the potential barrier layers with a forbidden bandwidth higher than the GaN are arranged in layers of the multiple quantum well structure, namely, an electron blocking layer in the existing structure is dispersed in the multiple quantum well structure layer, thereby achieving the effect of blocking electrons in a dispersed manner, enhancing the electronic blocking effect, reducing the electron overflow phenomenon at high current density and the resulting Droop effect, and improving light-emitting efficiency of the light-emitting diode.

Owner:ANHUI SANAN OPTOELECTRONICS CO LTD

High-efficient four solar cell and manufacturing method thereof

InactiveCN102412337AImprove lattice qualityBroaden the spectral absorption rangeFinal product manufacturePhotovoltaic energy generationContact layerSolar cell

The invention discloses a high-efficient four solar cell and a manufacturing method thereof. The method is characterized by: providing a double-sided polishing substrate, which is used for growing an extension of a semiconductor; forming a first sub-cell on a front side of the substrate so that the first sub-cell possesses a first band gap; forming a gradient buffer layer above the first sub-cell so that the gradient buffer layer possesses a second band gap which is greater than the first band gap; forming a second sub-cell above the gradient buffer layer so that the second sub-cell possesses a third band gap which is greater than the second band gap; forming a high doping cap layer above the second sub-cell; forming a third sub-cell on a back side of the substrate, wherein the third sub-cell grows at an inversed direction and possesses a fourth band gap which is less than the first band gap; forming a fourth sub-cell under the third sub-cell, wherein the fourth sub-cell grows at an inversed direction and possesses a fifth band gap which is less than the fourth band gap; extending to form a back contact layer under the fourth sub-cell and acquiring the needed solar cell. By using the method of the invention, the high-efficient four solar cell with current matching and a wide spectrum absorption scope can be manufactured.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

Substrate and manufacturing method thereof

ActiveCN106611739AReduce the number of defectsQuality improvementSemiconductor/solid-state device manufacturingChemical-mechanical planarizationOptoelectronics

The invention provides a substrate and a manufacturing method thereof. The method comprises steps: an auxiliary substrate and a supporting substrate are provided, wherein at least a defect elimination structure, an epitaxial layer above the defect elimination structure and a passivation layer above the epitaxial layer are arranged on the auxiliary substrate, and at least a buried dielectric layer is arranged on the supporting substrate; the auxiliary substrate is bonded on the supporting substrate; the auxiliary substrate is removed; and chemical-mechanical planarization (CMP) is carried out until the epitaxial layer reaches a specified thickness. As defects of the epitaxial layer can be reduced by the defect elimination structure and damages of the epitaxial layer during the bonding process can be effectively reduced by the passivation layer, a large amount of defects can be prevented from being generated in the epitaxial layer, and the performance and the reliability of using the epitaxial layer to manufacture a device can be enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

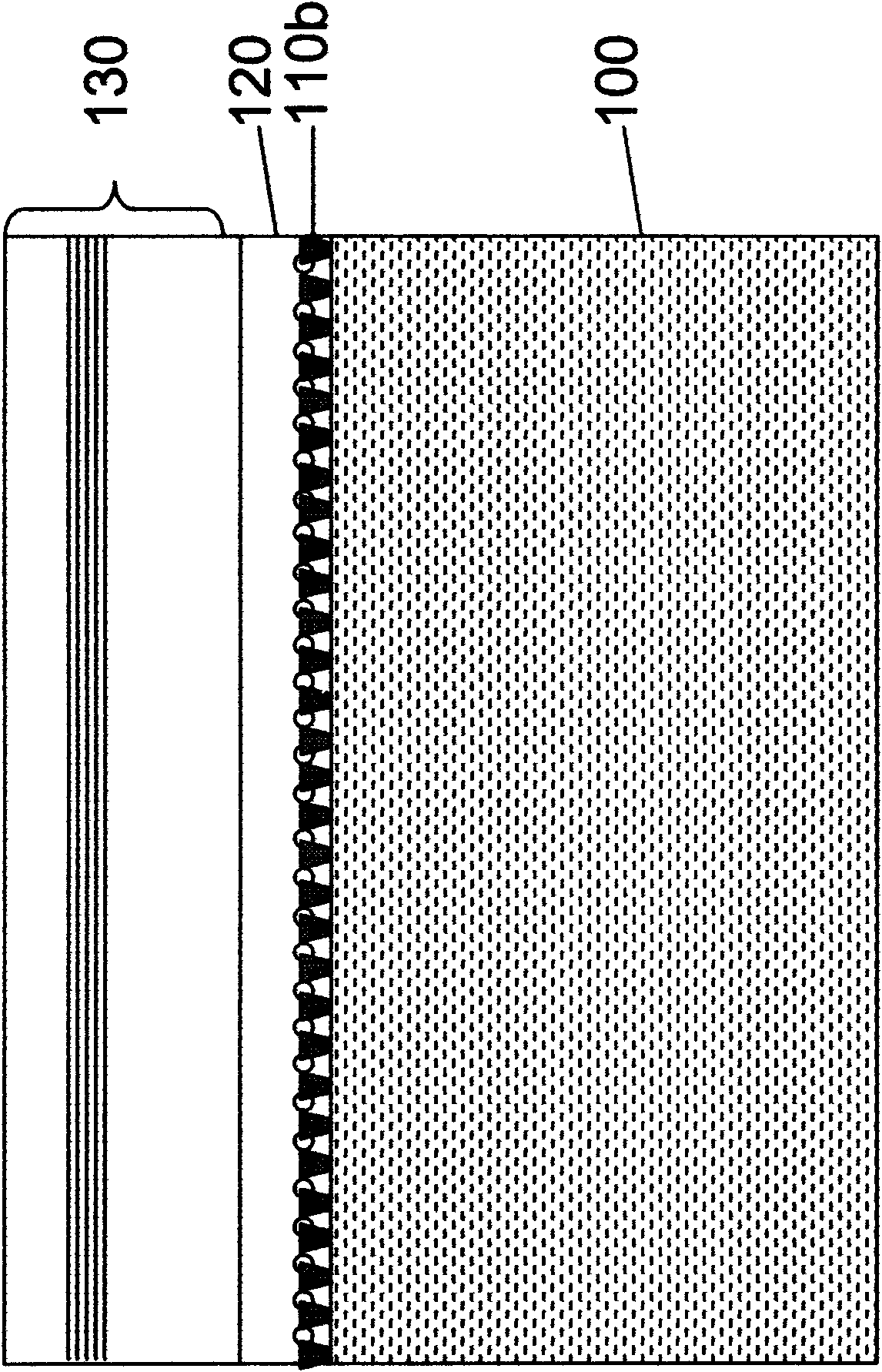

Epitaxial structure of LED (light-emitting diode) with GaN (gallium nitride)-based vertical structure and manufacturing method thereof

InactiveCN102214748AImprove light extraction efficiencySolve congestionSemiconductor devicesCharge carrierQuantum well

The invention relates to an epitaxial structure of an LED (light-emitting diode) with a GaN (gallium nitride)-based vertical structure and a manufacturing method thereof. The manufacturing method adopts the following technical scheme which at least comprises the following steps: (1) manufacturing a ZnO buffer layer on an epitaxial growth substrate; (2) using MOCVD (metal-organic chemical vapor deposition) equipment to grow an extrinsic doped GaN buffer layer on the ZnO buffer layer substrate; (3) continuing to grow a high-temperature N-type Si-doped GaN layer, a periodical multilayer luminous zone-quantum well, an electronic barrier layer and a P-type Mg-doped GaN layer in the MOCVD equipment; and (4) carrying out charge carrier exciton on the Mg doped in the P-type GaN layer. The invention has the following advantages: a complicated ultraviolet laser peeling process and dear ultraviolet laser peeling equipment are not used when the substrate is peeled; in the manufacturing method, a damage-free mechanical-separation-free substrate peeling technology is adopted; the equipment is low in requirements; and the epitaxial wafers can be processed in batch.

Owner:云峰

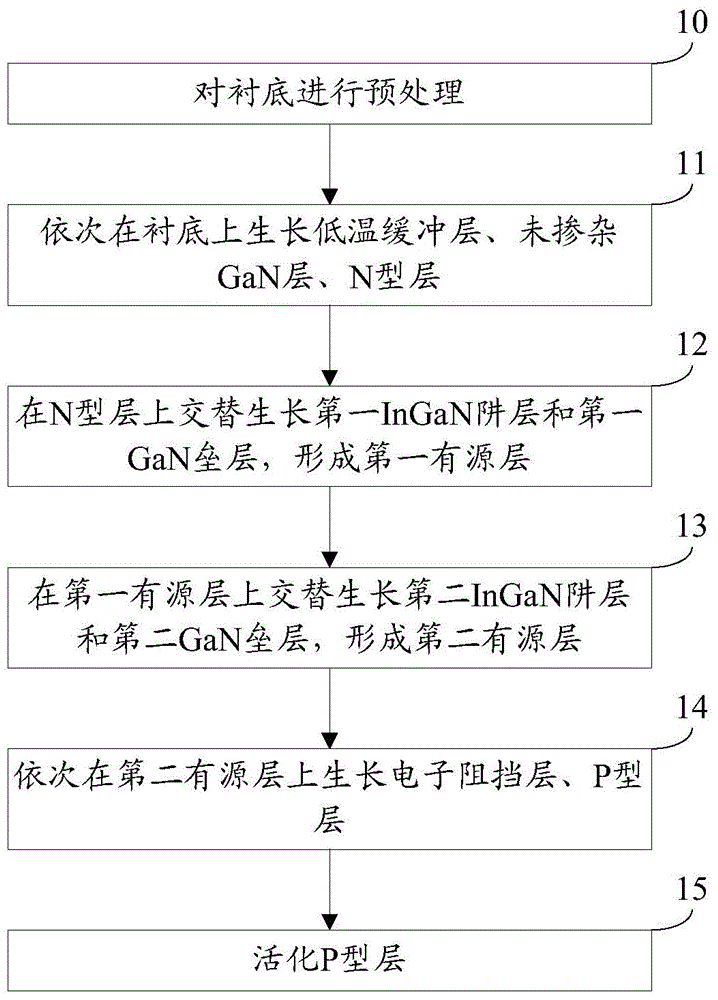

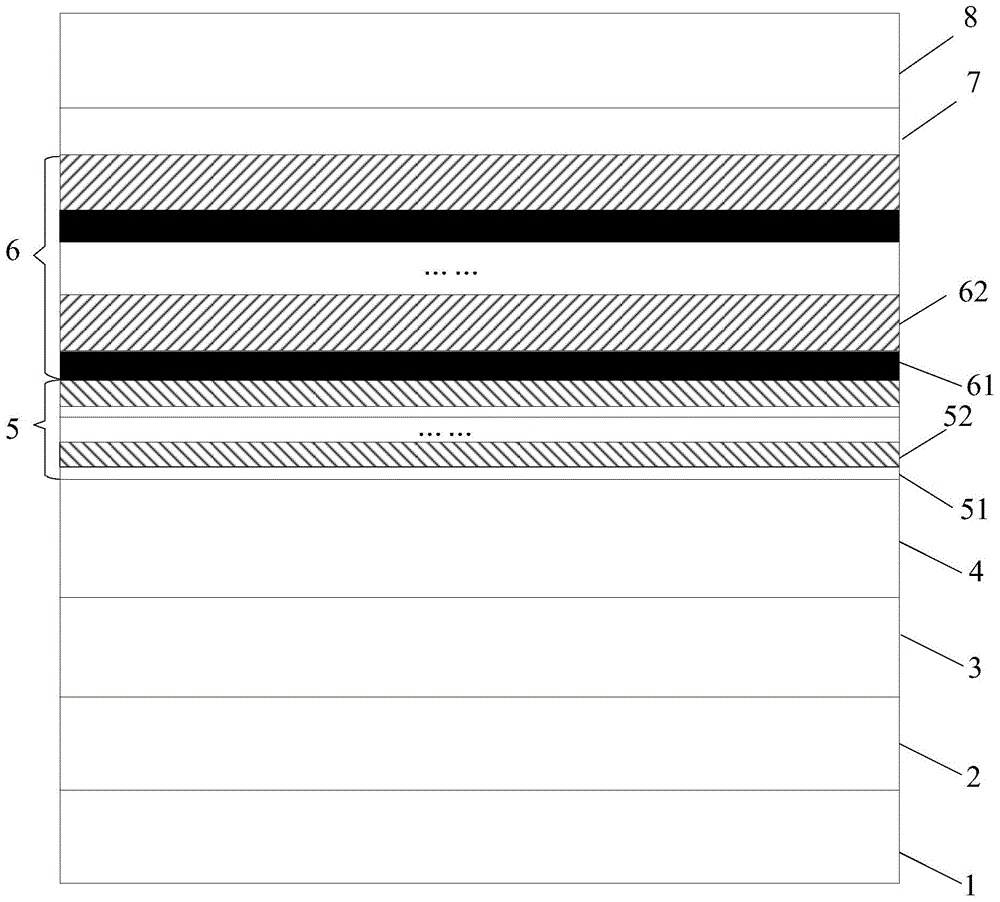

Growth method for light-emitting diode epitaxial wafer and epitaxial wafer

The invention discloses a growth method for a light-emitting diode epitaxial wafer and an epitaxial wafer, belonging to the technical field of a semiconductor. The growth method comprises the following steps of: sequentially growing a low-temperature buffer layer, a non-doped GaN layer and an N-type layer on a substrate; alternatively growing a first InGaN pit layer and a first GaN barrier layer on the N-type layer to form a first active layer; alternatively growing a second InGaN pit layer and a second GaN barrier layer on the first active layer to form a second active layer; and sequentially growing an electron blocking layer and a P-type layer on the second active layer, wherein the growth pressure of the second active layer is lower than the growth pressure of the first active layer, the growth speed of the second active layer is lower than the growth speed of the first active layer, the thickness of the second active layer is smaller than the thickness of the first active layer, and the growth pressure, the growth speed and the thickness of the second InGaN pit layer are gradually reduced, slowed and decreased along the growth direction of the light-emitting diode epitaxial wafer. The epitaxial wafer is high in luminous efficiency.

Owner:HC SEMITEK SUZHOU

Manufacturing method of light emitting diode (LED) based on inversed roughened surface Gan-base vertical structure

ActiveCN101661984AReduce dislocation densityImprove lattice qualitySemiconductor devicesNon dopedAnisotropic etching

The invention discloses a manufacturing method of an LED based on an inversed roughened surface Gan-base vertical structure, which comprises the following steps: growing a non-doped GaN material layeron a spphire substrate by adopting an MOCVD method; and continuously growing an LED extension illuminating material layer after carrying out anisotropic etching on the non-doped GaN material layer. After etching, the bottom surface of the non-doped GaN material layer and spphire form a discontinuous bonding interface, on the one hand, the LED extension stress of the release part improves the quality of an LED extension crystal lattice and improves the internal quanntum efficiency; and on the other hand, after the spphire substrate is removed, the discontinuous bonding interface naturally inverses into a roughened light emergent surface and improves the light collection efficiency of LED devices, therefore, the LED with GaN-based vertical structure has higher illuminating efficiency and isparticularly suitable for heavy current drive.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

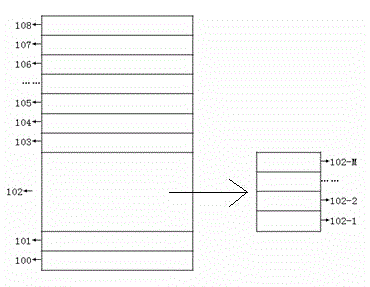

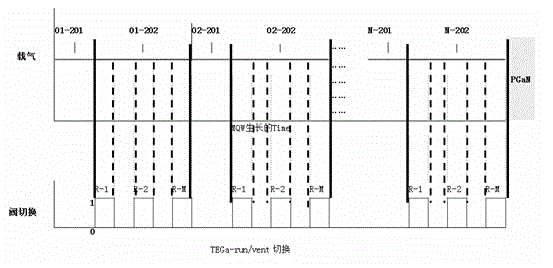

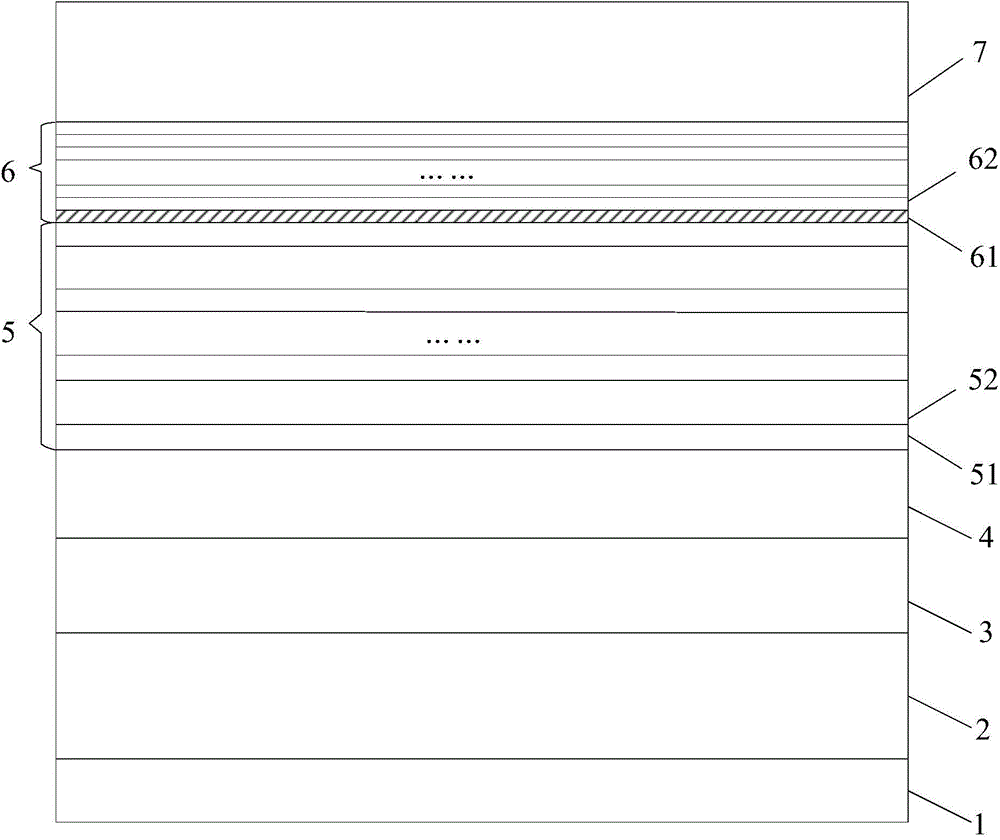

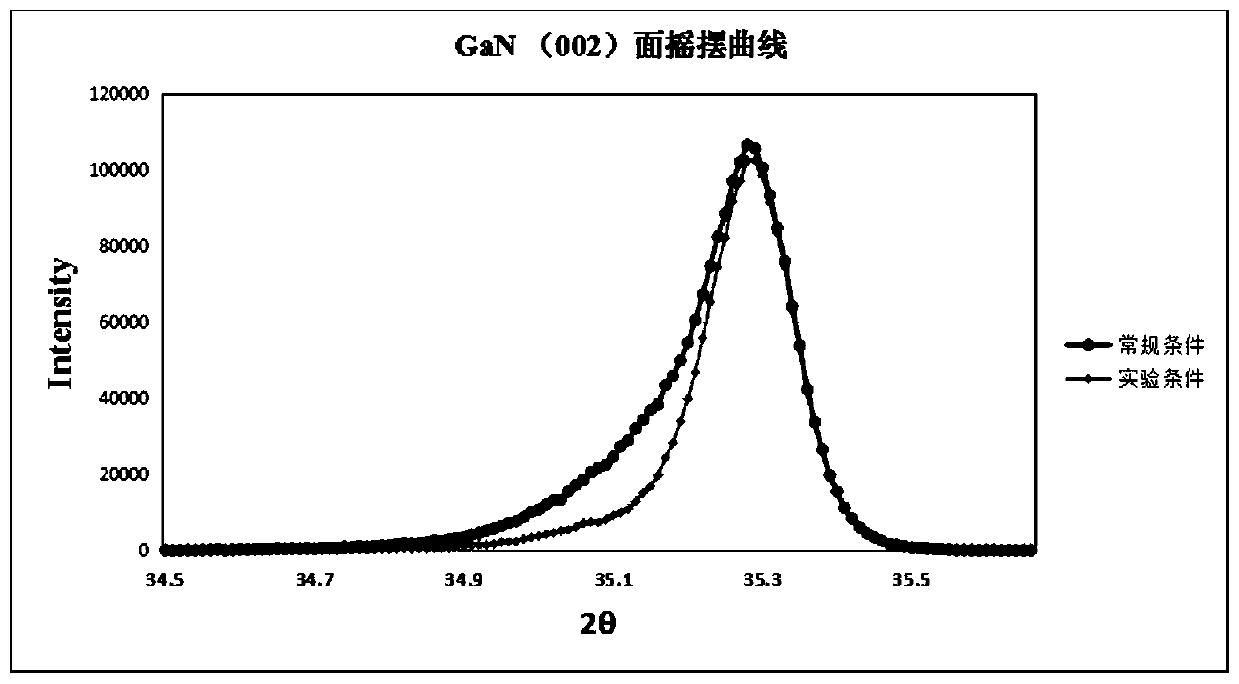

Intermittent-annealing isothermal-growth multi-quantum well LED extension structure and manufacturing method thereof

InactiveCN104319321AUniform crystal plane orientationImprove lattice qualitySemiconductor devicesHydrogen atmosphereCrystal orientation

The invention discloses a manufacturing method of an intermittent-annealing isothermal-growth multi-quantum well LED (light-emitting diode) extension structure, and the manufacturing method comprises the following steps of: preparing a substrate, and treating it at high temperature under hydrogen atmosphere; successively growing a buffer layer and a n-GaN layer on the treated substrate surface; periodically growing a MQW (multiple quantum well) active layer on the n-GaN layer; successively growing a p-GaN contact layer and a P-type contact layer on the MQW active layer; the MQW active layer is composed of at least two MQW layers, each MQW layer includes an InGaN MQW layer, a GaN protection layer and a GaN quantum barrier layer, and each MQW layer is grown at the same temperature. In the manufacturing method, through intermediate intermittent annealing, the extension structure has more uniform crystal orientation and higher crystal lattice quality; through the method, a high-quality MQW structure layer can be manufactured, the luminous efficiency is improved by more than 10%, much original heating and cooling time is saved in the MQW and the capacity is also obviously increased. The surface of low-temperature GaN material is smoothed to achieve uniform two-dimensional growth of the barrier so as to obtain a high-quality MQW material.

Owner:SUZHOU NANOJOIN PHOTONICS

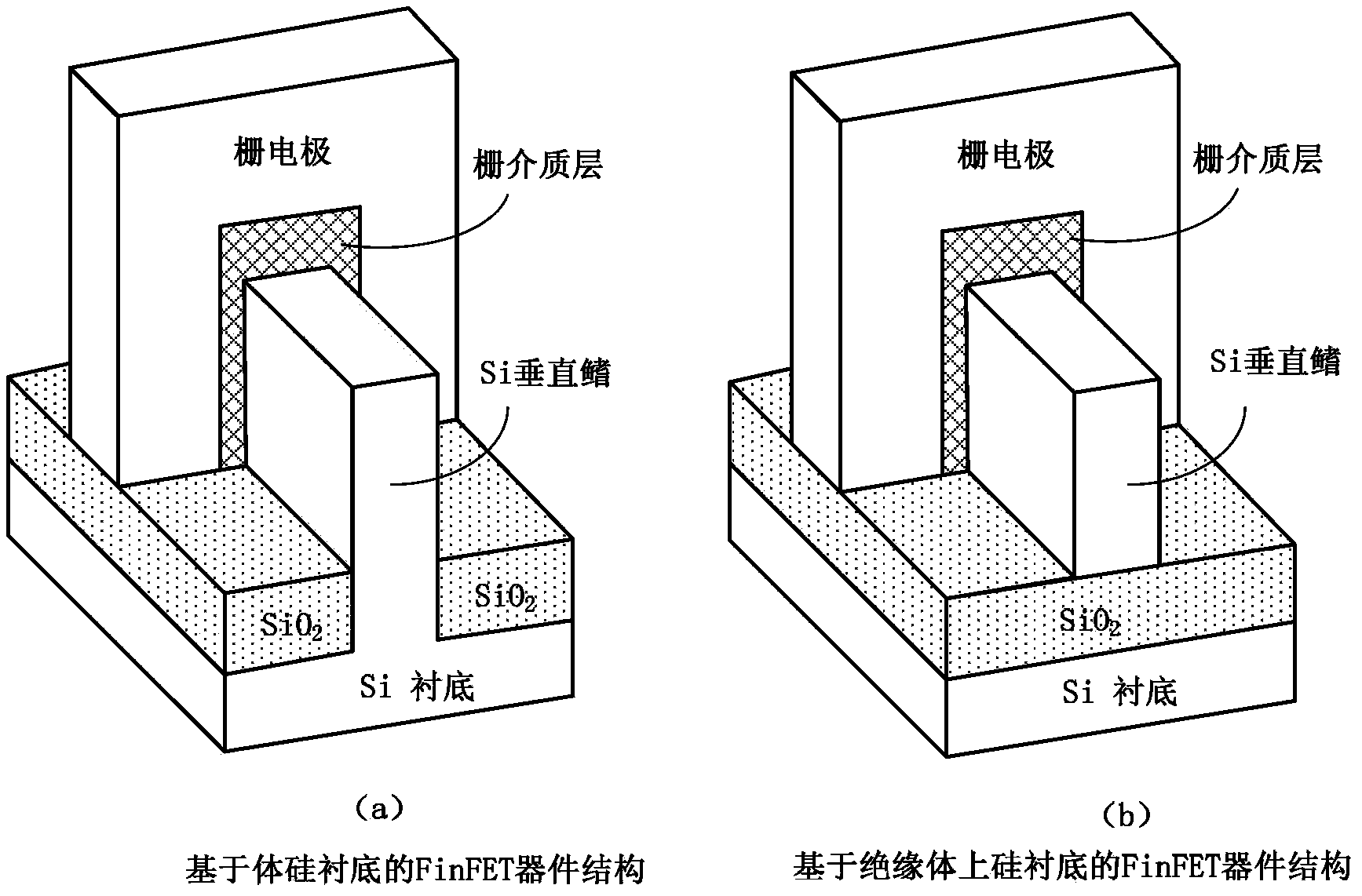

Method for improving performance of fin field-effect transistor

InactiveCN106952806AImprove protectionWeak diffusion barrierSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerEngineering

A method for improving performance of a fin field-effect transistor comprises the steps of providing a substrate, wherein discrete fin parts are formed on a surface of the substrate, an isolation layer is also formed on the surface of the substrate and covers surfaces of a part of side walls of the fin parts, and the top of the isolation layer is lower than the tops of the fin parts; forming a gate structure bridging the fin parts on a surface of the isolation layer, wherein the gate structure covers the surfaces of a part of tops and the side walls of the fin parts; forming an amorphous material layer covering the surfaces of a part of tops and the side walls of the fin parts and the surface of the isolation layer; forming an oxide doping layer on a surface of the amorphous material layer; annealing the oxide doping layer so that doping ions are diffused and enter the fin parts, and forming doping regions in the fin parts at two sides of the gate structure; and removing the oxide doping layer. During the process of removing the oxide doping layer, the amorphous material layer has a protection effect on the isolation layer, the etching loss caused by the technology of removing the oxide doping layer on the isolation layer is prevented, so that the thickness of the isolation layer is maintained unchanged, and the electrical property of the formed fin field-effect transistor is further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

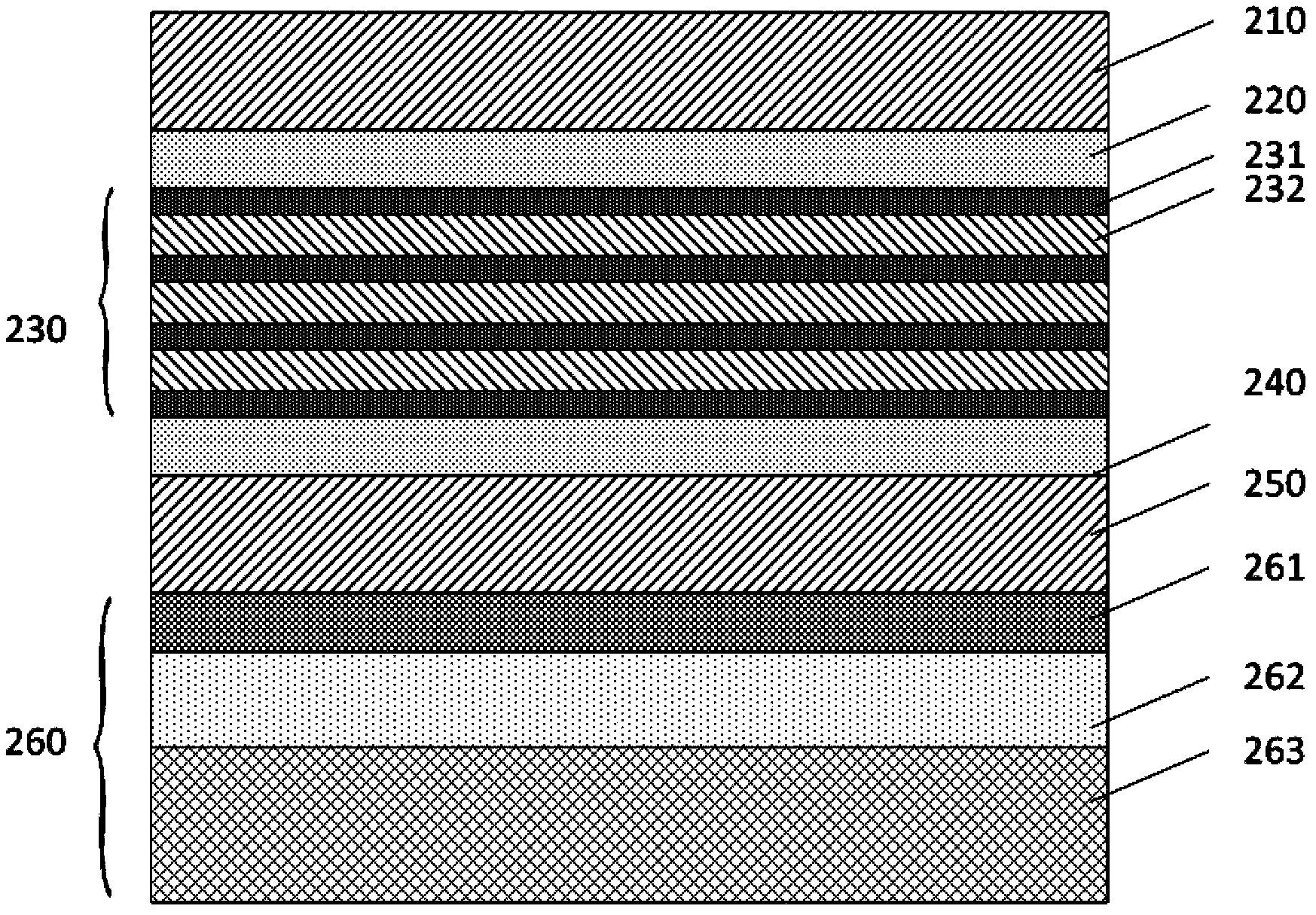

Efficient triple-junction solar cell and manufacturing method thereof

InactiveCN103258872AHigh mechanical strengthImprove lattice qualityPhotovoltaic energy generationSemiconductor devicesEngineeringSolar battery

The invention discloses an efficient triple-junction solar cell and a manufacturing method thereof. The efficient triple-junction solar cell comprises a growth substrate, a bottom cell, an intermediate cell and a top cell, wherein the growth substrate is provided with two polished surfaces; the bottom cell is formed by a strain compensation superlattice structure, grows on the reverse side of the growth substrate in an inverted mode, and is provided with a first band gap, and the equivalent lattice constant of the bottom cell is matched with that of the growth substrate; the intermediate cell is formed on the obverse side of the growth substrate and is provided with a second band gap larger than the first band gap, and the lattice constant of the intermediate cell is matched with that of the growth substrate; the top cell is formed on the intermediate cell and provided with a third bang gap larger than the second band gap, and the lattice constant of the top cell is matched with that of the intermediate cell. Distribution of energy band gaps of the triple-junction solar cell meets an optimal choice for capturing a solar energy spectrum, and current matching and lattice matching are achieved, so photoelectric conversion efficiency of the triple-junction solar cell is effectively improved; according to the manufacturing method of the triple-junction solar cell, a mode of double-faced growth on the growth substrate is adopted, so growth cockamamie processes brought in the later stage of inverted growth are eliminated, and the yield of products is improved.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

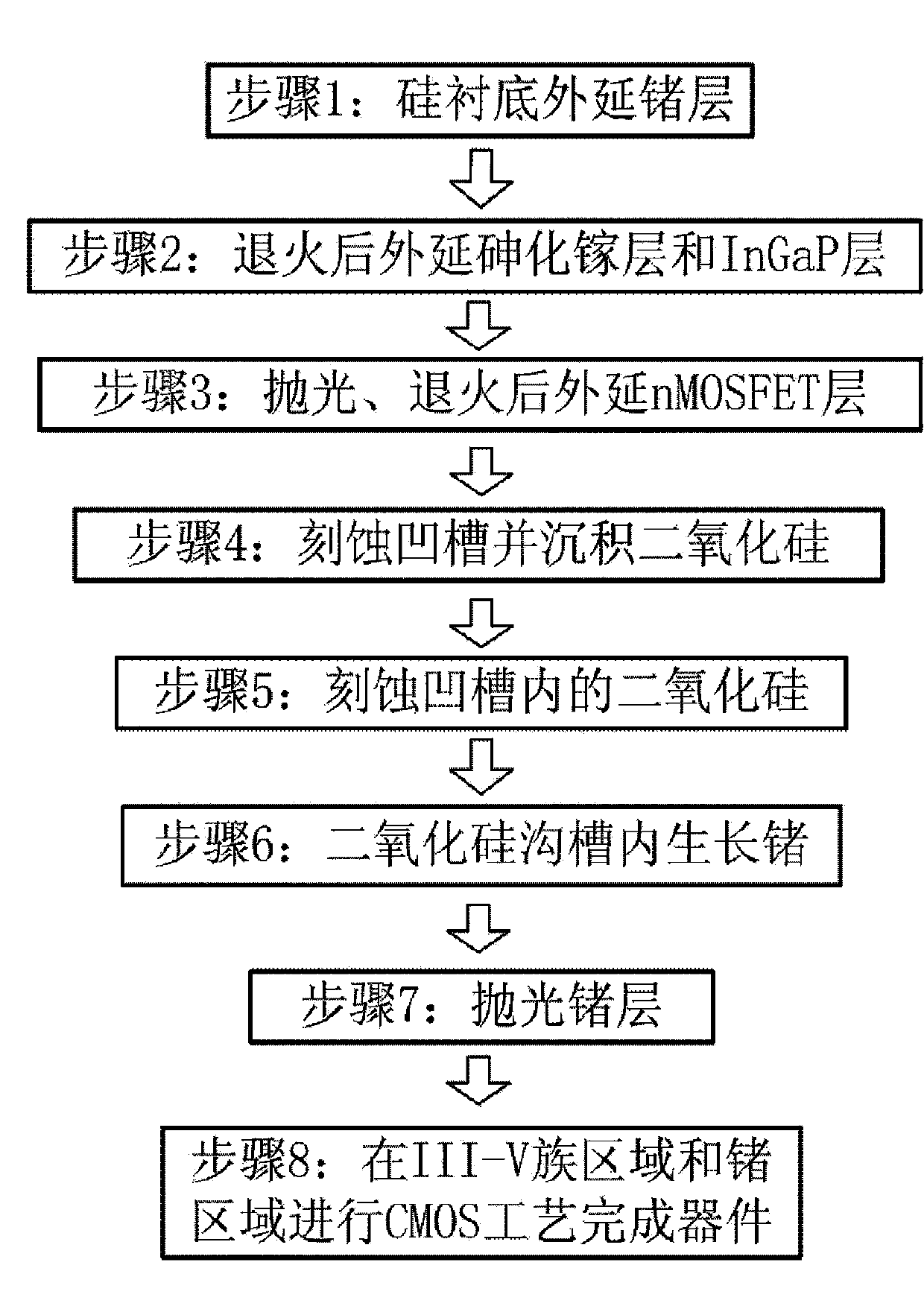

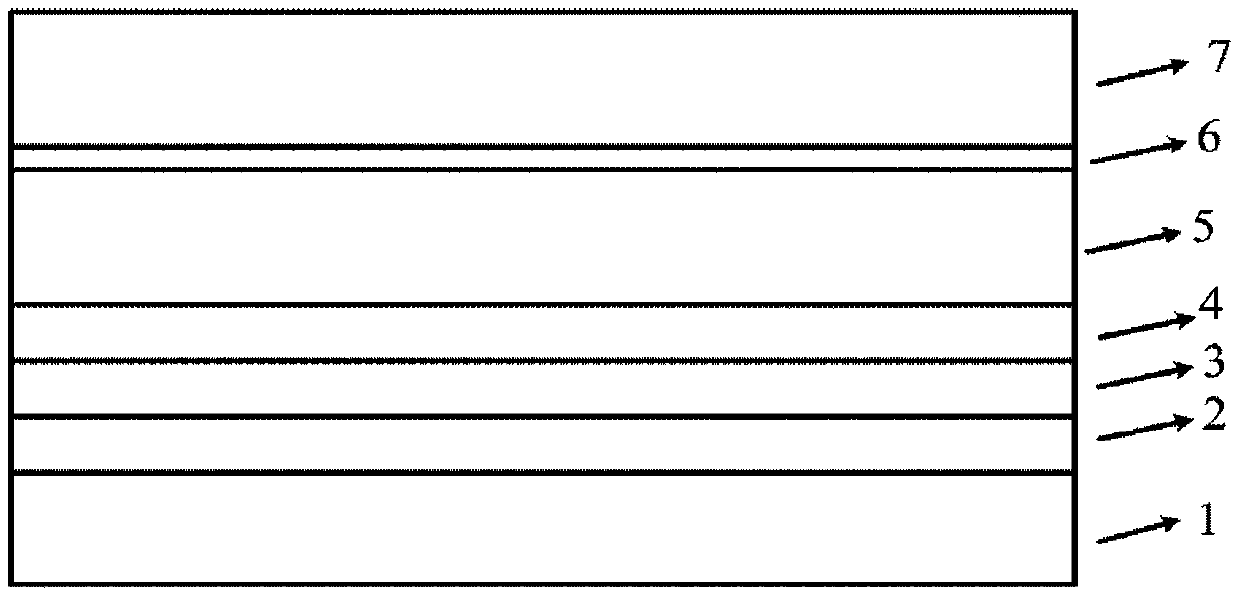

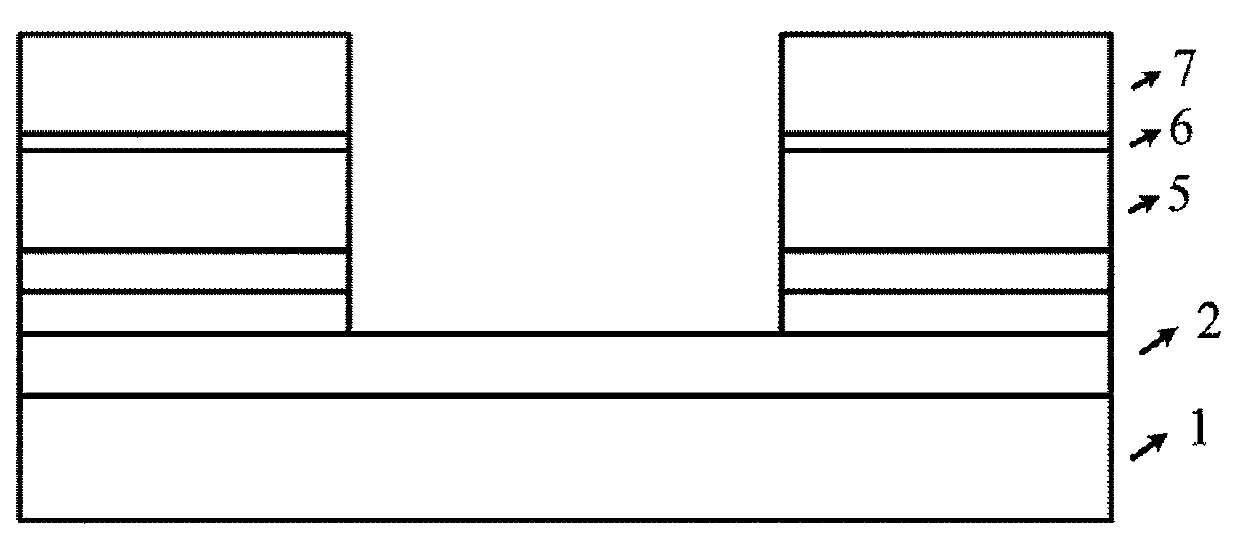

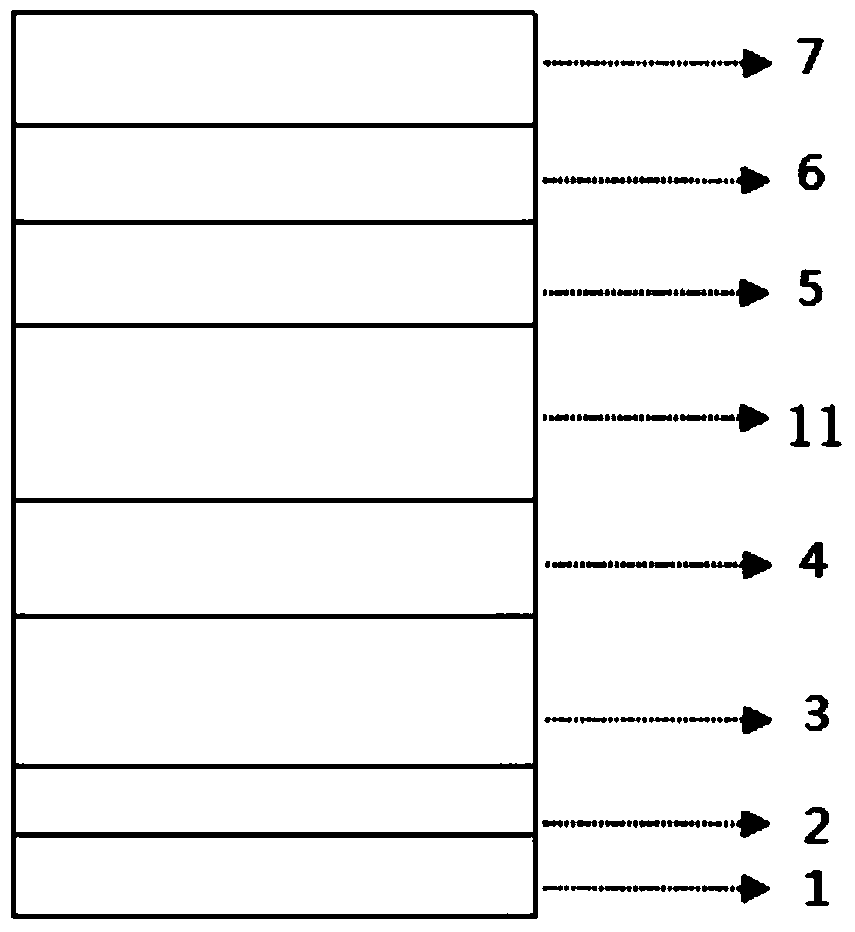

Method for preparing silicon-based high-mobility CMOS (complementary metal-oxide-semiconductor) provided with III-V/Ge channel

ActiveCN103390591AImprove lattice qualitySolid-state devicesSemiconductor/solid-state device manufacturingUltra-high vacuumGallium arsenate

The invention discloses a method for preparing a silicon-based high-mobility CMOS provided with an III-V / Ge channel. The method comprises steps as follows: a germanium layer is grown on a silicon substrate; a low-temperature nucleation gallium arsenide layer, a high-temperature gallium arsenide layer, an on-growth semi-insulating InGaP (gallium indium phosphide) layer and a gallium arsenide cover coating are sequentially grown on the germanium layer after the first annealing, so that a sample is formed; the gallium arsenide cover coating of the sample is subjected to a gallium arsenide polishing process, and a nMOSFET (metal oxide semiconductor field effect transistor) structure is grown after the sample is subjected to secondary annealing; an area is selected on the surface of the nMOSFET structure for ICP (inductively coupled plasma) etching, downward etching from the nMOSFET structure to the germanium layer is performed to form a groove, and silicon dioxide layers are grown in the groove and on the surface of the nMOSFET structure in a PECVD (plasma enhanced chemical vapor deposition) manner; the area selected for etching is subjected to ICP etching again from the silicon dioxide layers to the germanium layer, and a groove is formed; the sample is cleaned, and a germanium nucleating layer and a germanium top layer are grown in the groove with an ultra-high vacuum chemical vapor deposition method; the germanium top layer is polished, and a part of silicon dioxide layers on the nMOSFET structure are removed; and the CMOS process of source, drain and grid electrodes is performed on the nMOSFET structure and the germanium top layer, so that the preparation of the device is finished.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Epitaxial growth method and structure for blocking electron leakage and defect extension

The invention provides an epitaxial growth method for blocking electron leakage and defect extension. The method comprises letting NH3, TMGa and TMAl in between a growth multi-quantum well InxGa(1-x)N / GaN layer and a growth P-type GaN layer, and growing an electron barrier layer with a growth thickness of 8 to 25 nm, wherein the layer comprises two to six groups of double-layer structures, and compared to the Al component content of the UAlGaN layer of the last double-layer structure, the Al component content of the UAlGaN layer of each double-structure is increased by 15% to 50%. According to the invention, the UAlGaN / UGaN structure with layer-to-layer gradually increased Al components is utilized as an electron barrier layer, the single energy level height distribution of a conventional P-spacer energy band is changed, the blocking effects on cavity injection are weakened, and the MQW luminescence efficiency is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

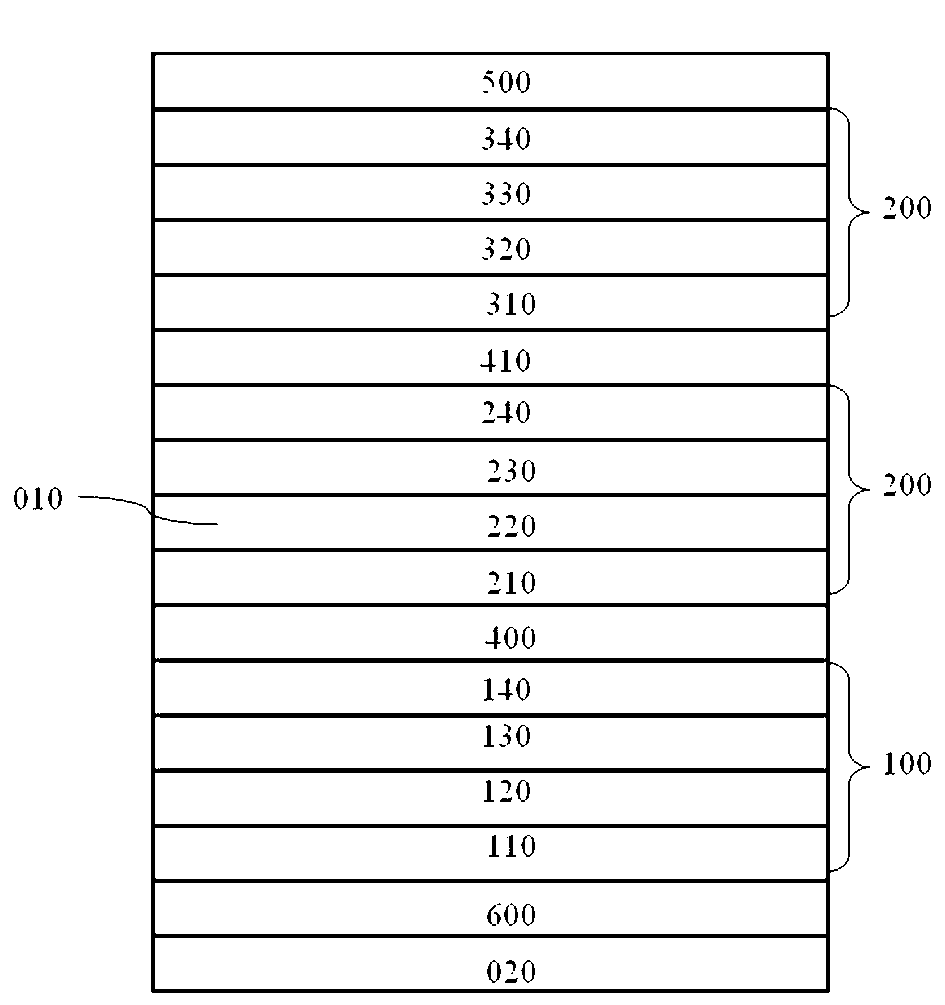

Epitaxial wafer of light emitting diode and manufacturing method thereof

ActiveCN104157763AReduce blocking effectImprove the blocking effectSemiconductor devicesQuantum wellElectron blocking layer

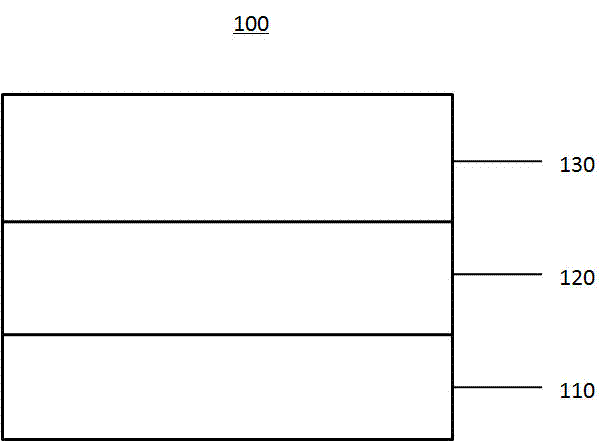

The invention discloses an epitaxial wafer of a light emitting diode and a manufacturing method thereof and belongs to the technical field of semiconductors. The epitaxial wafer comprises an underlayer and a low temperature buffer layer, a high temperature buffer layer, an N type layer, an active layer, an electronic resisting layer and a P type layer which are stacked on the underlayer in sequence, wherein the electronic resisting layer comprises a GaN layer and at least two AlGaN layers stacked on the GaN layer; the Al component content of the AlGaN layers increases or reduces layer-by-layer in the growing direction of the epitaxial wafer. According to the invention, the electronic resisting layer is arranged, so that the energy level height of the electronic resisting layer increases or reduces layer-by-layer, the resisting function of injecting the active layer to a hole is weakened, electrons can be prevented from leaking from a quantum well, and the luminous efficiency is improved.

Owner:HC SEMITEK SUZHOU

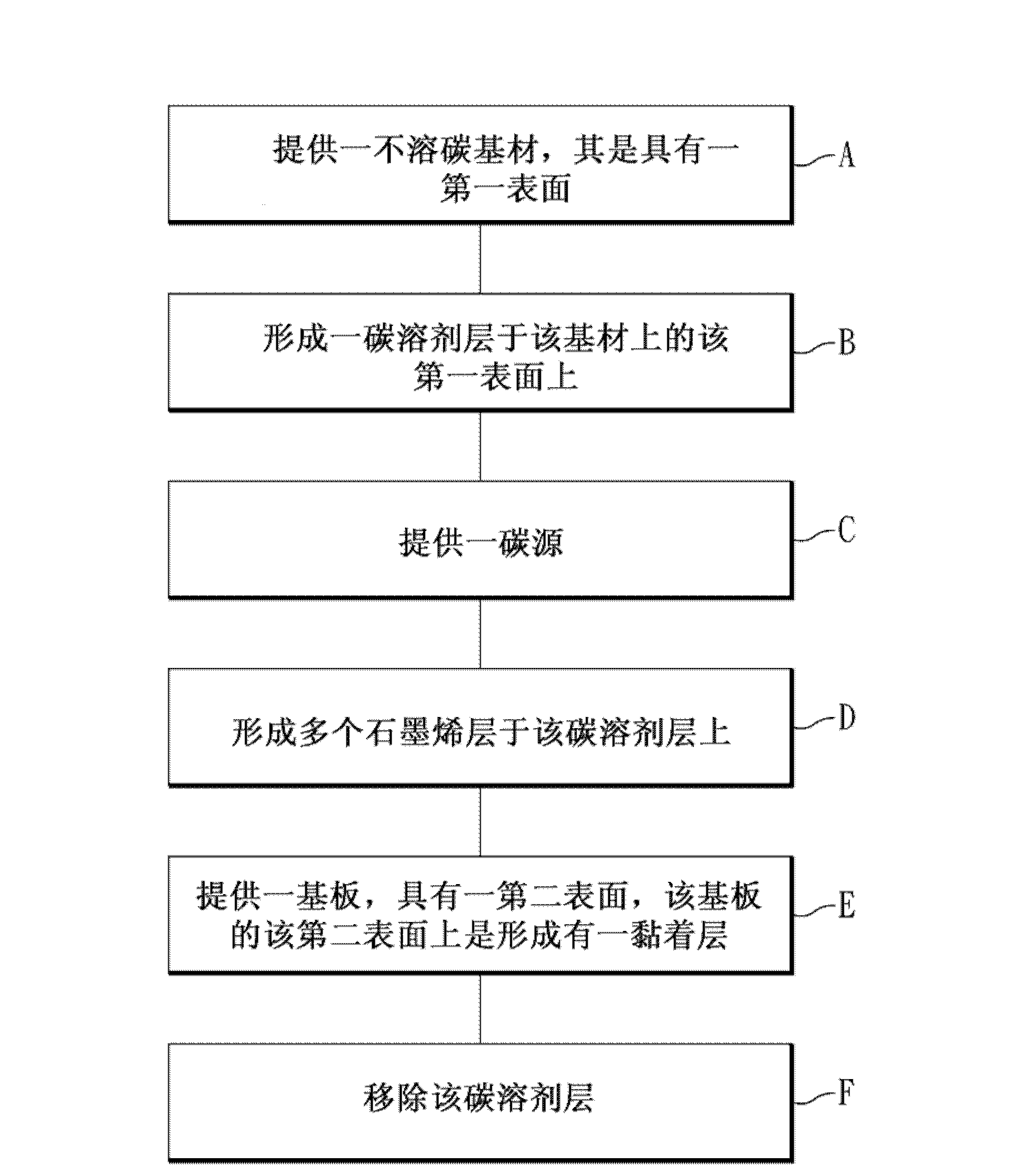

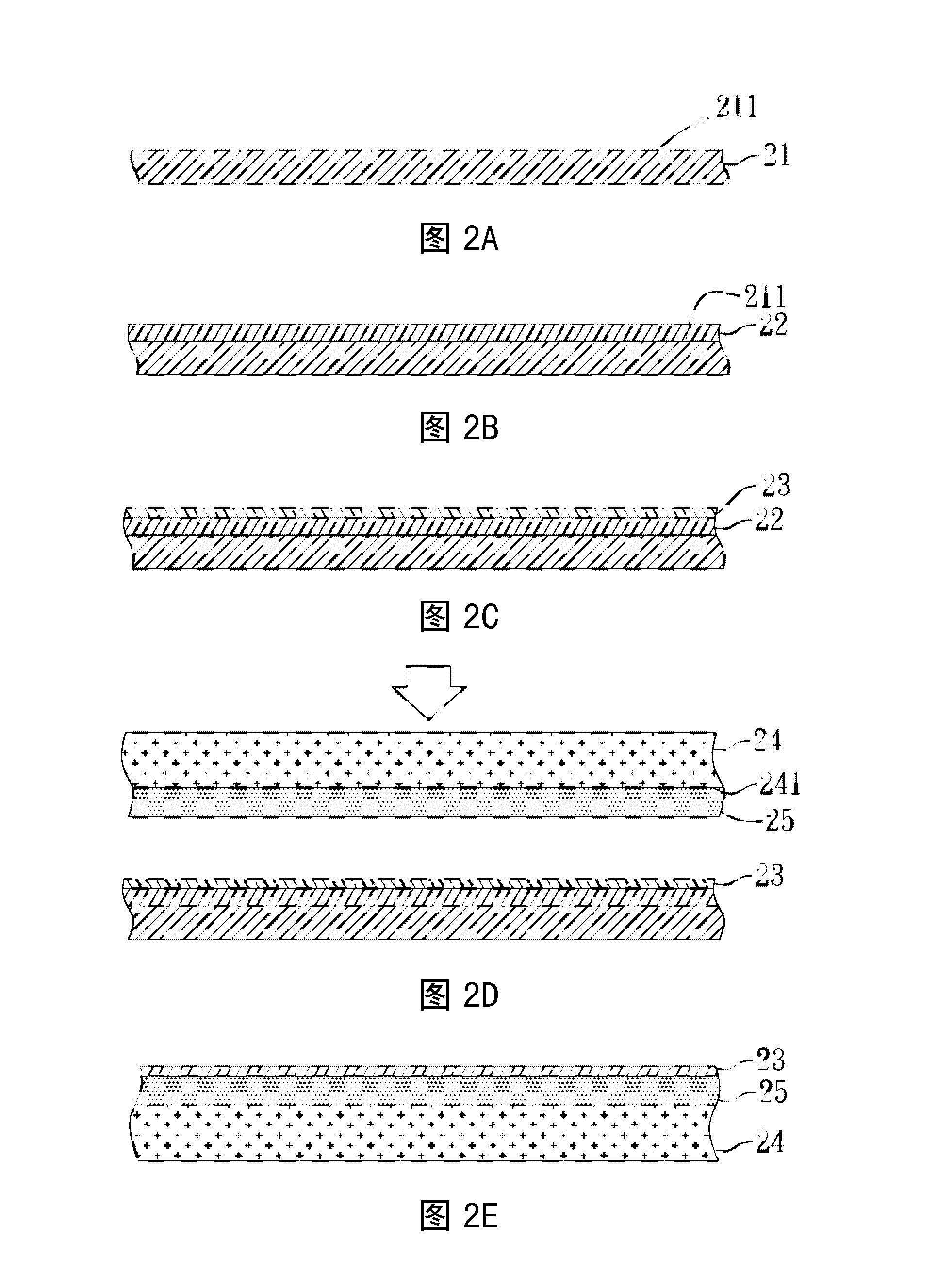

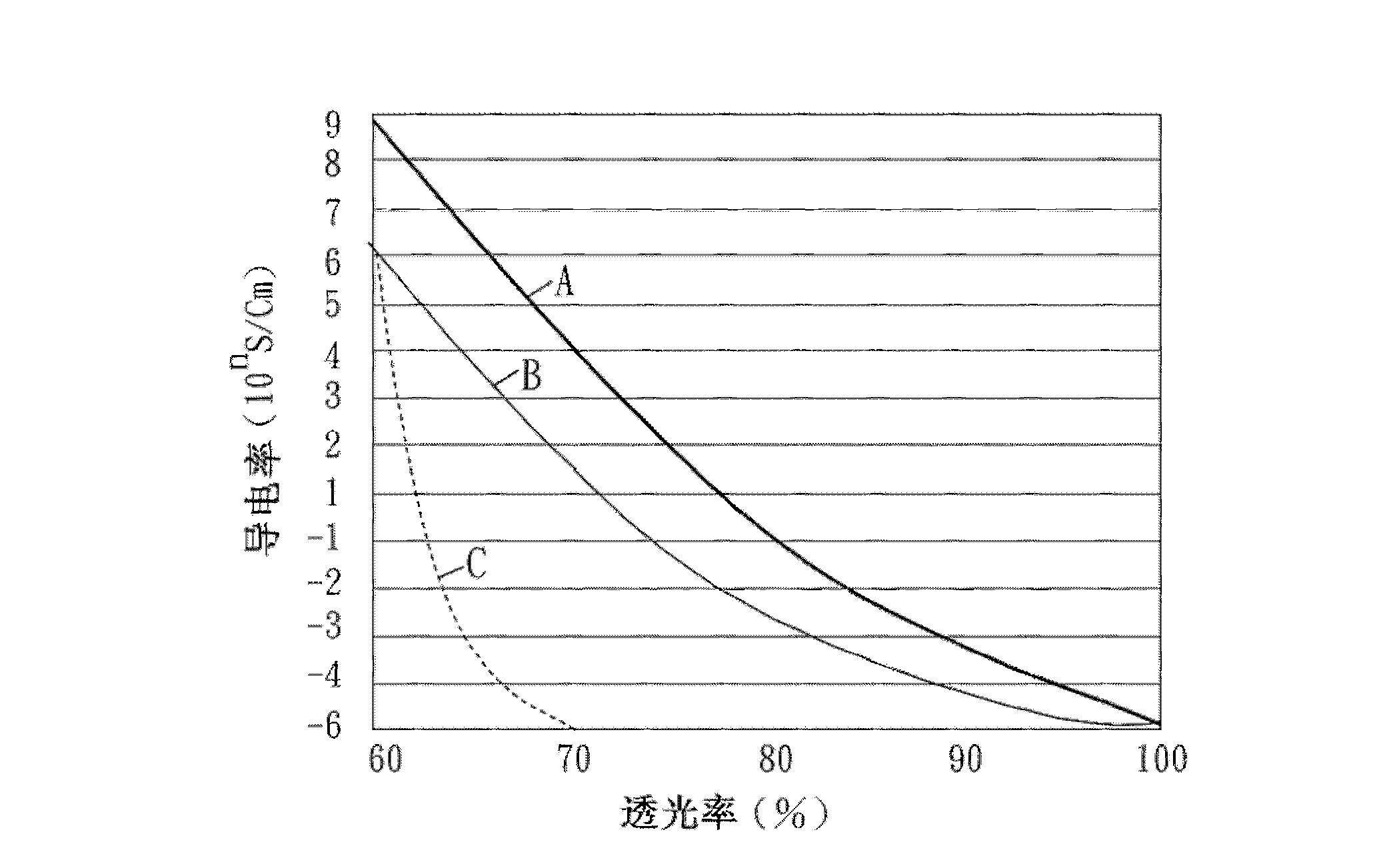

Manufacture method fro transparent electrodes

InactiveCN102682918AImprove conductivityHigh transparencyTransistorConductive layers on insulating-supportsSolventCvd graphene

The invention provides a manufacture method for transparent electrodes, comprising steps of: (A) providing a carbon-insoluble substrate provided with a first surface; (B) forming a carbon solvent layer on the first surface of the substrate; (C) providing a carbon source; and (D) forming a plurality of graphene layers on the carbon solvent layer. Wherein the thickness of graphene layers is controlled by the carbon solvent layer, the carbon source is supplied by a carbon-containing gas, and is used for controlling the growth rate of the graphene layers.

Owner:RITEDIA CORPORATION

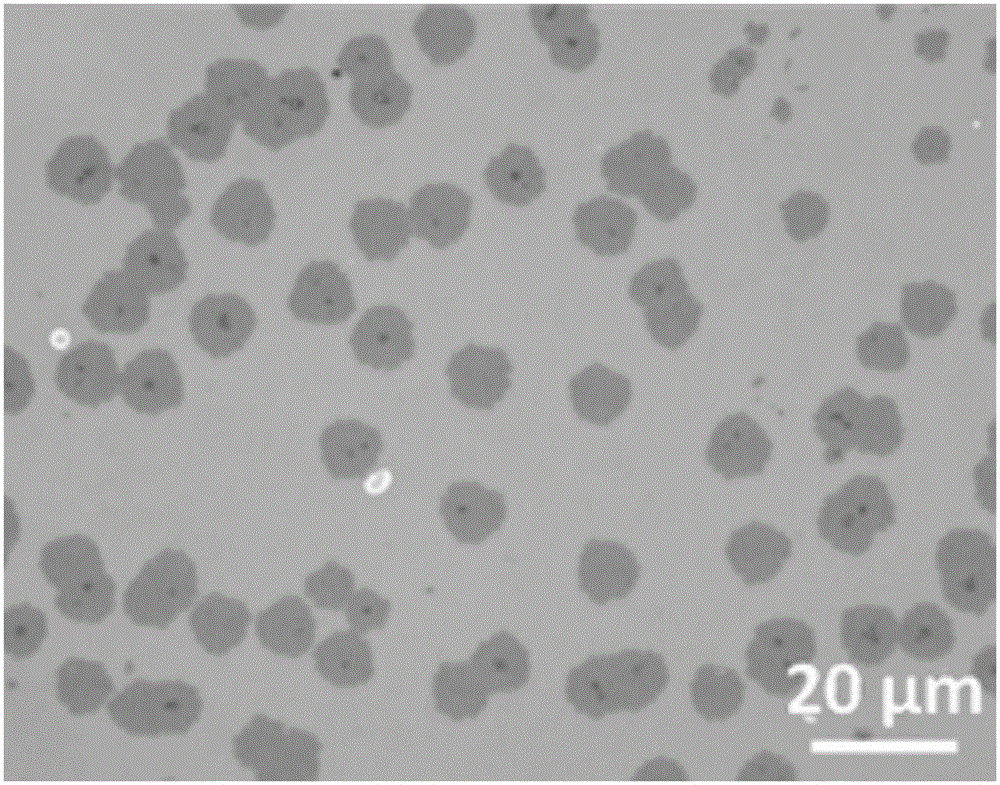

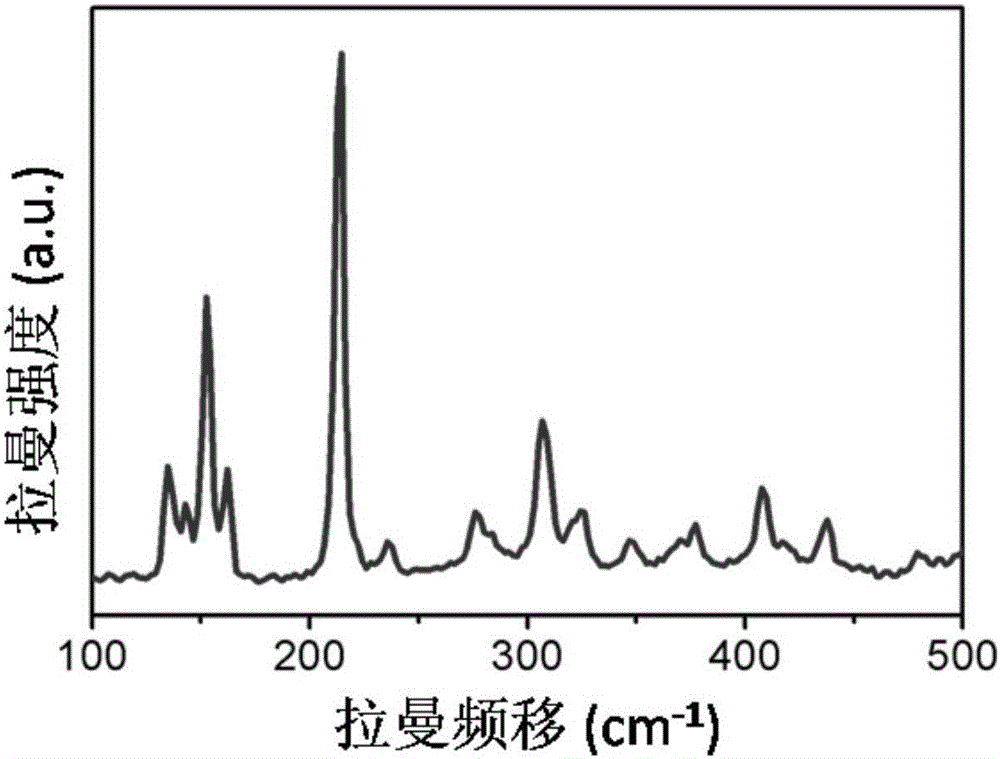

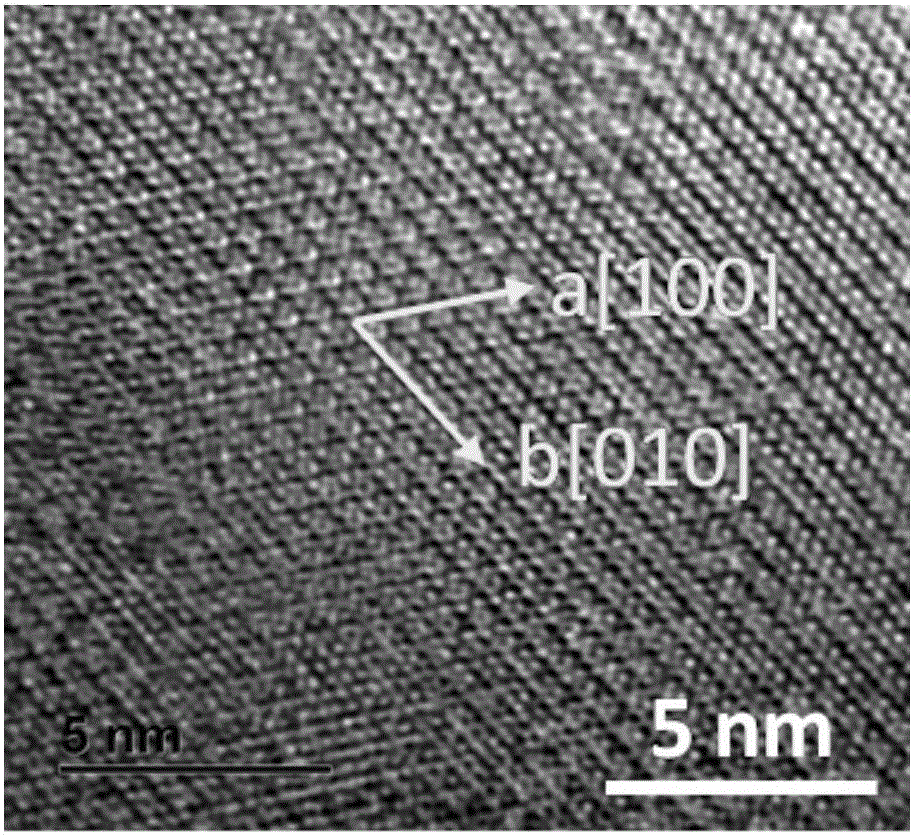

Method for preparing rhenium disulfide thin film through chemical vapor deposition

InactiveCN105839072AImprove growth efficiencyPromotes epitaxial growthChemical vapor deposition coatingRheniumArgon atmosphere

The invention discloses a method for preparing a rhenium disulfide thin film through chemical vapor deposition. According to the method, a two-element eutectoid alloy formed by a mixture of rhenium powder and tellurium powder is used as a rhenium source, powdered sulfur is used as a sulfur source, mica is used as a growth substrate, and the two-dimensional rhenium disulfide thin film grows under the argon atmosphere at the temperature ranging from 500 DEG C to 900 DEG C. Compared with an existing rhenium disulfide preparation method, the requirement for device conditions is low, the operation process is simple, the method has the beneficial effects of being low in reaction temperature, high in growth efficiency, even in layer number, high in lattice quality of the obtained product and good in controllability, large-area, high-quality and layer-number-controllable controlled growth of rhenium disulfide is achieved, and a reliable sample preparation method is provided for application of rhenium disulfide in the field of electronic and photoelectron devices.

Owner:SHAANXI NORMAL UNIV

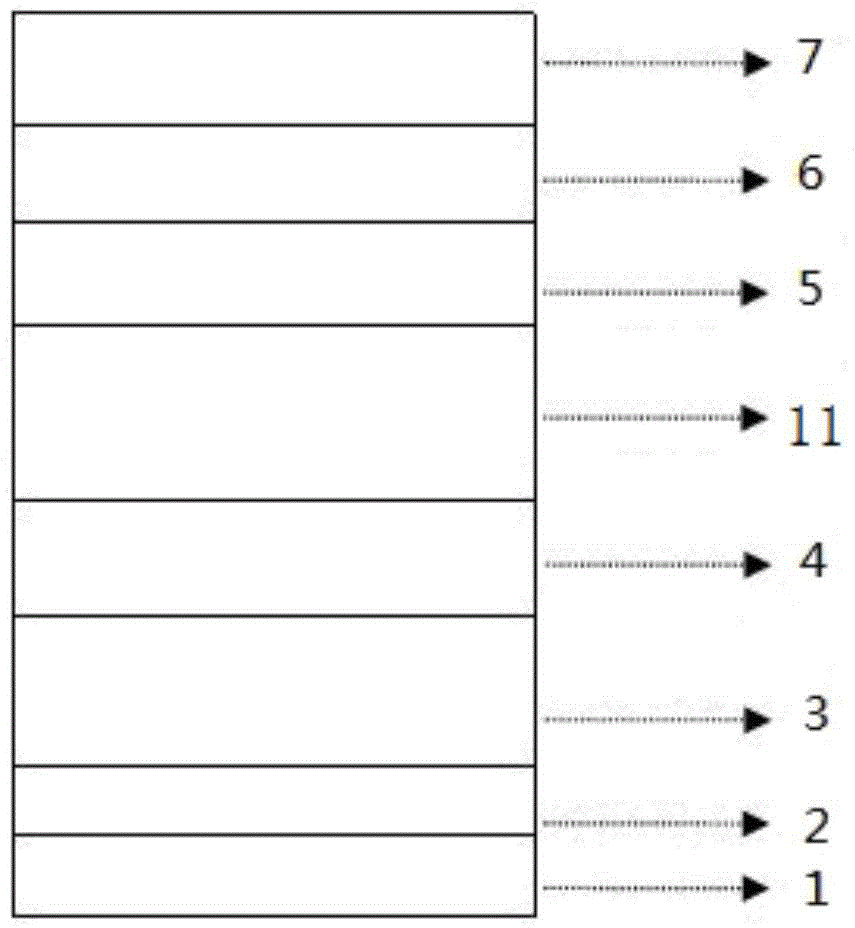

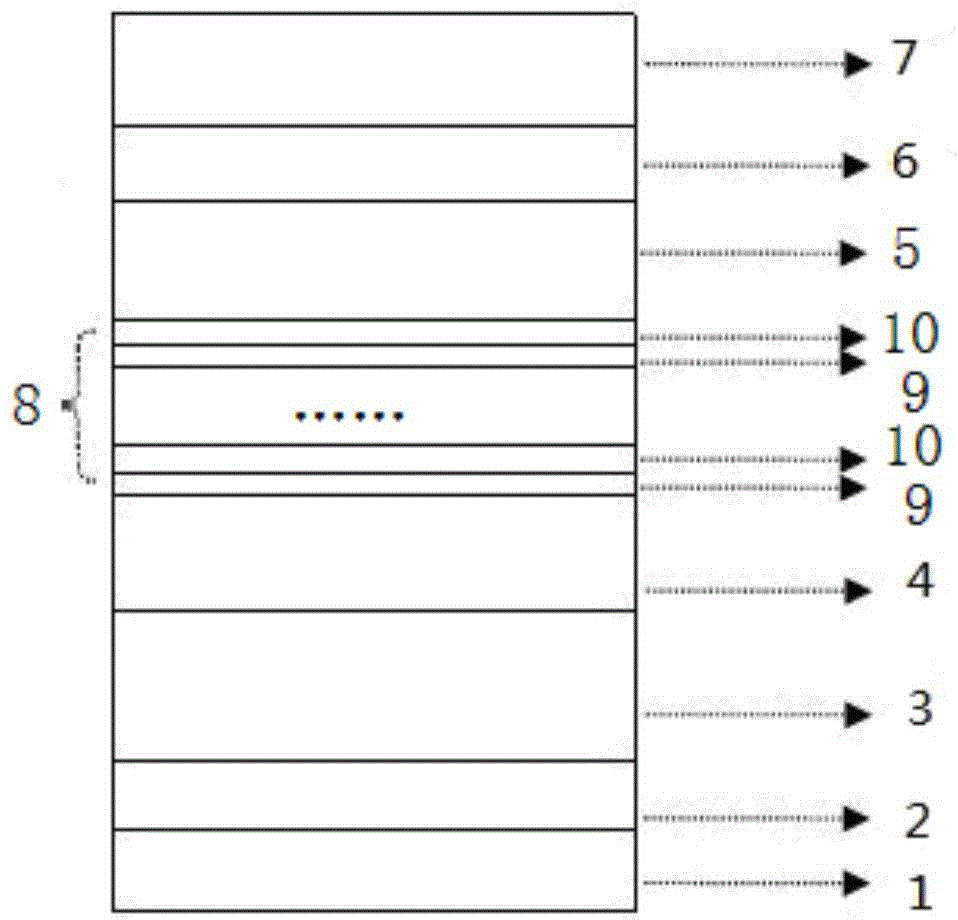

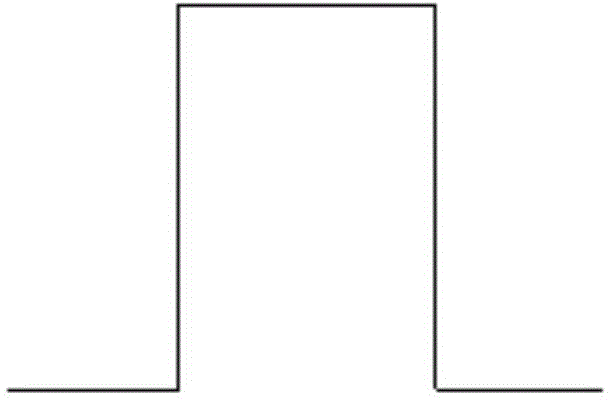

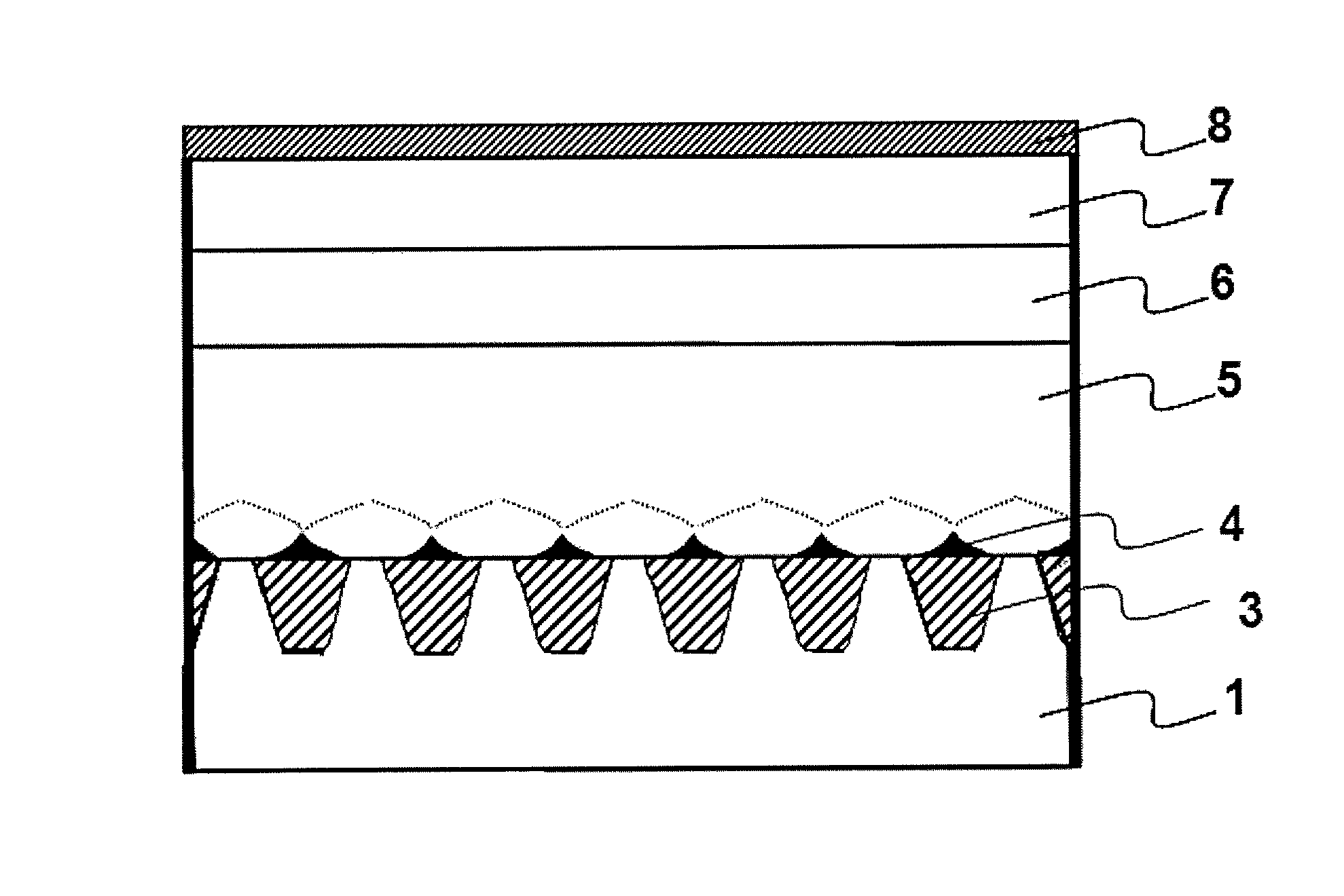

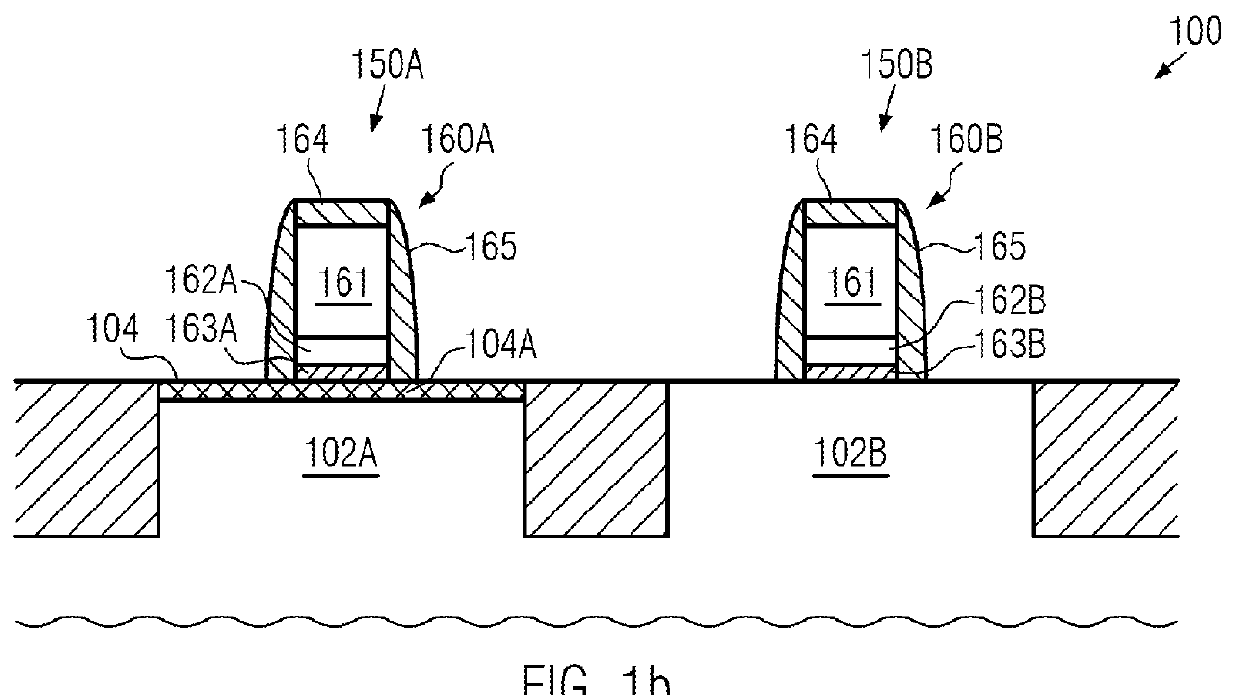

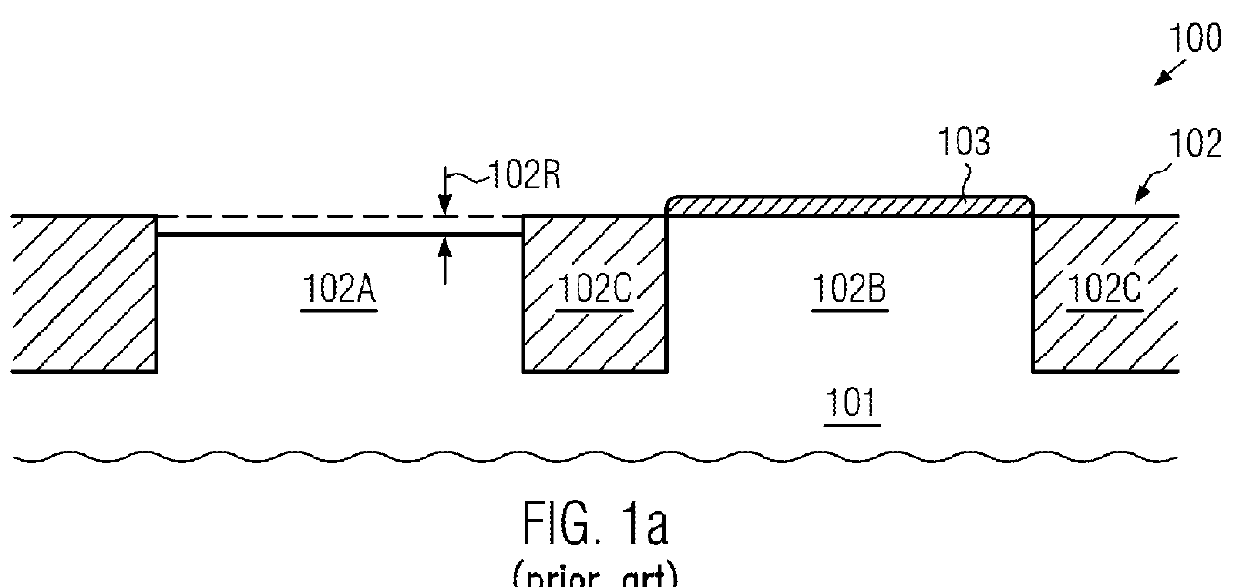

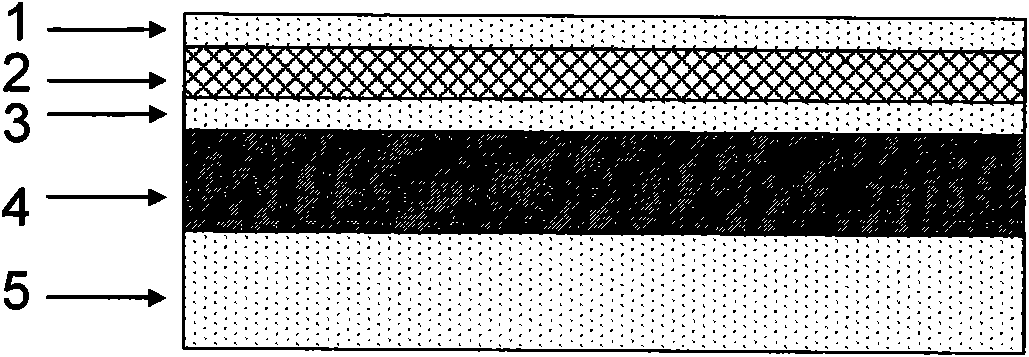

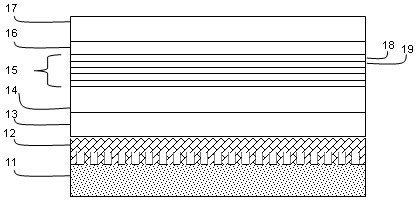

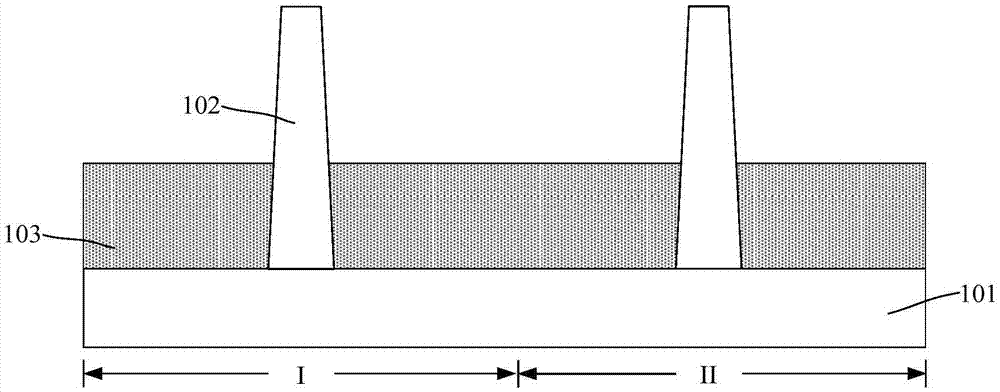

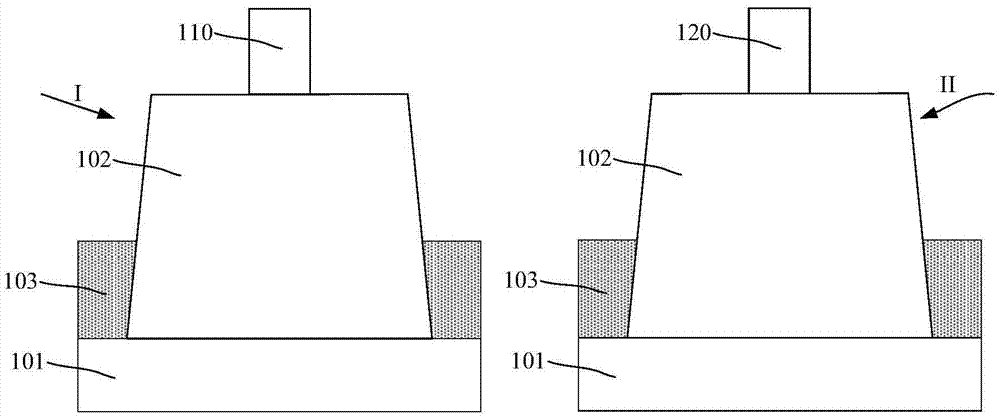

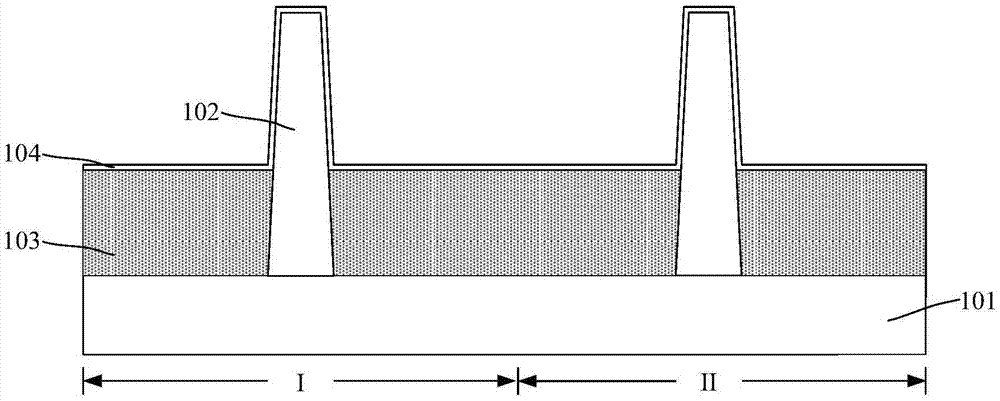

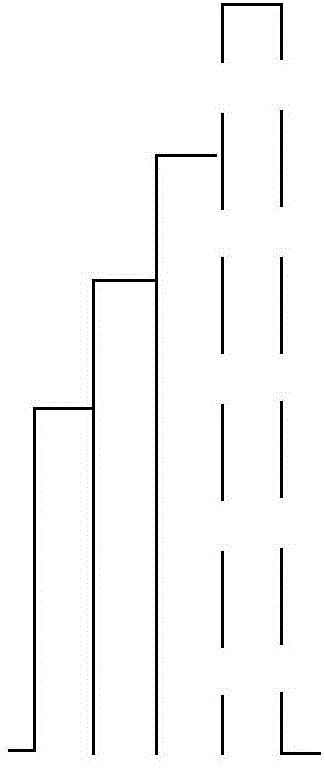

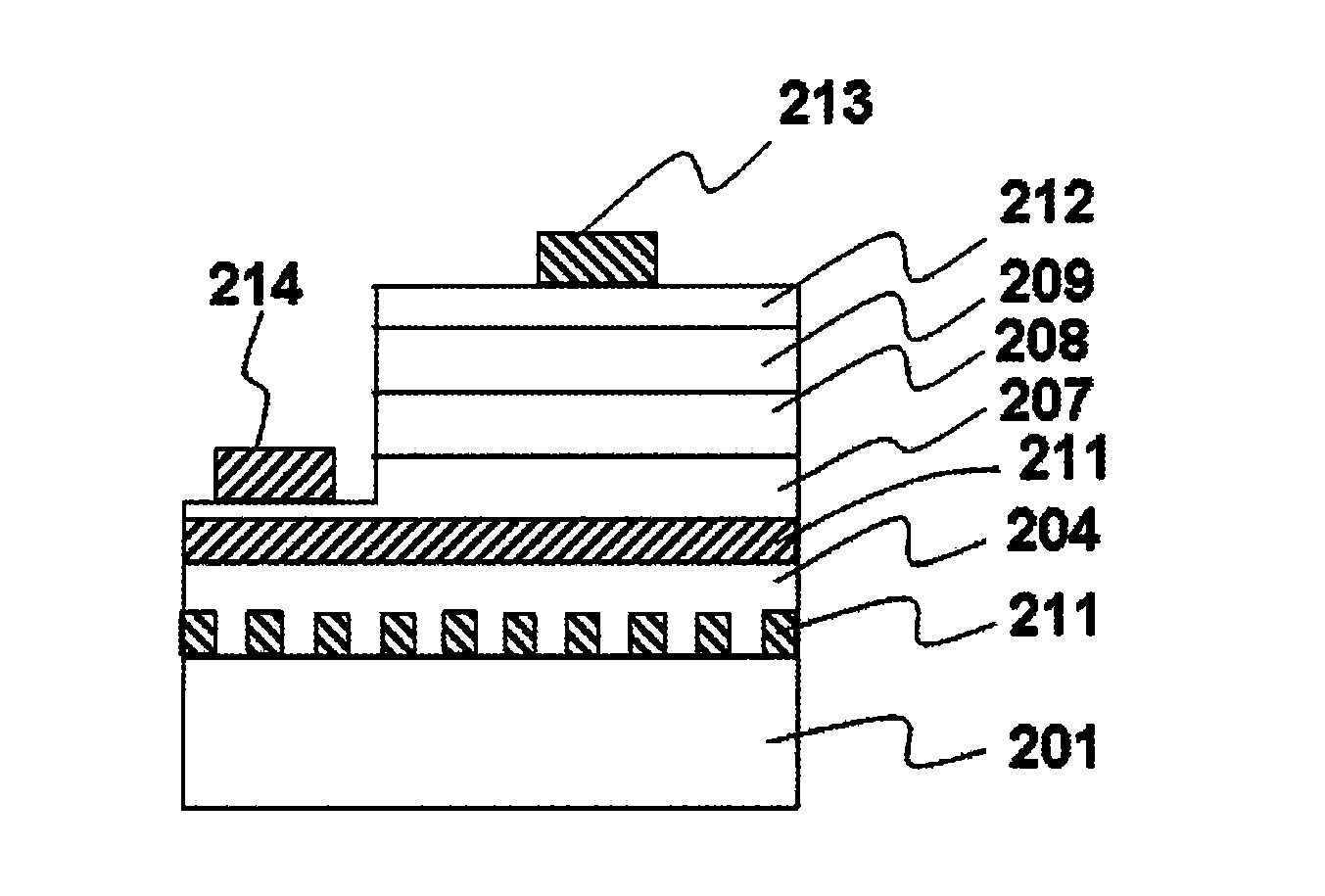

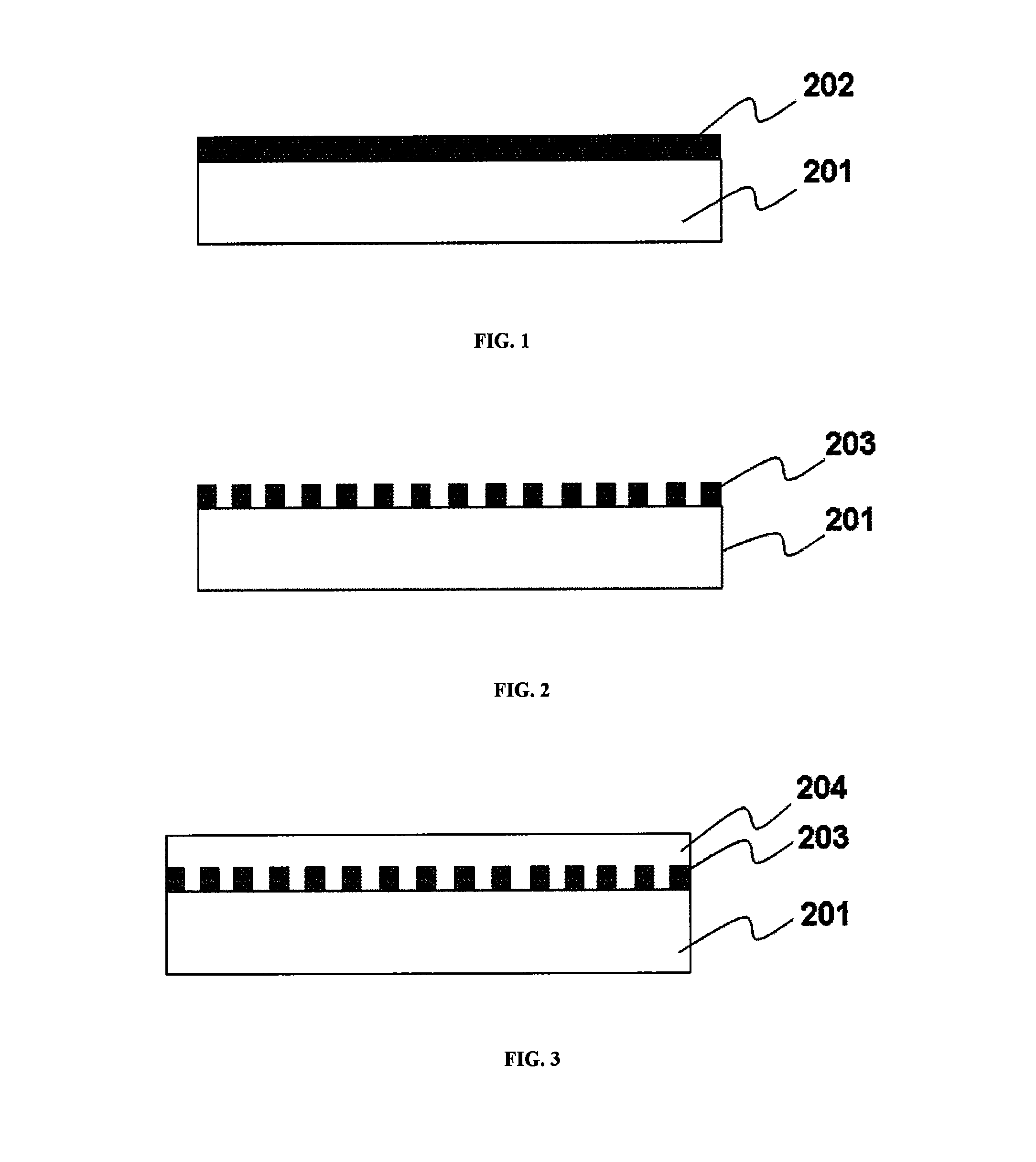

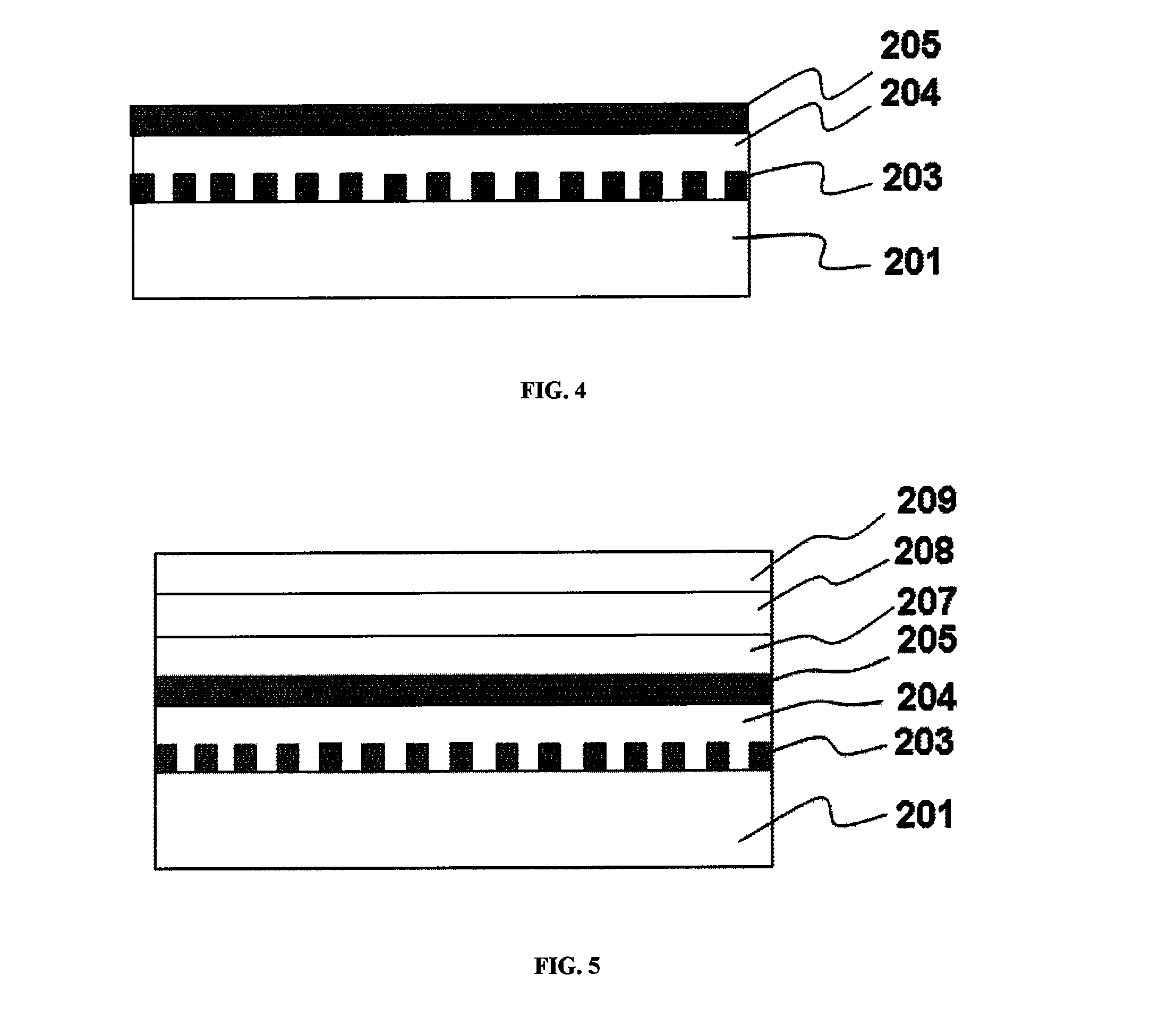

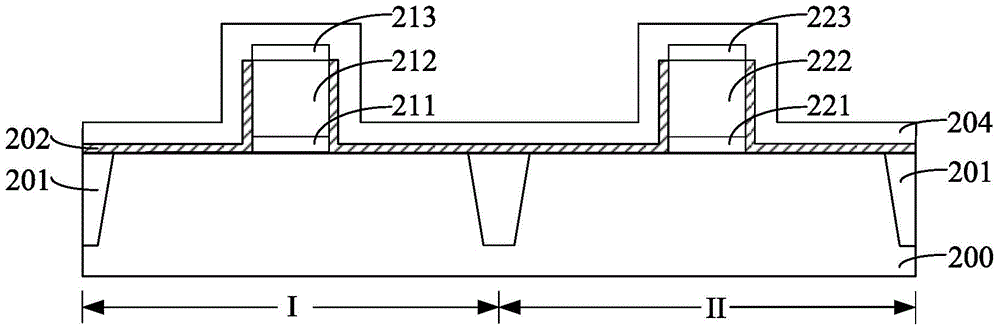

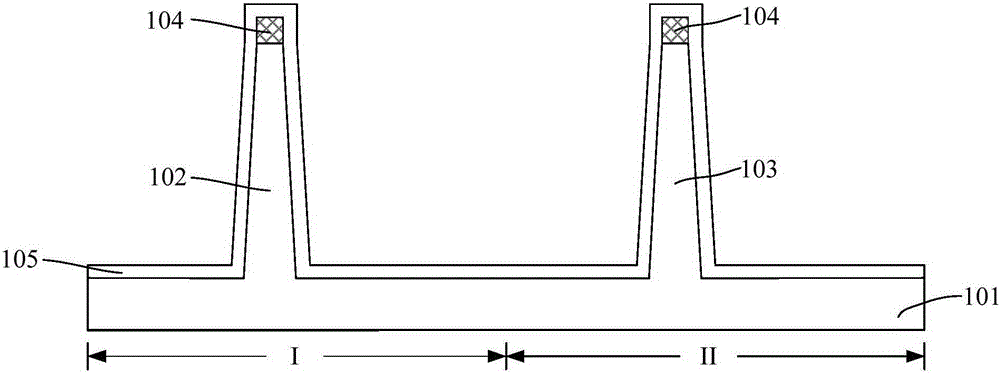

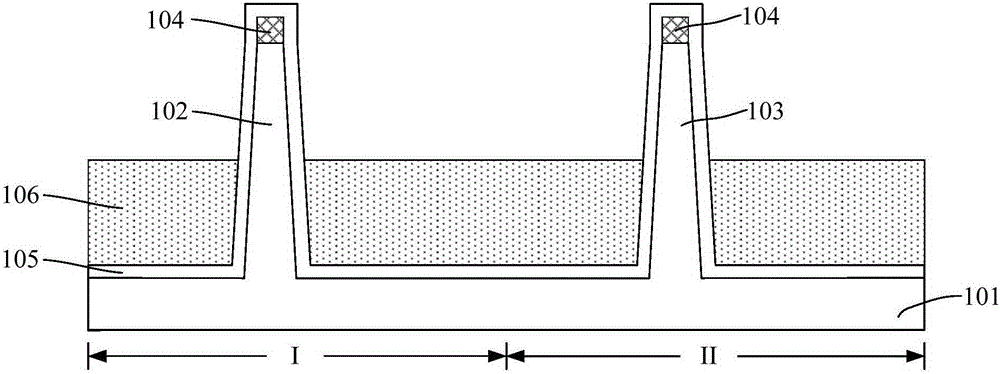

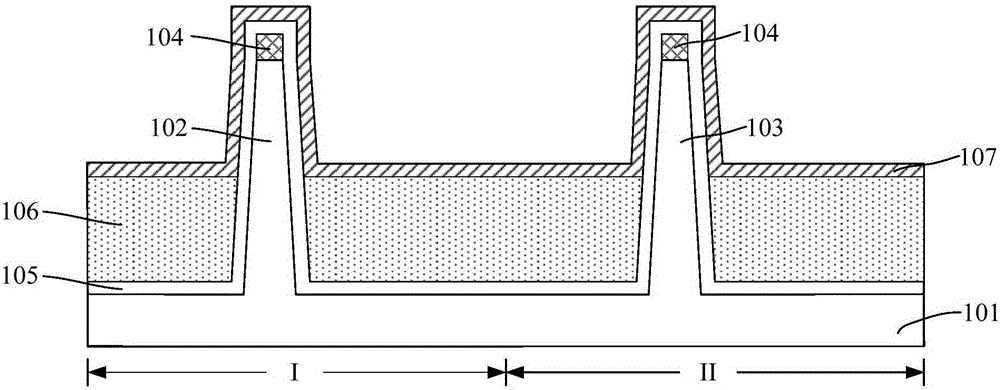

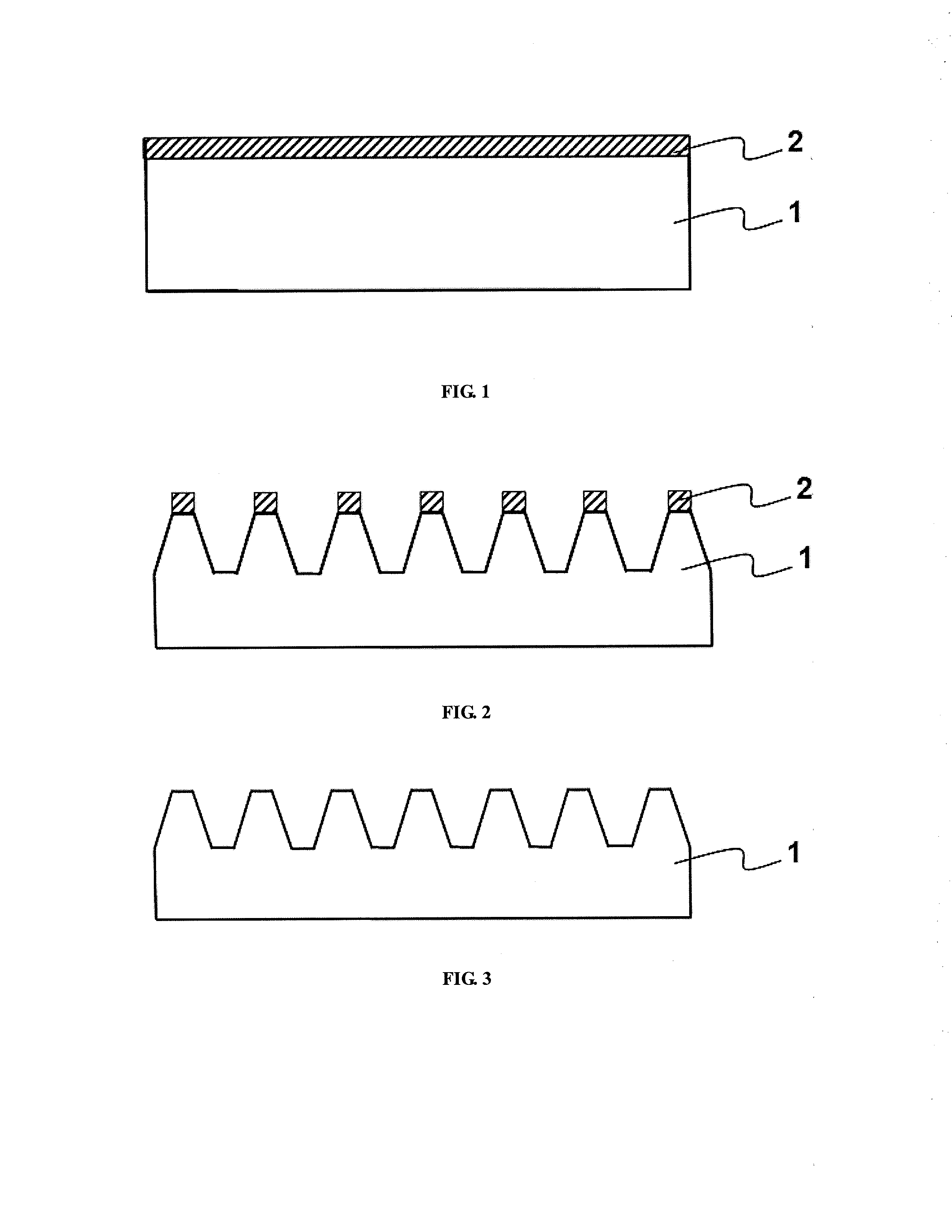

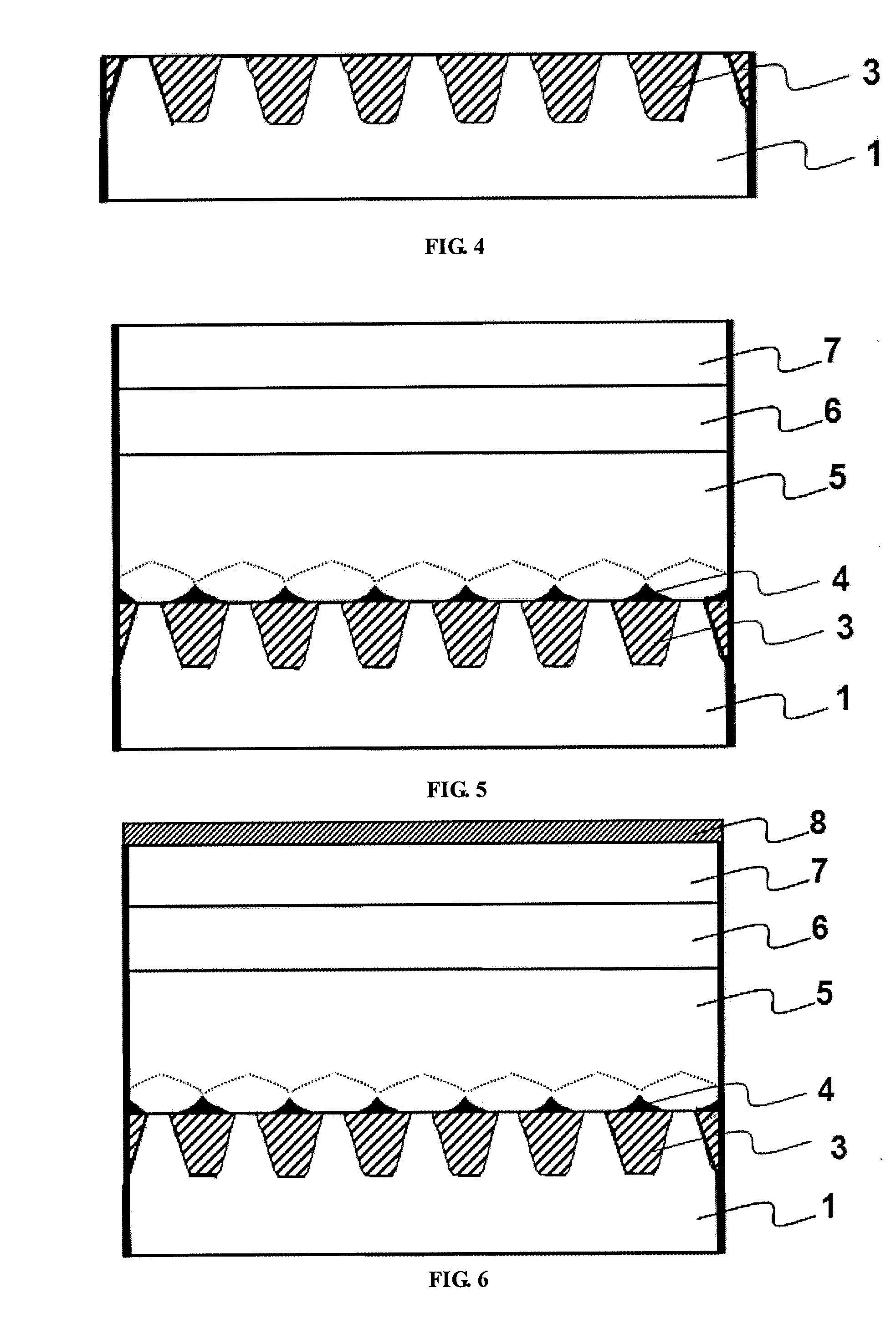

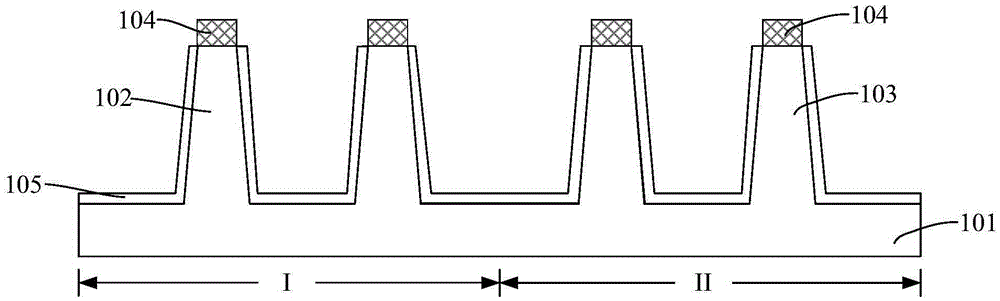

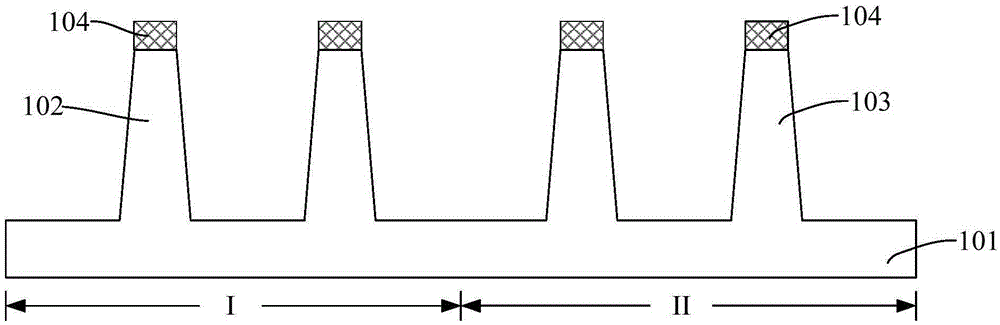

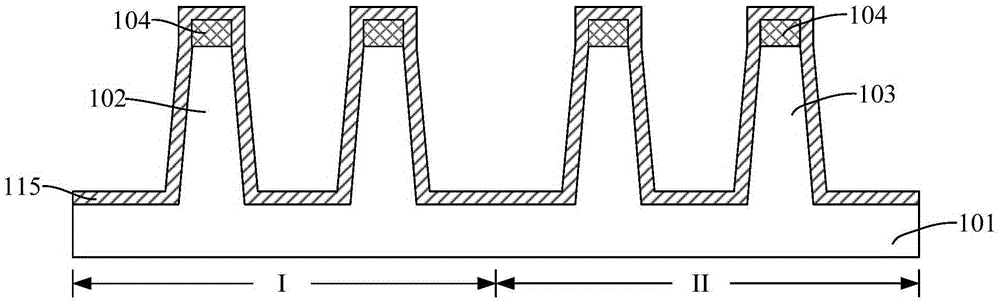

GaN-Based Light-Emitting Diode and Method for Manufacturing the Same

ActiveUS20120043578A1Reduce dislocation densityImprove lattice qualitySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingProtection layer

A GaN-based LED and a method for manufacturing the same are provided, and the method includes: providing a substrate, depositing a first transition layer on the substrate; forming a first patterned transition layer by etching with a mask; growing a first epitaxial layer on the first patterned transition layer; depositing a second transition layer on the first epitaxial layer; forming a second patterned transition layer by etching with a mask, such that the second patterned transition layer and the first patterned transition layer are cross-staggered with each other; growing a second epitaxial layer on the second patterned transition layer, wherein the second epitaxial layer includes a P-type layer, a light-emitting layer and an N-type layer; depositing a protection layer on the second epitaxial layer, dicing to obtain chips with a defined size; removing the first patterned transition layer and the second patterned transition layer on the substrate and the protection layer on the second epitaxial layer by wet etching, so as to form a structure with two layers of cross-staggered through holes; forming a conductive layer on the second epitaxial layer; and forming a P-electrode and an N-electrode by etching with a mask. The two layers of cross-staggered through holes of the LED chips can effectively reduce the dislocation density in the epitaxial growth of the GaN-based layer, and improve the lattice quality and luminous efficiency.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

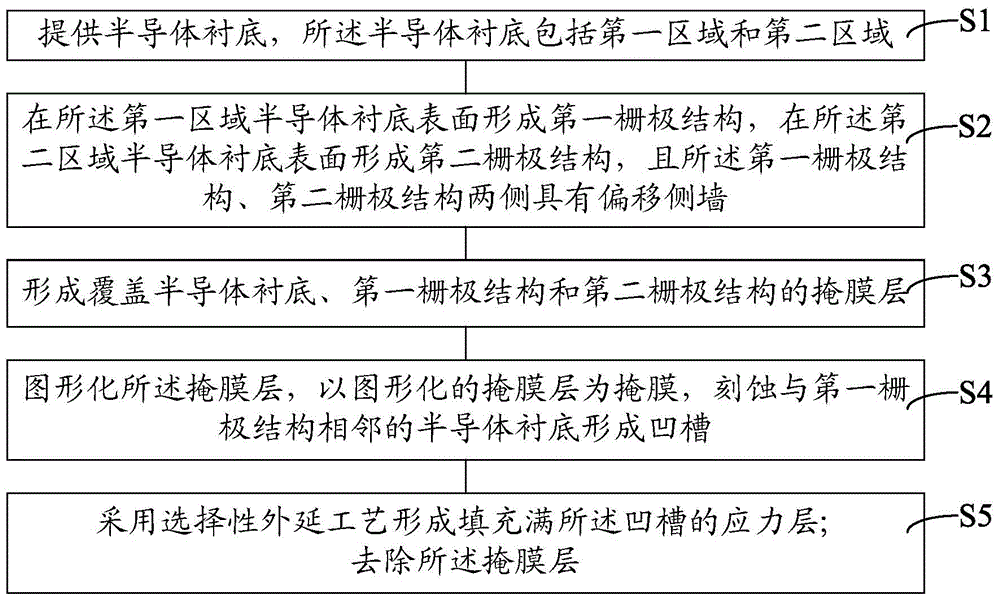

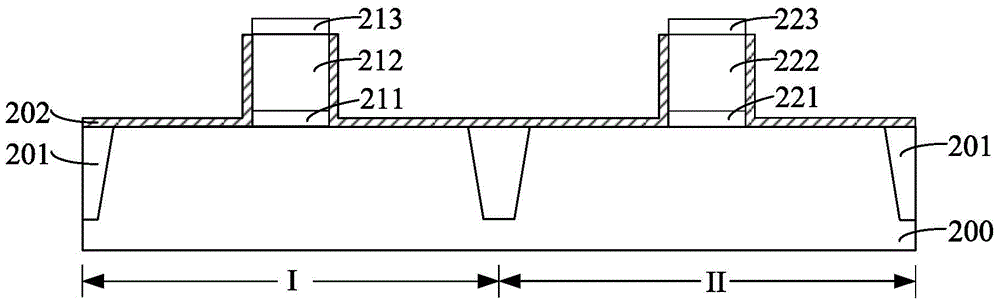

Formation method of semiconductor device

InactiveCN105097457AImprove lattice qualityReduce defectsSemiconductor/solid-state device manufacturingFilm materialEngineering

A formation method of a semiconductor device comprises the steps of providing a substrate, wherein a grid structure is formed on the surface of the substrate; etching to remove the partial thickness of substrate at the two sides of the grid structure to form grooves; carrying out the oxidation treatment on the surfaces of the grooves to form oxidation films, and repairing the crystal lattice damage on the surfaces of the grooves; removing the oxidation films to expose the surfaces of the grooves; adopting an epitaxy process to form the stress layers filling the grooves. According to the present invention, before the stress layers are formed, the oxidation treatment is carried out on the surfaces of the grooves, the materials having the crystal lattice damage on the surfaces of the grooves are transformed into the oxidation film materials, and then the oxidation films are removed, so that the exposed crystal lattices on the surfaces of the grooves are high in quality, and accordingly, the stress layers of high quality and few defects are conducive to being formed, the stress actions of the stress layers in a channel region are larger, and a driving current of the formed semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Fin type field effect transistor formation method

InactiveCN106558556AFacilitated DiffusionImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesIonField-effect transistor

The invention provides a fin type field effect transistor formation method comprising the steps that a protective layer is formed on the surface of a substrate, and the top part of the protective layer is lower than the top part of a first fin part and the top part of a second fin part; a first side wall is formed on the surface of the side wall of the first fin part higher than the top part of the protective layer; a second side wall is formed on the surface of the side wall of the second fin part higher than the top part of the protective layer; partial thickness or all the thickness of the protective layer is removed; a first epitaxial layer is formed on the surface of the side wall of the exposed first fin part, and the first epitaxial layer includes first penetration prevention ions; a second epitaxial layer is formed on the surface of the side wall of the exposed second fin part, and the second epitaxial layer includes second penetration prevention ions; annealing is performed on the first epitaxial layer and the second epitaxial layer; the first side wall and the second side wall are removed; and a dielectric layer is formed on the substrate, the surface of the first epitaxial layer and the surface of the second epitaxial layer. The electrical performance of the formed fin type field effect transistor can be improved by the fin type field effect transistor formation method.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

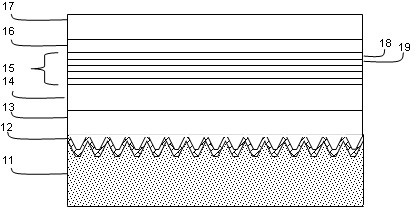

Method for lift-off of light-emitting diode substrate

ActiveUS20120190148A1Reduce dislocation densityImprove lattice qualitySemiconductor/solid-state device manufacturingSemiconductor devicesLight-emitting diodeDislocation

The present invention discloses a method for lift-off of an LED substrate. By eroding the sidewall of a GaN epitaxial layer, cavity structures are formed, which may act in cooperation with a non-fully filled patterned sapphire substrate from epitaxial growth to cause the GaN epitaxial layer to separate from the sapphire substrate. The method according to an embodiment of the present invention can effectively reduce the dislocation density in the growth of a GaN-based epitaxial layer; improve lattice quality, and realize rapid lift-off of an LED substrate, and has the advantages including low cost, no internal damage to the GaN film, elevated performance of the photoelectric device and improved luminous efficiency.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

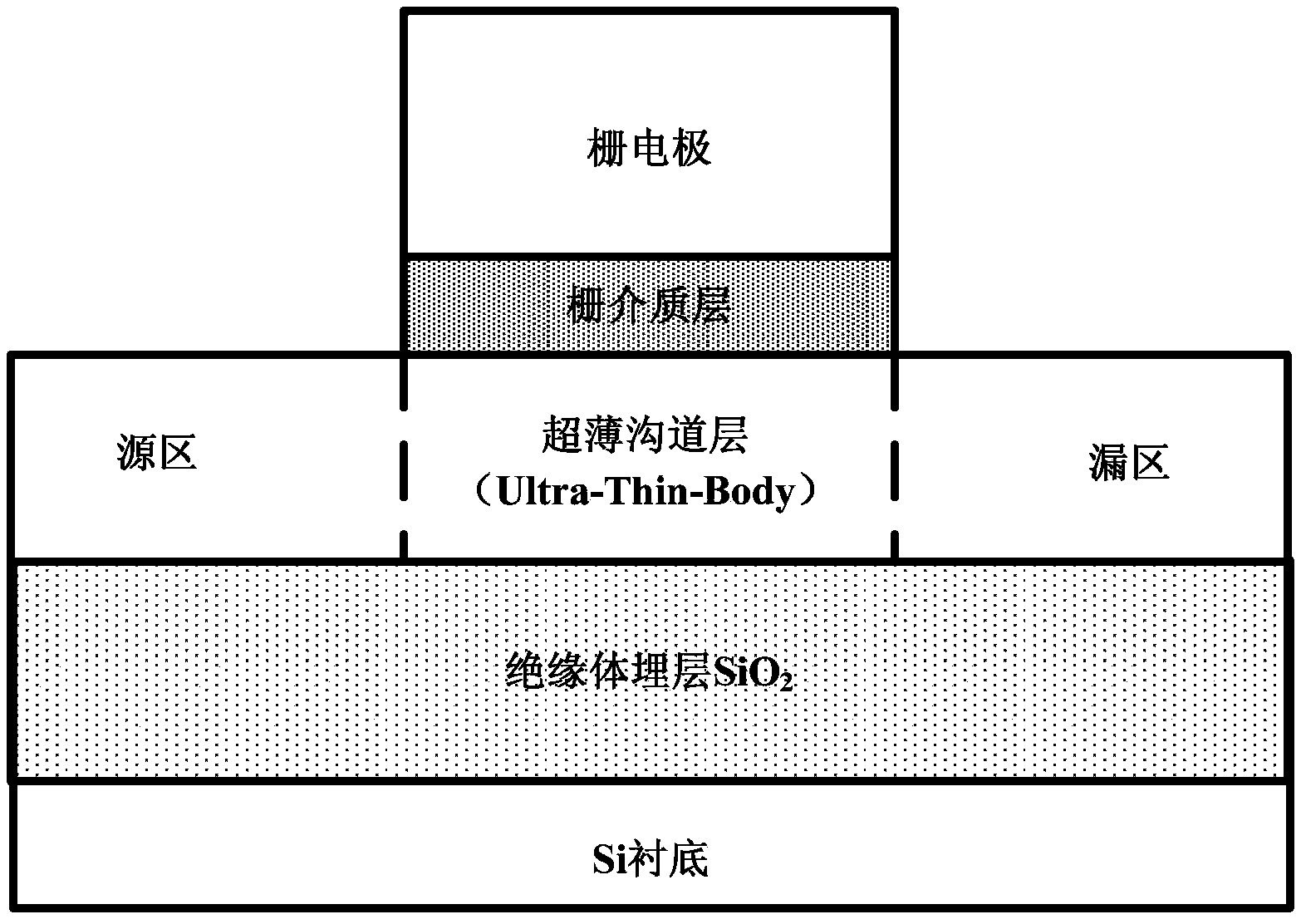

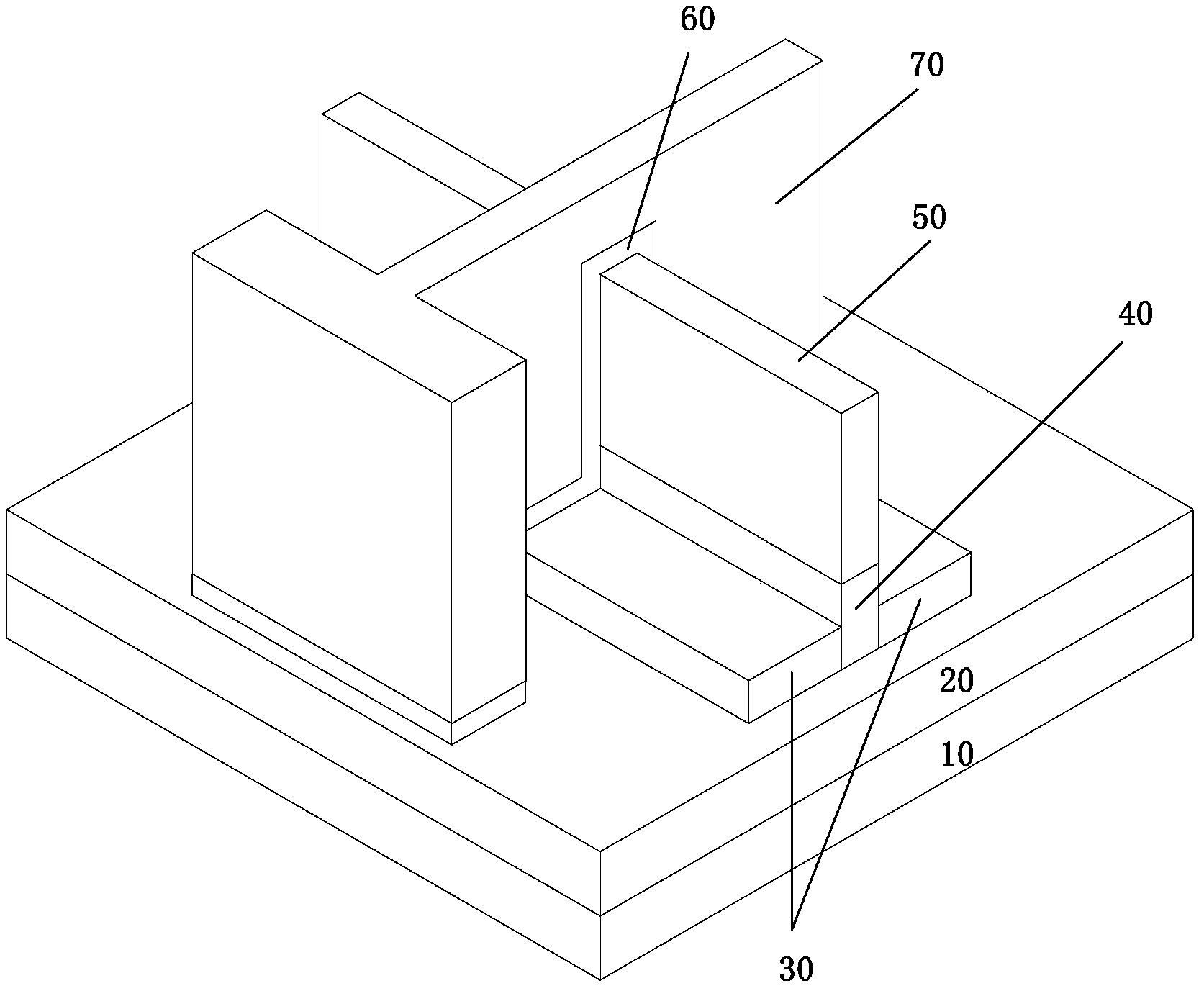

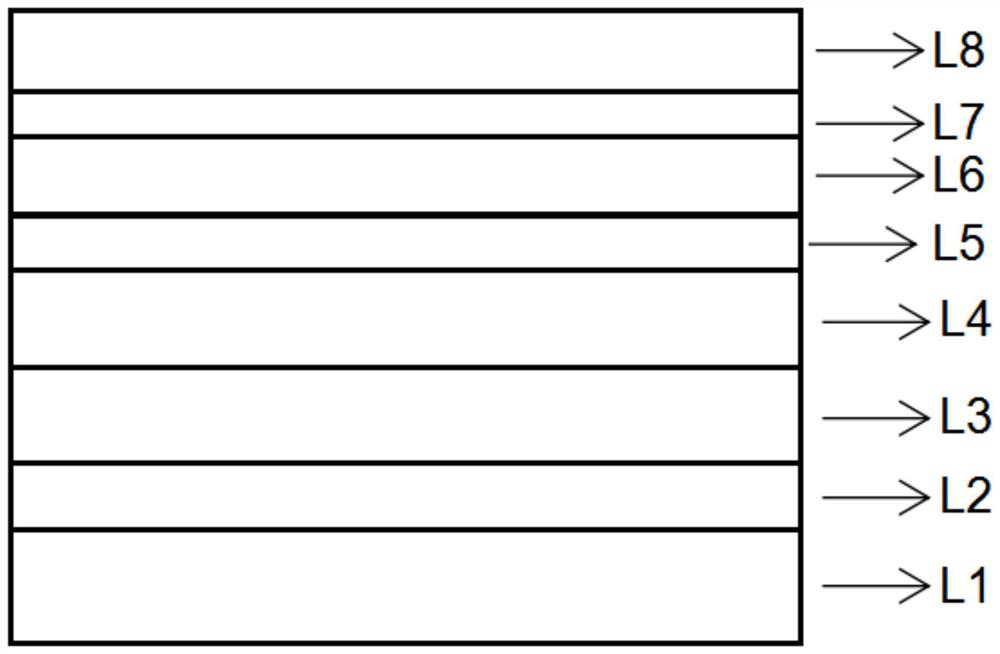

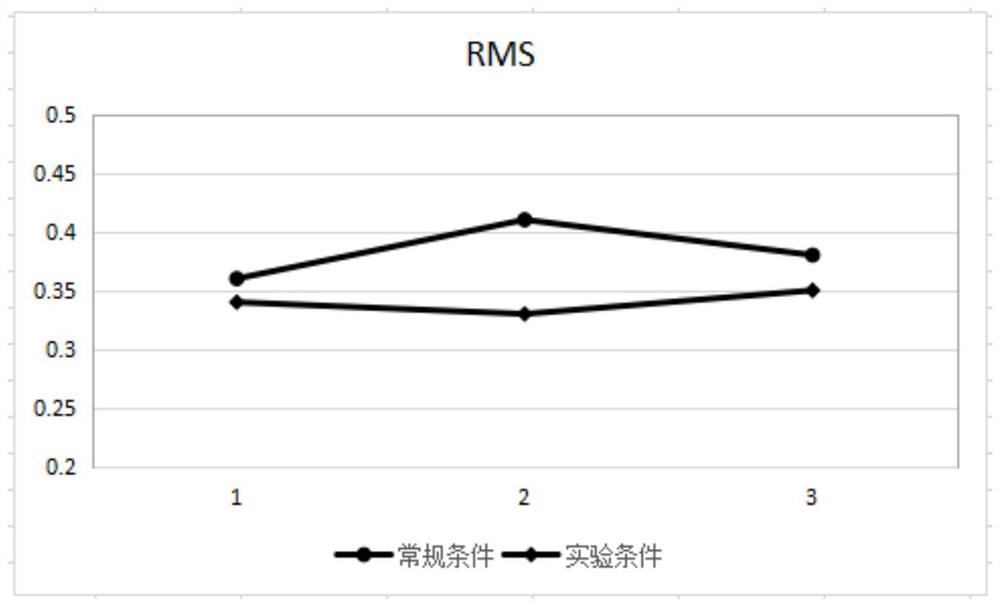

Three-dimensional semiconductor device on insulator and forming method of three-dimensional semiconductor device

ActiveCN103400858ASimple structureImprove lattice qualityTransistorSolid-state devicesDriving currentInsulation layer

The invention discloses a three-dimensional semiconductor device on an insulator and a forming method of the three-dimensional semiconductor device. The device comprises a substrate, an ultra-thin insulation layer, a plane ultra-thin semiconductor structure, an insulation fin-shaped seed layer, a vertical semiconductor fin, a grid dielectric layer and a grid electrode, wherein the ultra-thin insulation layer is made of single crystal rare earth oxide or single crystal beryllium oxide, the plane ultra-thin semiconductor structure has the first width and the second width, and is positioned above the ultra-thin insulation layer, the insulation fin-shaped seed layer has the second width and the second height, is embedded in the plane ultra-thin semiconductor structure and is in adjacent joint with the upper surface of the ultra-thin insulation layer, the second width is smaller than the first width, the second height is greater than or equal to the first height, the insulation fin-shaped seed layer is made of single crystal rare earth oxide or single crystal beryllium oxide, the vertical semiconductor fin has the third width and the third height, and is positioned above the insulation fin-shaped seed layer, and in addition, the third width is smaller than the first width. The three-dimensional semiconductor device has the advantages that the driving current is great and can be continuously regulated, the process compatibility is realized, and the qualification rate is high.

Owner:TSINGHUA UNIV

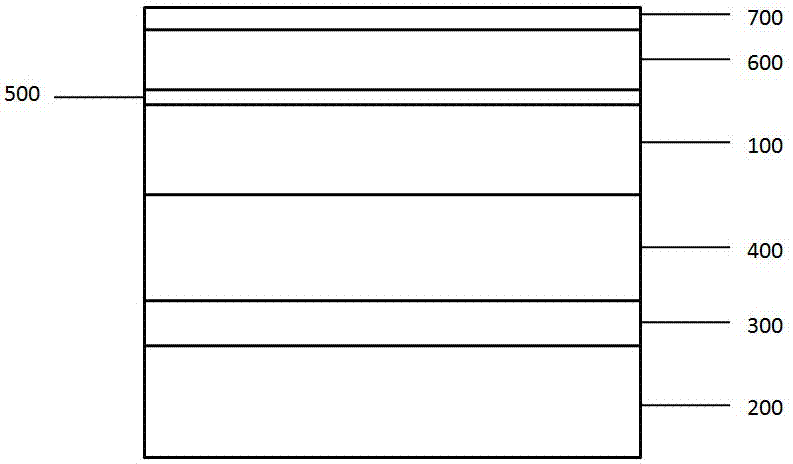

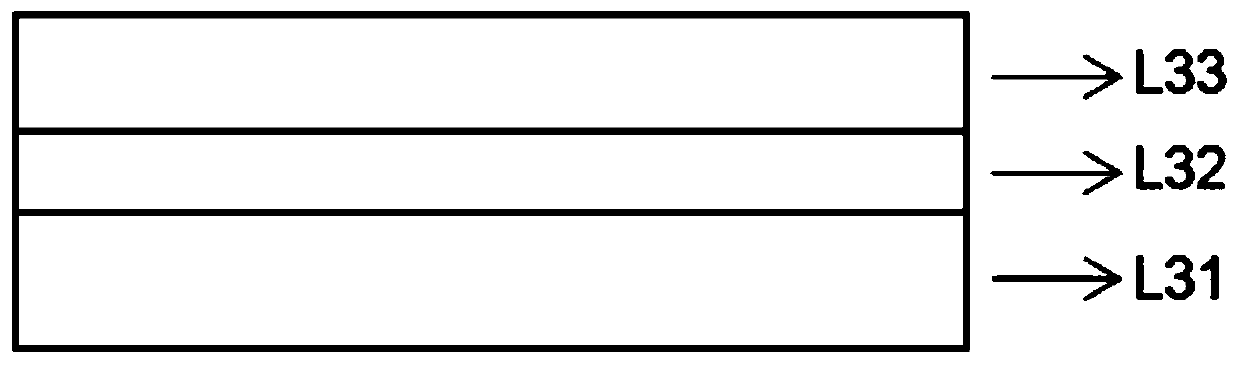

P-type cap layer enhanced HEMT device and preparation method thereof

PendingCN112133749AAchieve epitaxial preparationEnabling Enhanced Epitaxy FabricationSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryMaterials science

The invention discloses a P-type cap layer enhanced HEMT (High Electron Mobility Transistor) device and a preparation method thereof, and belongs to the technical field of microelectronics. The devicecomprise a substrate, a low-temperature nucleating layer, a buffer layer, a high-resistance layer, a channel layer, a barrier layer, an insertion layer and a P-GaN cap layer which are sequentially stacked from bottom to top. The invention provides a new structure and a new growth method, so that the epitaxial preparation of the enhanced HEMT device is realized, and the stability of the performance of the enhanced HEMT device is ensured.

Owner:西安电子科技大学芜湖研究院

Method for forming fin field effect transistor

ActiveCN106571339AGood lookingImprove lattice qualitySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical performanceField-effect transistor

A method for forming a fin field effect transistor comprises the following steps: forming a first fin on the surface of the substrate in a NMOS region and forming a second fin on the surface of the substrate in a PMOS region; forming a first doping layer covering the sidewall surface of the first fin, wherein the first doping layer contains first anti-punchthrough ions; forming a second doping layer on the sidewall surface of the second fin, wherein the second doping layer contains second anti-punchthrough ions; forming a dielectric layer on the surface of the substrate, wherein the top of the dielectric layer is lower than the top of the first fin and the top of the second fin; removing the first doping layer higher than the top of the dielectric layer; removing the second doping layer higher than the top of the dielectric layer; subjecting the remaining first doping layer and the remaining second doping layer to annealing to diffuse the first anti-punchthrough ions into the first fin to form a first anti-punchthrough layer and to diffuse the second anti-punchthrough ions into the second fin to form a second anti-punchthrough layer. The method improves the electrical performance of the formed fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

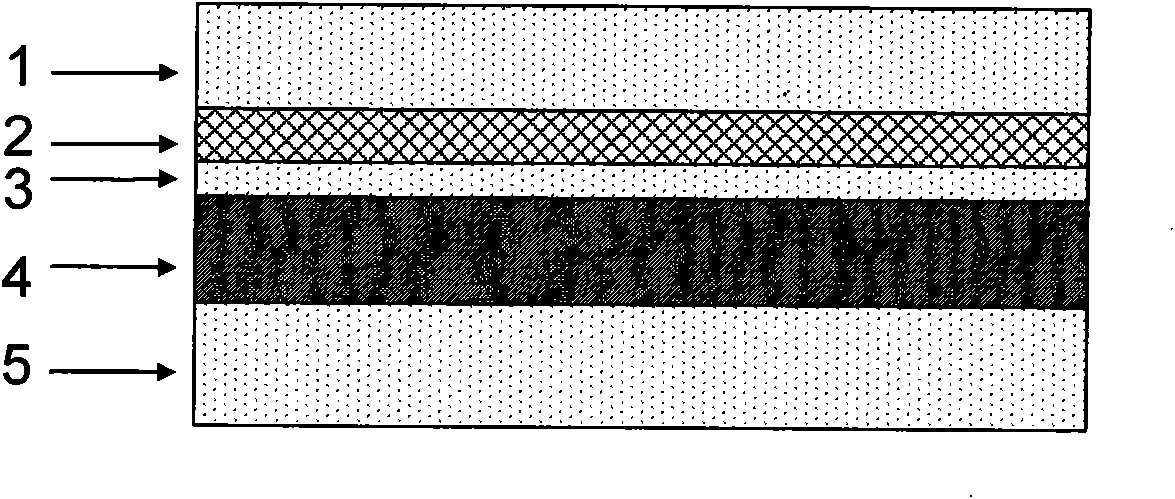

Self-doped silicon-germanium/silicon multiple quantum well thermosensitive material applied to uncooled infrared detection array

ActiveCN103630247AWide infrared response bandEquivalent TCR valueFrom chemically reactive gasesPyrometry using electric radation detectorsIsolation layerContact layer

The invention discloses a thermosensitive material which is of a self-doped silicon-germanium / silicon multiple quantum well structure, has a high temperature resistance coefficient and is applied to an uncooled infrared detection array. The material comprises a bottom contact layer, a bottom isolation layer, the silicon-germanium / silicon multiple quantum well structure, a top isolation layer and a top contact layer. When the thickness of each isolation layer is 35 to 100nm, boron particles diffuse from the contact layers to the silicon-germanium / silicon multiple quantum well structure, so as to form a carrier. The design simplifies a process and is conductive to preparing the silicon-germanium / silicon multiple quantum well structure with high lattice quality. The invention discloses a pixel structure of the uncooled infrared detection array which uses the material. The thickness of each support layer in double support layers is 200nm to 250nm. Under the condition that optical conditions are met, the pixel structure is stable. The invention further discloses an extension growth process, which is based on a low pressure chemical vapor deposition technology, of the material.

Owner:NANJING UNIV OF SCI & TECH

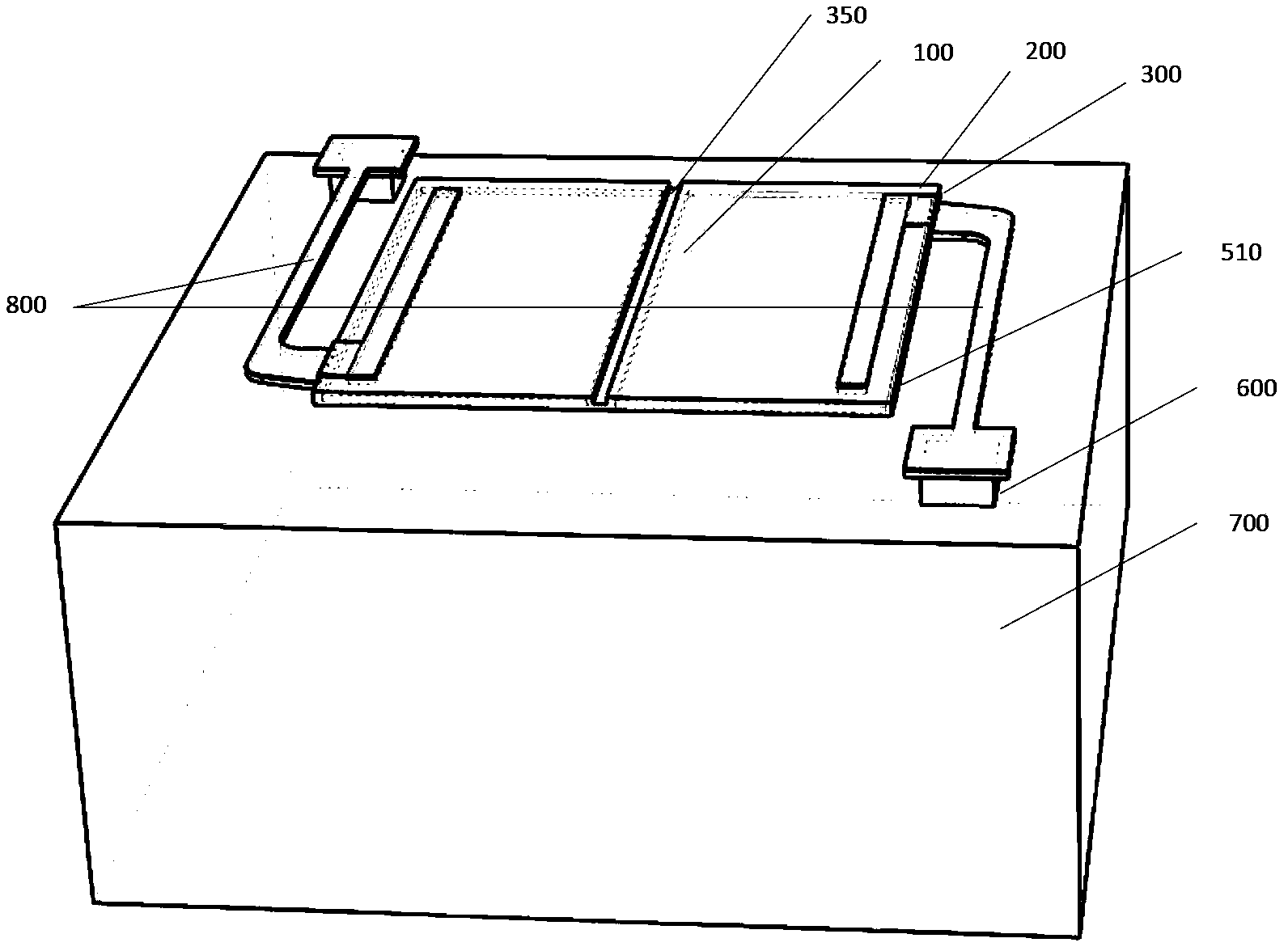

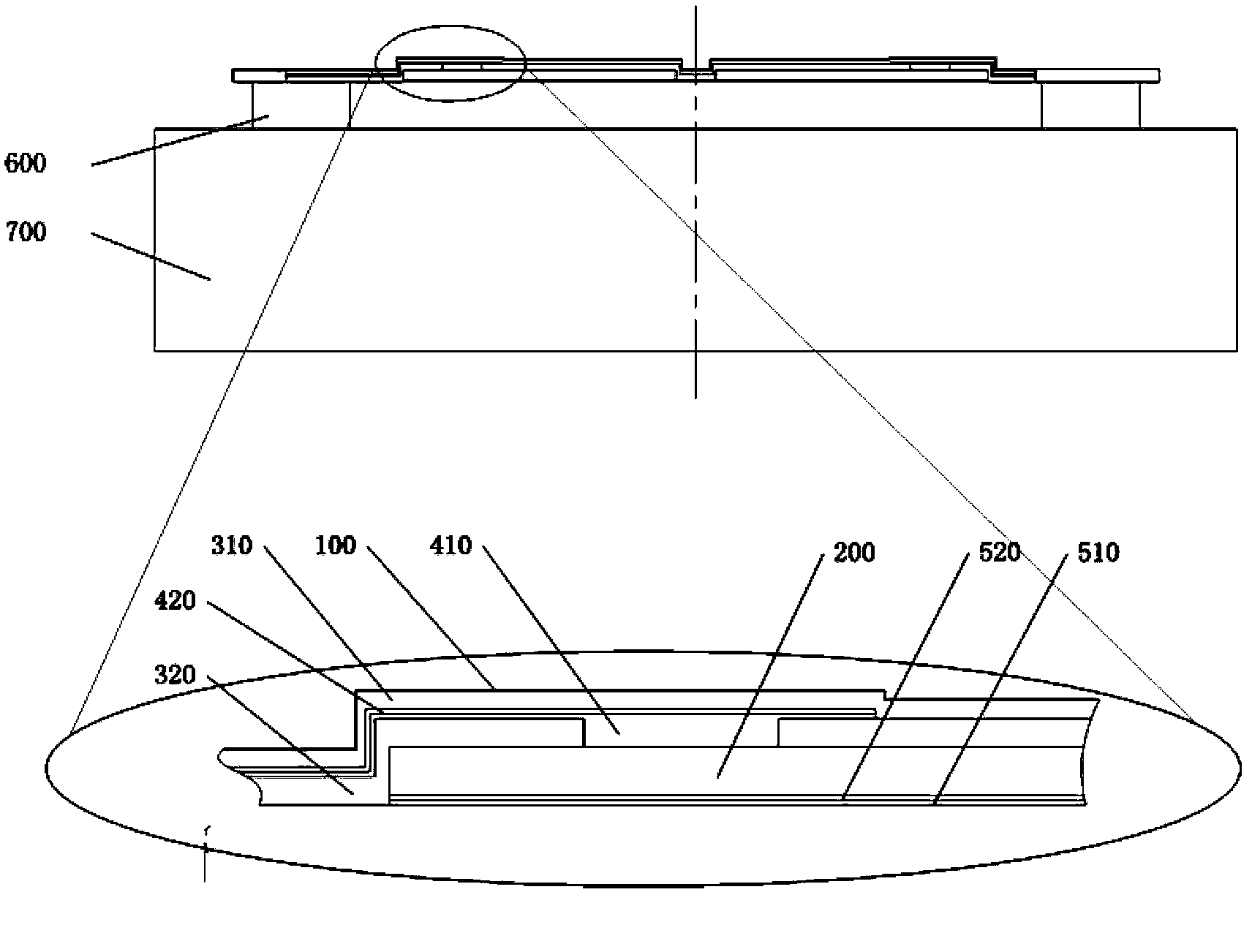

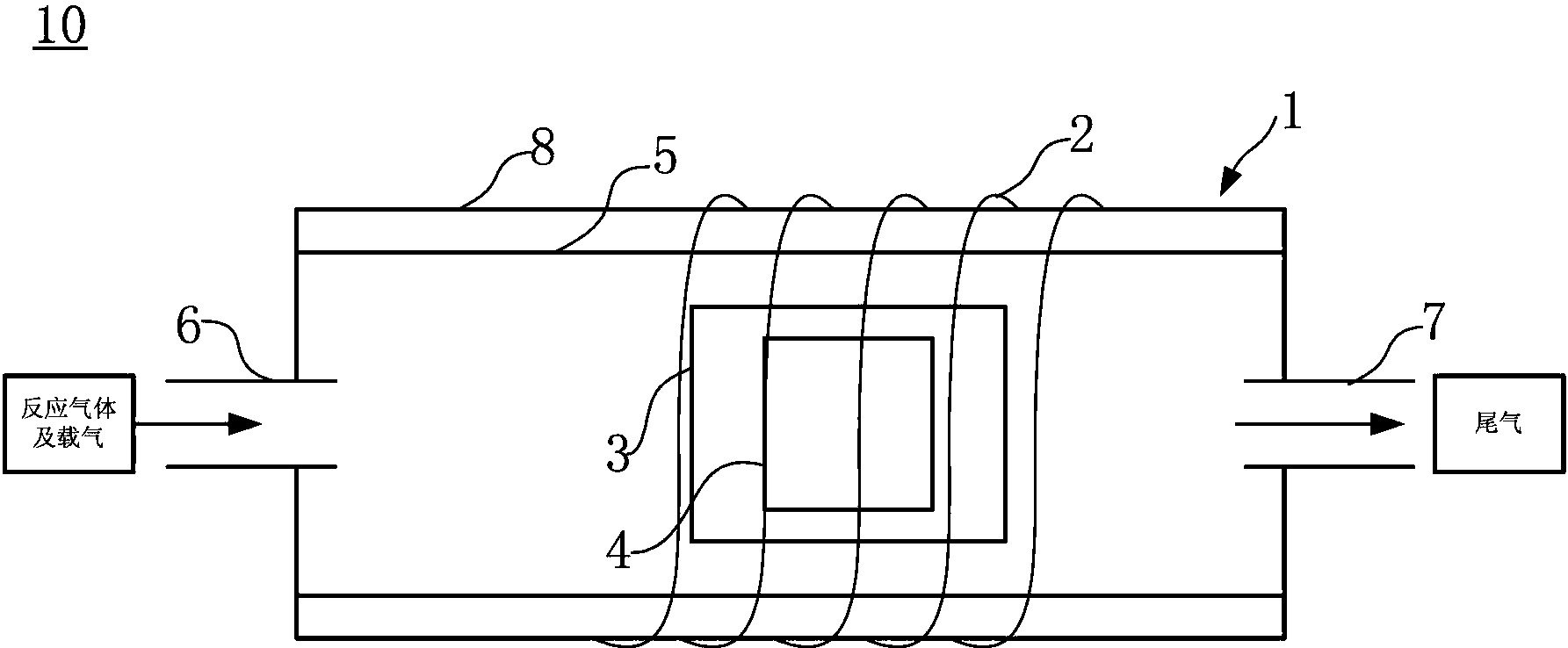

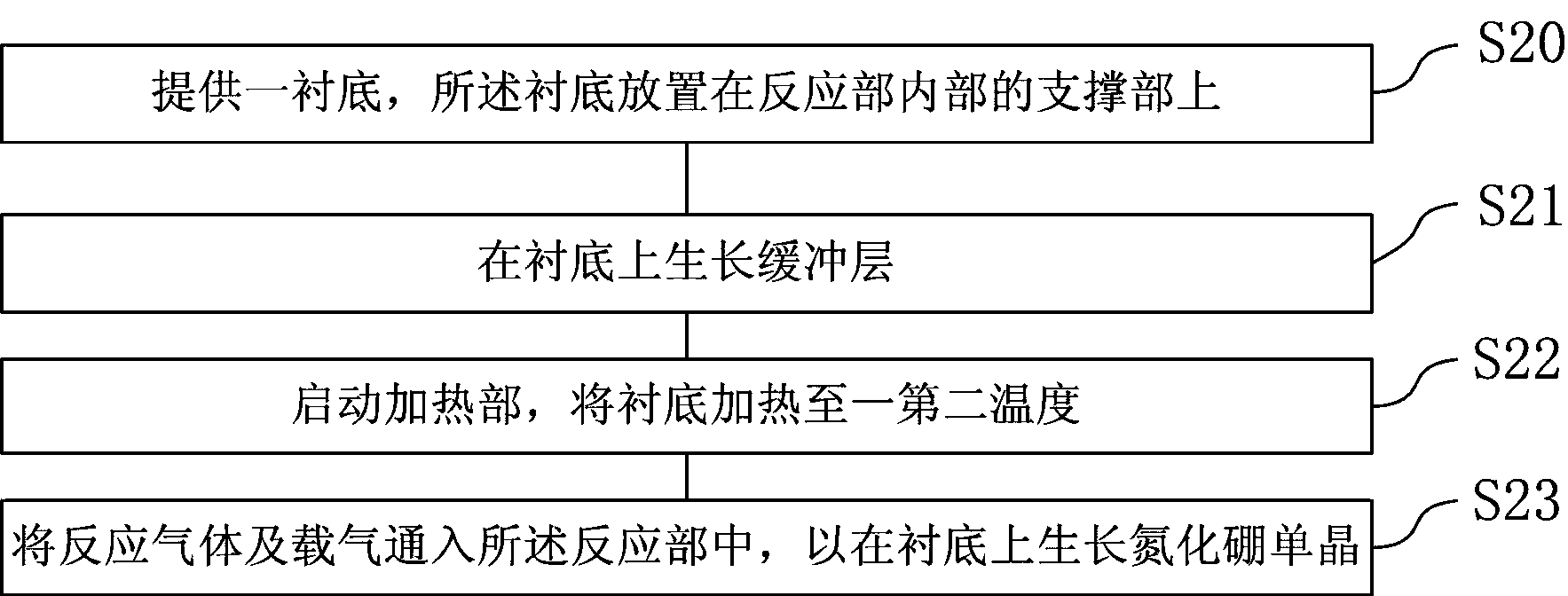

Device and method for preparing boron nitride single crystal

ActiveCN103541000AAvoid corrosionImprove lattice qualityPolycrystalline material growthFrom chemically reactive gasesBoron trichlorideSingle crystal

The invention provides a device and a method for preparing boron nitride single crystal. The method comprises the following steps: (1), providing a substrate and placing the substrate on a supporting part inside a reaction part; (2), starting a heating part, heating the substrate to a second temperature; (3), ventilating reaction gases as well as a carrier gas into the reaction part to grow the boron nitride single crystal on the substrate, wherein the reaction gases are boron trichloride and ammonia gas. The device and the method disclosed by the invention have the advantages that firstly, the boron trichloride and the ammonia gas are used as reaction gases to prepare the boron nitride single crystal, and boron nitride polycrystal or corundum is used as the material of the reaction part, so that corrosion of the boron trichloride to the reaction part is avoided; secondly, induction heating is adopted, so that the boron nitride single crystal with high crystal lattice quality can be obtained; thirdly, a vapor phase epitaxy technology is adopted, so that the born nitride single crystal can be grown on a lager substrate, the born nitride single crystal with large dimension can be prepared, and growth speed is quick; fourthly, production device is simple, used materials are easily available, cost is low, and the device and the method can be used for large-scale production.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

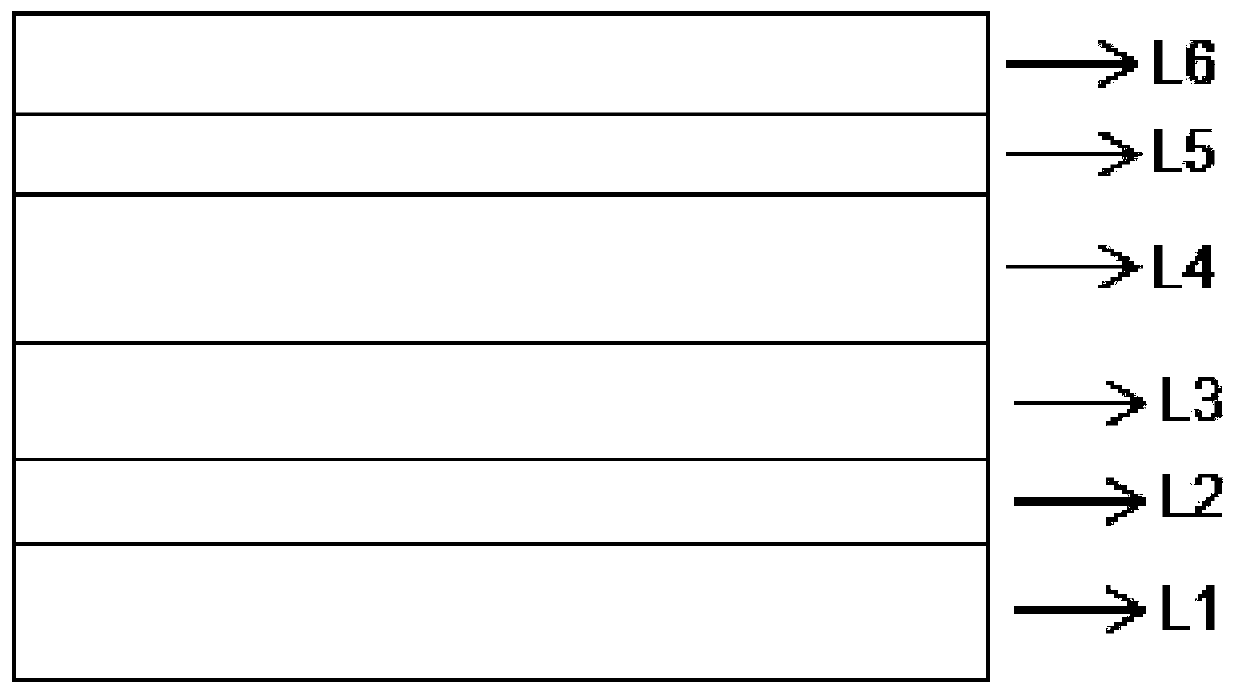

Epitaxial structure of gallium nitride device

PendingCN110993689AHigh electron mobilityImprove breakdown voltageTransistorSemiconductor/solid-state device manufacturingLeakage (electronics)Gallium nitride

The invention discloses an epitaxial structure of a gallium nitride device, belongs to the technical field of microelectronics, the epitaxial structure comprises a substrate, a low-temperature nucleating layer, a buffer layer, a high-resistance layer, a channel layer and a barrier layer, wherein the buffer layer is formed by circularly growing GaN<1> / SiN / GaN<2>, comprises a GAN1 crystal nucleus layer, a net-shaped structure SiN thin layer and a GAN2 filling layer, different growth modes are controlled mainly by controlling the total amount of NH3 in the growth environment of the three sub-layers. According to the HEMT device, the dislocation density of the material can be greatly reduced by circularly growing the GaN1 / SiN / GaN<2> buffer layer, and the lattice quality is improved, so that the characteristics of electron mobility, breakdown voltage, leakage current and the like of the HEMT device are improved.

Owner:西安电子科技大学芜湖研究院