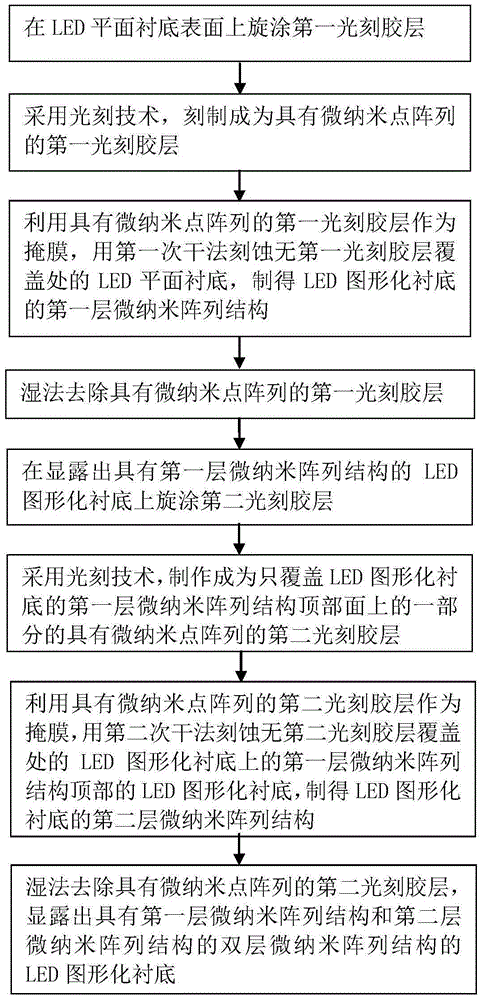

Manufacturing method for LED patterned substrate with double-layer micro-nano array structure

A patterned substrate and array structure technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems that GaN cannot be improved at the same time, so as to improve light extraction efficiency, optimize graphic morphology, and improve GaN lattice quality Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0062] In this embodiment, the method for fabricating an LED patterned substrate with a double-layer micro-nano array structure comprises the following steps:

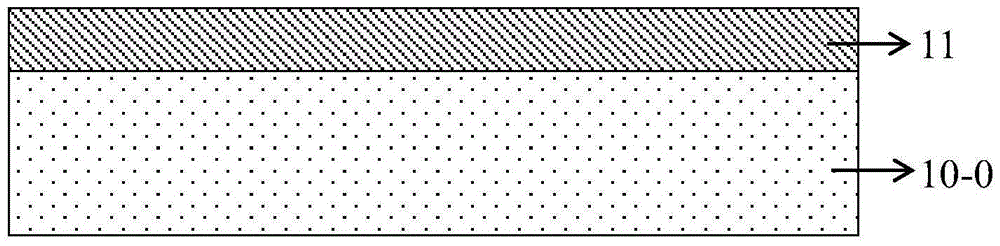

[0063] In the first step, spin-coat the first photoresist layer:

[0064] Spin-coating a photoresist layer on the surface of the planar sapphire LED substrate to form a first photoresist layer covering the surface of the sapphire LED substrate;

[0065] The second step is to make the first photoresist layer with micro-nano dot array:

[0066] Using nanoimprint photolithography technology, the first photoresist layer covering the surface of the sapphire LED substrate obtained in the first step is photolithographically made into a first photoresist layer with an array of micro-nano dots;

[0067] The third step, the first dry etching:

[0068] Using the first photoresist layer with micro-nano dot array obtained in the second step as a mask, use the first dry etching to etch the sapphire LED substrate without the covera...

Embodiment 2

[0081] The method for manufacturing an LED patterned substrate with a double-layer micro-nano array structure in this embodiment, the steps are:

[0082] In the first step, spin-coat the first photoresist layer:

[0083] Spin-coating a photoresist layer on the surface of the planar silicon carbide LED substrate to form a first photoresist layer covering the surface of the silicon carbide LED substrate;

[0084] The second step is to make the first photoresist layer with micro-nano dot array:

[0085] Using the photolithography technology of laser holographic interference exposure, the first photoresist layer covering the surface of the silicon carbide LED substrate obtained in the first step is photolithographically made into a first photoresist layer with an array of micro-nano dots;

[0086] The third step, the first dry etching:

[0087] Using the first photoresist layer with micro-nano dot array obtained in the second step as a mask, use the first dry etching to etch the...

Embodiment 3

[0100] A method for manufacturing an LED patterned substrate with a double-layer micro-nano array structure, the steps are:

[0101] In the first step, spin-coat the first photoresist layer:

[0102] Spin-coating a photoresist layer on the surface of the planar gallium nitride LED substrate to form a first photoresist layer covering the surface of the gallium nitride LED substrate;

[0103] The second step is to make the first photoresist layer with micro-nano dot array:

[0104] Using the photolithography technology of nanosphere self-assembly method, the first photoresist layer covering the surface of the gallium nitride LED substrate obtained in the first step is photolithographically made into the first photoresist layer with a micro-nano dot array;

[0105] The third step, the first dry etching:

[0106] Using the first photoresist layer with micro-nano dot arrays obtained in the second step as a mask, the gallium nitride LED substrate without the coverage of the first ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More