Patents

Literature

77results about How to "Promotes epitaxial growth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

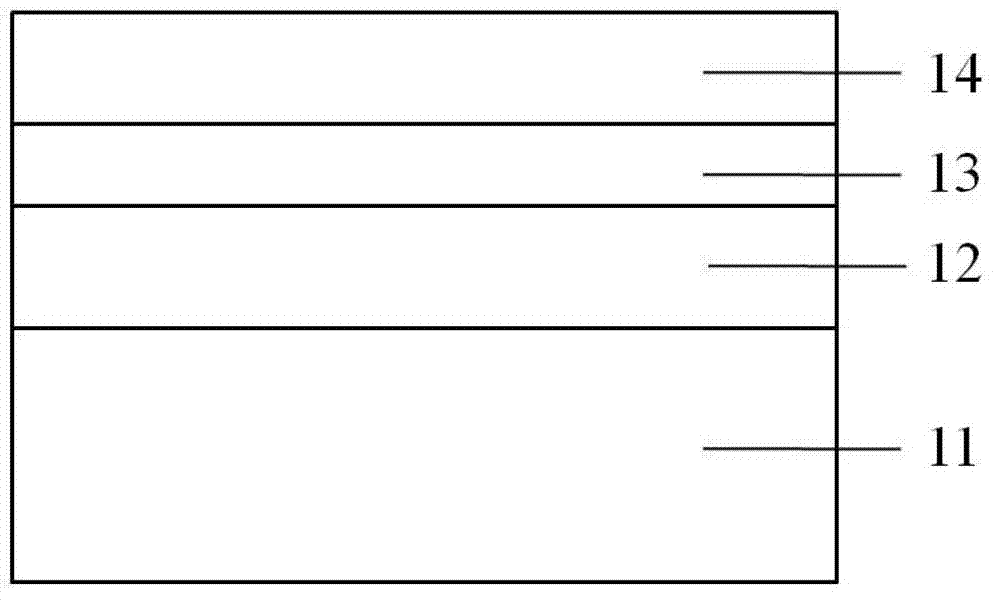

Nitride LED epitaxial wafer structure based on copper substrate and manufacturing method thereof

InactiveCN104538526AImprove crystal qualityNitride Epitaxial Growth of High Crystal QualitySemiconductor devicesOptical propertyNitride

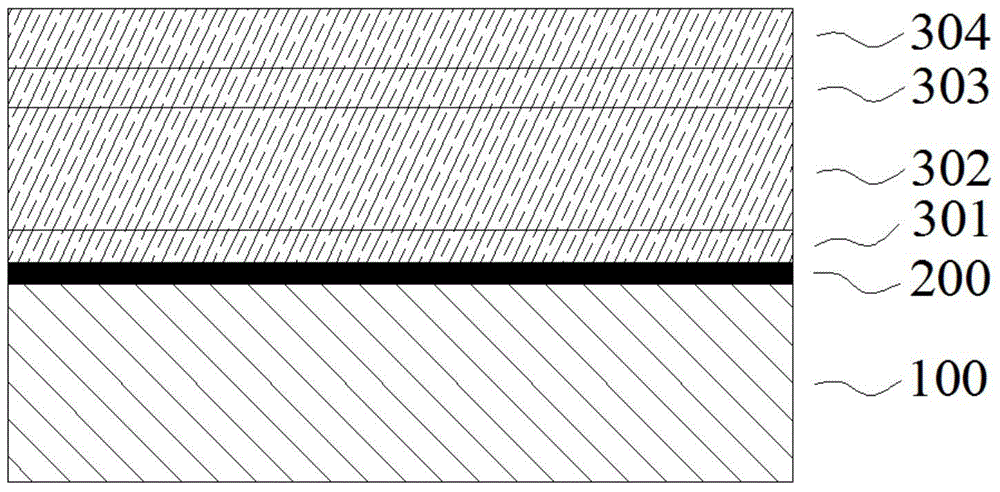

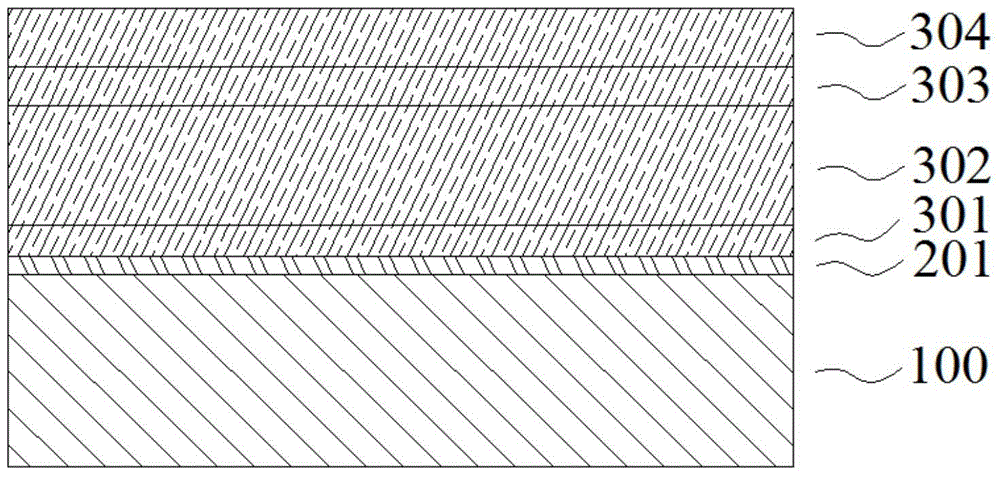

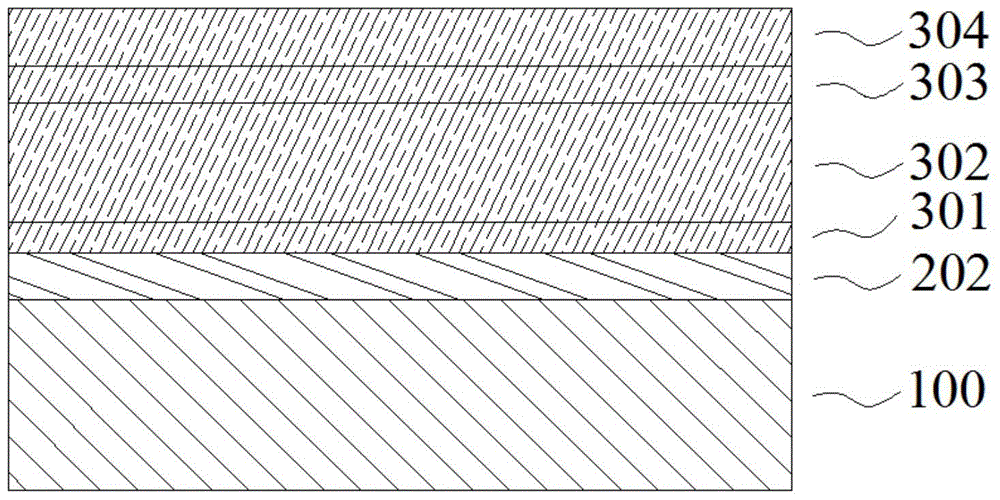

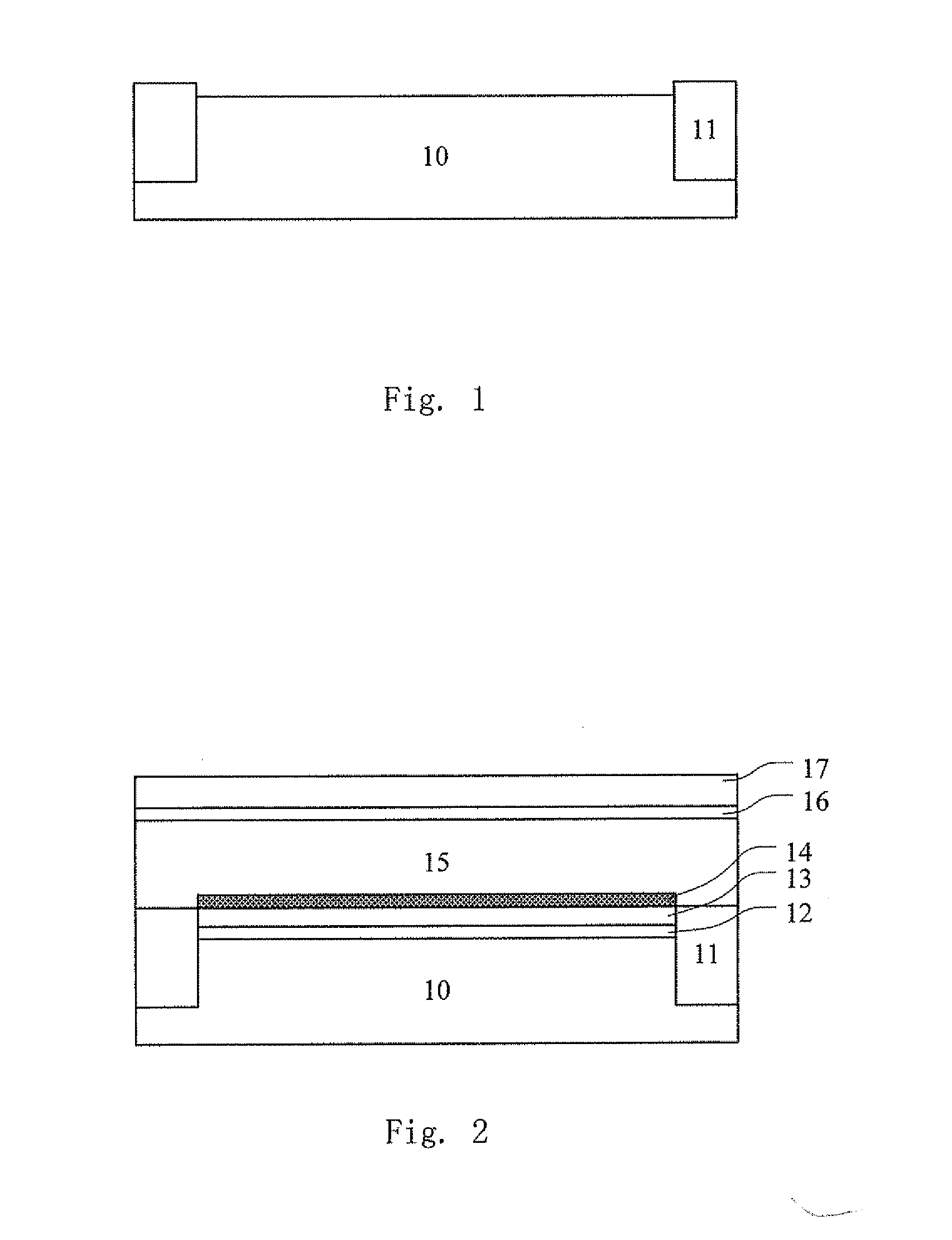

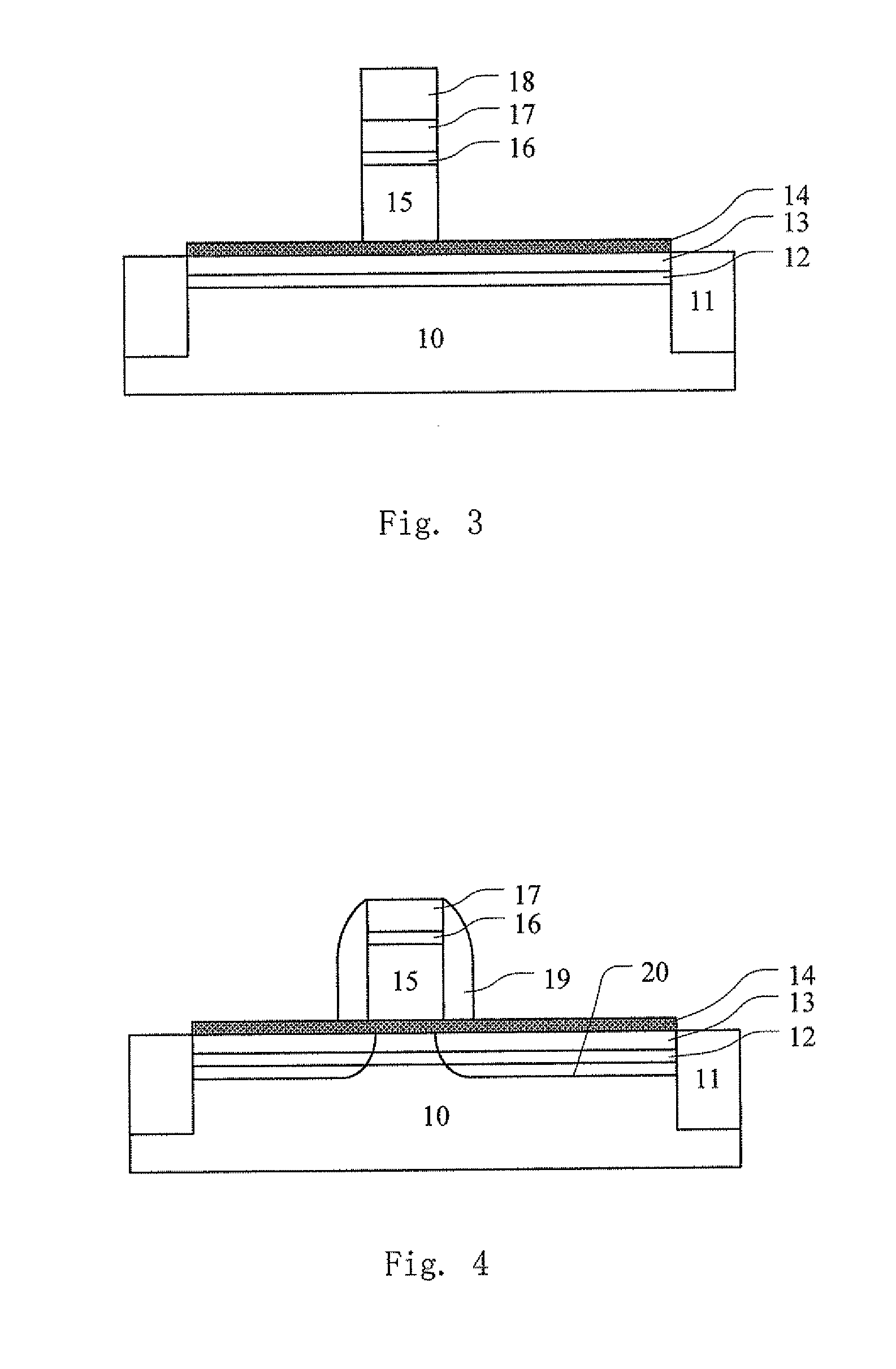

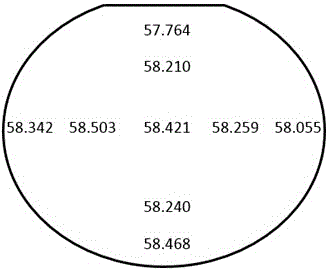

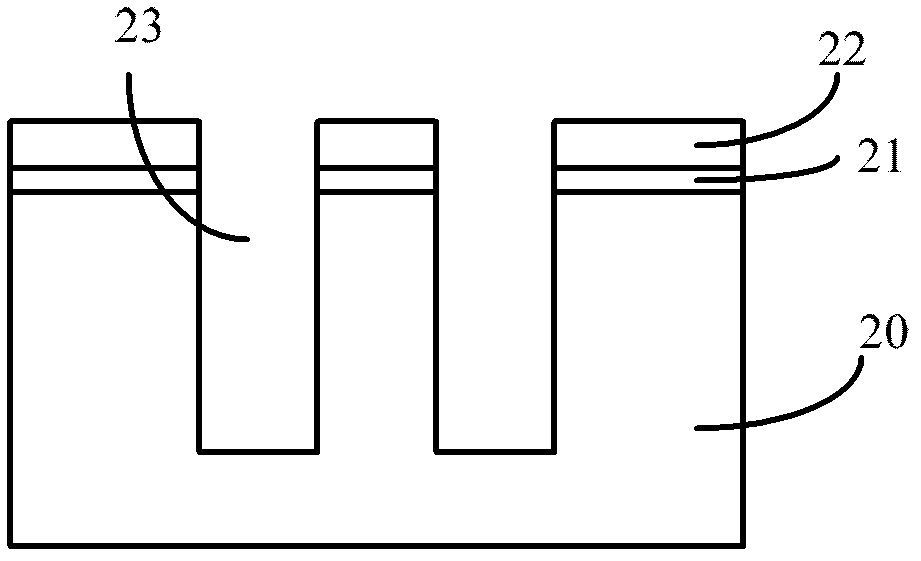

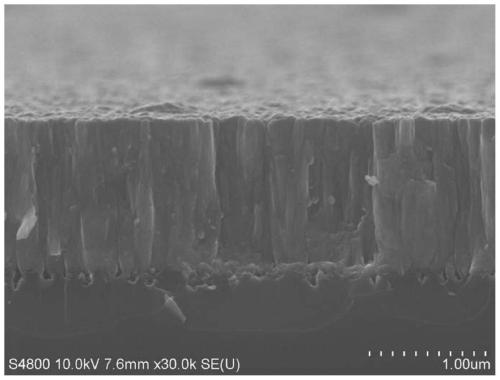

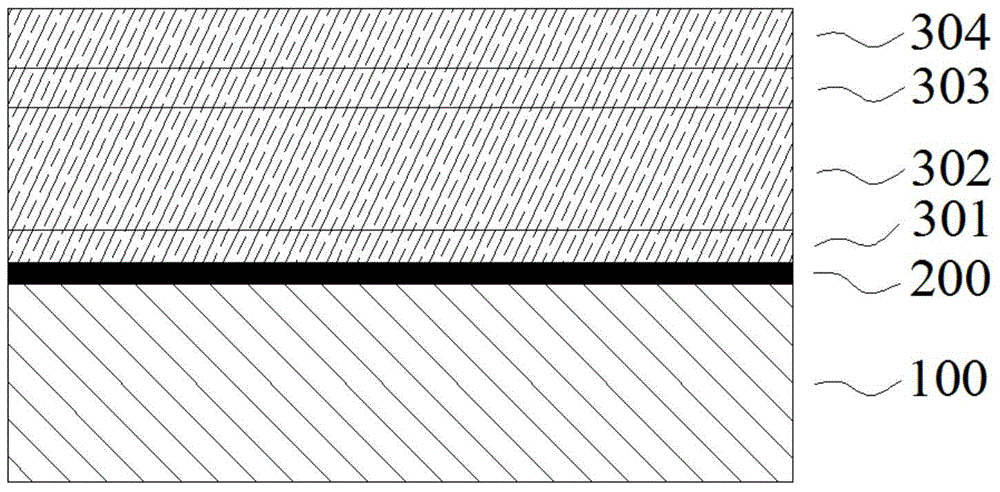

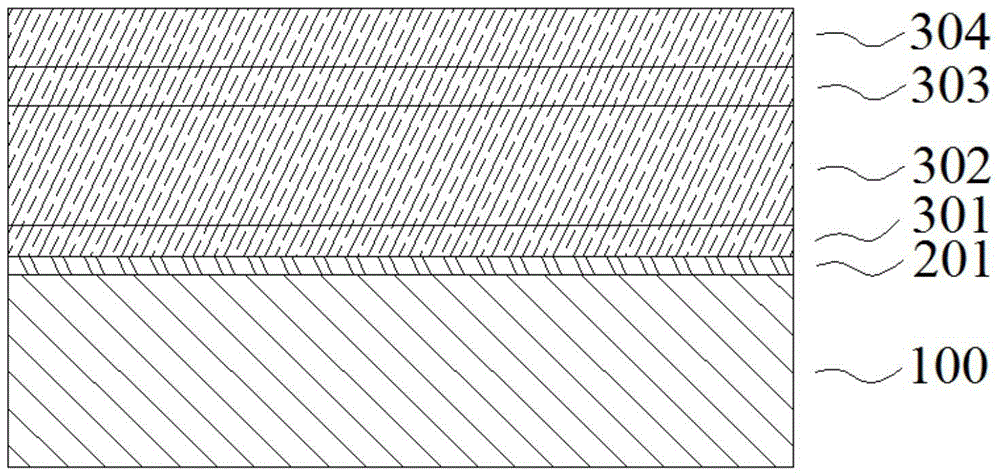

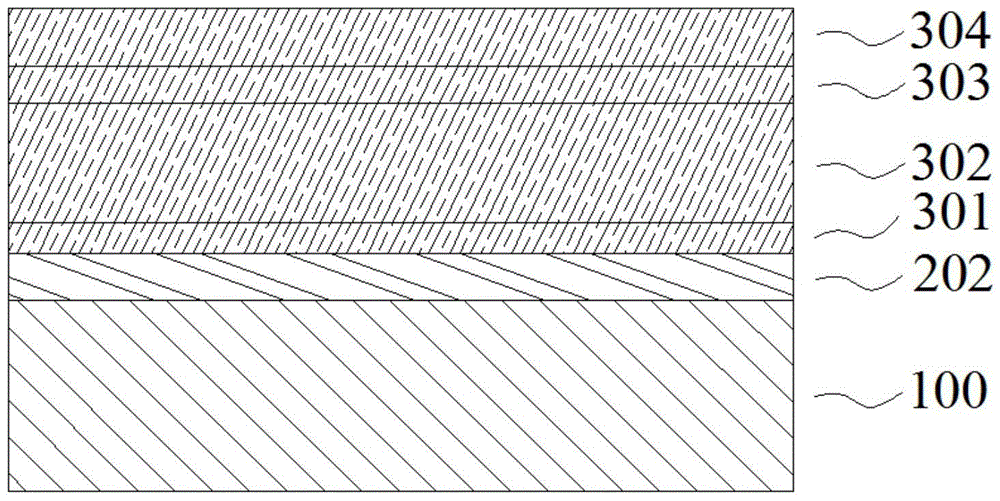

The invention relates to a nitride LED epitaxial wafer structure based on a copper substrate and a manufacturing method of the nitride LED epitaxial wafer structure. The nitride LED epitaxial wafer structure based on the copper substrate comprises the copper substrate, a two-dimensional derived film and a nitride epitaxial layer. The two-dimensional derived film is located between the copper substrate and the nitride epitaxial layer and is attached to the surface of the copper substrate. The nitride epitaxial layer is attached to the two-dimensional derived film. The manufacturing method comprises the steps that one or two layers of two-dimensional derived films are manufactured on the copper substrate, and the nitride epitaxial layer is grown on the copper substrate with the two-dimensional derived films. By the adoption of the nitride LED epitaxial wafer structure based on the copper substrate, high-crystalline-quality nitride epitaxial growth can be conducted on the copper substrate, cost is reduced, and the optical property, the electrical property and the thermal property of a device are improved.

Owner:江苏巨晶新材料科技有限公司

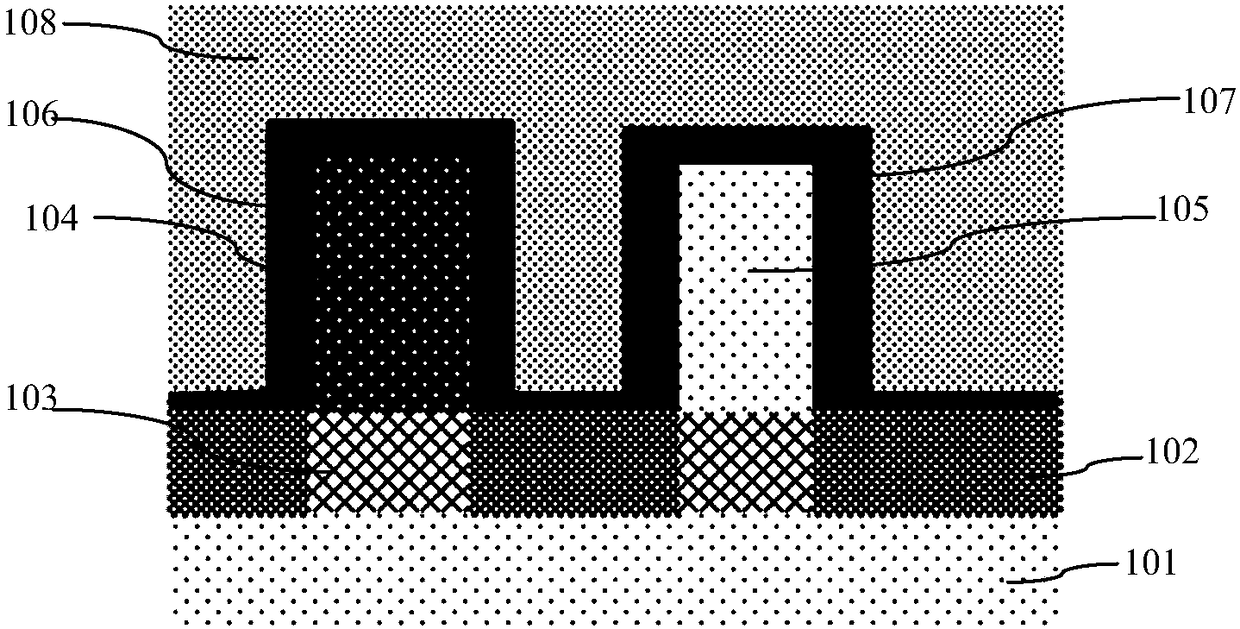

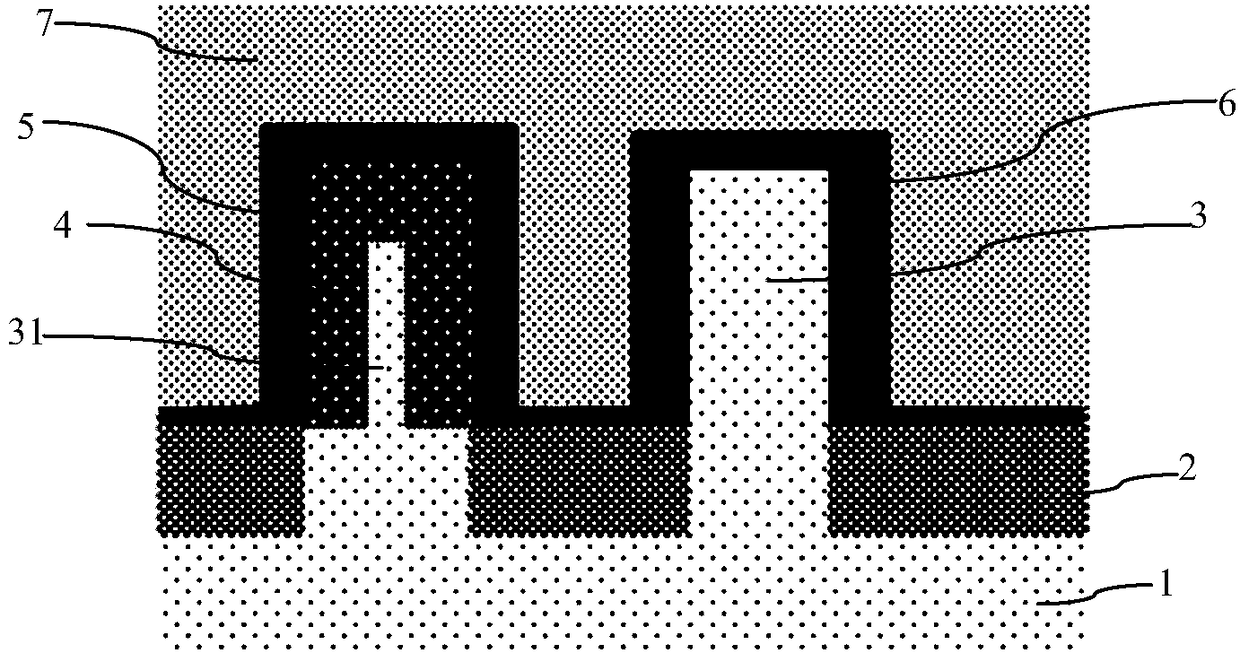

Semiconductor device and method of fabricating the same

ActiveUS20110303951A1Increase currentReduce power consumptionTransistorSemiconductor/solid-state device manufacturingPower semiconductor devicePower flow

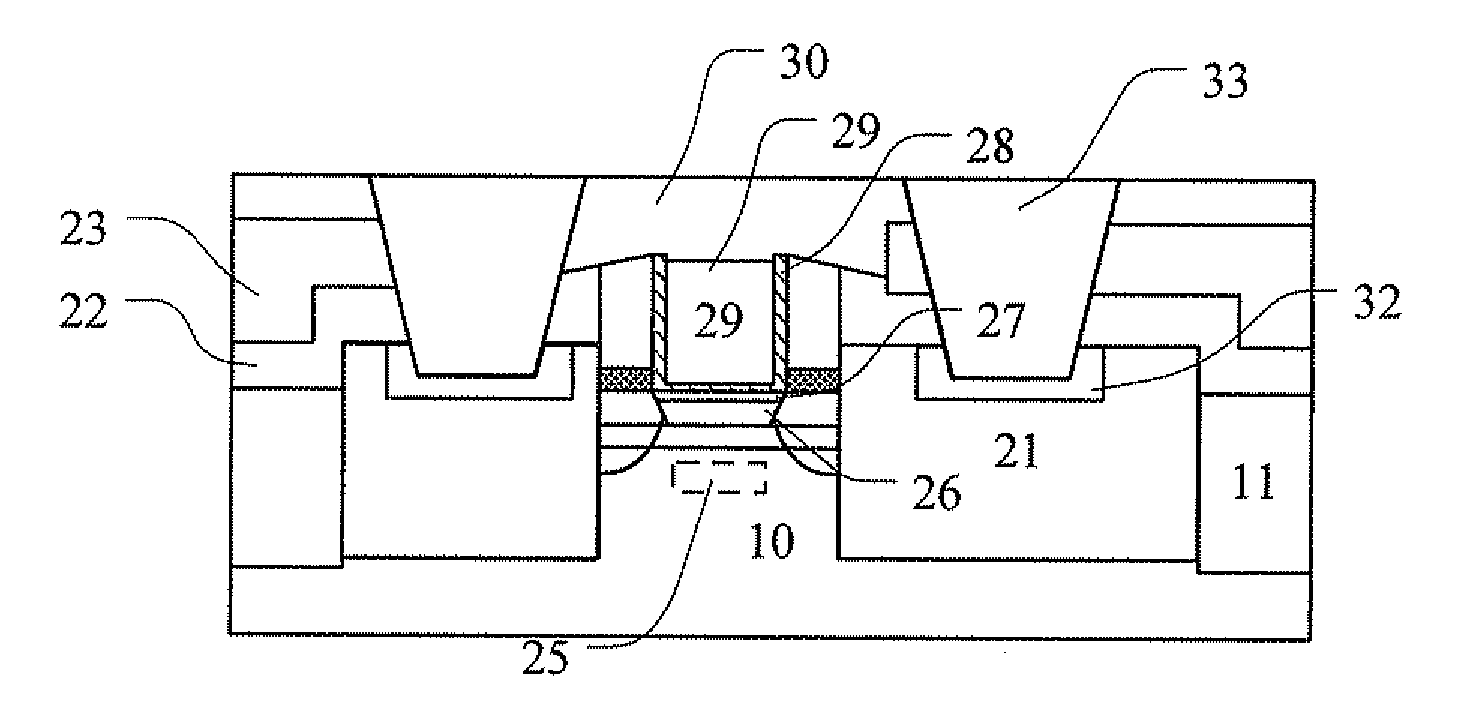

The present application discloses a semiconductor device and a method for manufacturing the same. The semiconductor device comprises a semiconductor substrate; a first semiconductor layer on the semiconductor substrate; a second semiconductor layer surrounding the first semiconductor layer; a high k dielectric layer and a gate conductor formed on the first semiconductor layer; source / drain regions formed in the second semiconductor layer, wherein the second semiconductor layer has a slant sidewall in contact with the first semiconductor layer. The semiconductor device has an increased output current, an increased operating speed, and a reduced power consumption due to the channel region of high mobility.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for preparing thick epitaxial layer on thin sb substrate for VDMOS device

ActiveCN106128938AImprove processing yieldPromotes epitaxial growthSemiconductor/solid-state device manufacturingSlip lineHydrogen

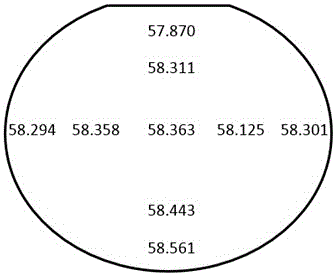

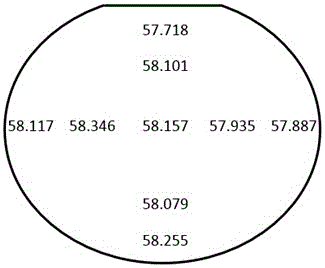

The invention relates to a method for preparing a thick epitaxial layer on a thin sb substrate for a VDMOS device. The method comprises: scale values of nine groups of adjusting rods arranged below a graphite pedestal of an epitaxial furnace are set respectively; the epitaxial furnace pedestal is processed by etching and polishing by using hydrogen chloride HC1 gas under a high temperature; a silicon substrate sheet is installed in a pit of the epitaxial furnace pedestal and the surface of the silicon substrate is polished by using the HC1 gas; sweeping is carried out on the surface of the silicon substrate sheet by using high-flow hydrogen; a thin intrinsic epitaxial layer grows on the silicon substrate sheet; a doped epitaxial layer grows; after the thickens of the doped epitaxial layer reaches a predetermined thickness, cooling is carried out; and then thicknesses of nine testing points of the epitaxial wafer are measured, thereby obtaining an average thickness value and a uniformity value of a silicon epitaxial wafer. Therefore, good control of epitaxial growth of the thin 400-micron sb substrate is realized; the nonuniformity of the thickness is less than 0.5%; defects of slip line, edge breakage, and damage existence at the edge are overcome; and the requirements on the silicon epitaxial layer of the VDMOS device are met; and the processing yield of the device is improved.

Owner:CHINA ELECTRONICS TECH GRP NO 46 RES INST +1

Method for growing InGaAs film on GaAs substrate

InactiveCN102560634AEffectively filter dislocationsFacilitated releasePolycrystalline material growthFrom chemically reactive gasesPhysical chemistryThin membrane

The invention discloses a method for growing an InGaAs film on a GaAs substrate, which comprises the following steps of: (1) cleaning the GaAs substrate; (2) pre-processing the GaAs substrate; (3) deoxidizing; (4) growing a GaAs buffer layer; (5) growing a low-temperature single-layer In0.6Ga0.4As big-mismatch buffer layer; and (6) growing an In0.3Ga0.7As epitaxial film, wherein the In0.6Ga0.4As big-mismatch buffer layer and the In0.3Ga0.7As epitaxial film both can be prepared by using the molecular beam epitaxial growth or metal organic vapor deposition technology. Various defects caused by mismatch stress can be lowered by the big-mismatch buffer layer. The prepared In0.3Ga0.7As epitaxial layer has lower defect density. The method has the advantages of simple buffer layer structure, simple and convenient epitaxial growth process, low defect density of the In0.3Ga0.7As epitaxial film, high crystal quality and the like.

Owner:SOUTH CHINA UNIV OF TECH

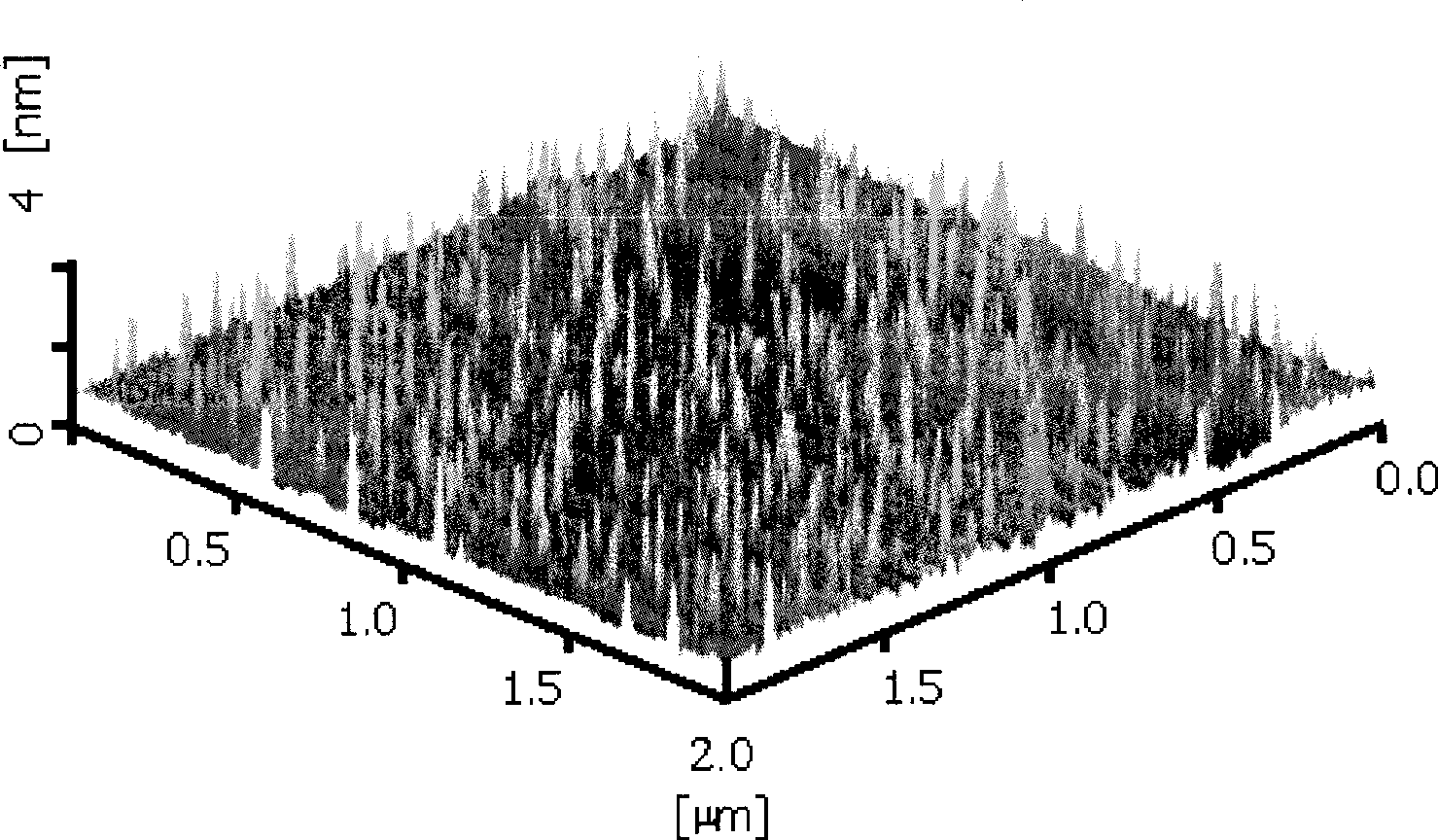

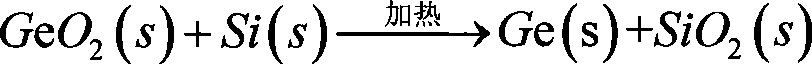

Preparation of germanium quantum point

InactiveCN101388324ASmall sizeHigh densityLaser detailsNanostructure manufactureHigh densityQuantum dot

A process for preparing germanium quantum dots is provided. The invention provides a process for preparing Ge quantum dot which can realize small size and high density without wetted layer, which comprises growing a SiGe alloy layer on a silicon substrate or a silicon substrate of an insulator, wherein Ge component is larger than 0, or is smaller than or equal to 0.5, then cleaning the SiGe alloy layer with at least one of three kinds of cleaning fluid in turn, forming an oxide layer on the surface of the SiGe alloy layer after the cleaning, wherein the oxide is the mixture of SiO2 and GeO2, then placing the SiGe alloy layer which is coated with the oxide layer into a vacuum cavity to heat up and deoxidize, thereby obtaining the Ge quantum dots. The heating temperature can be larger than the deoxidizing temperature, and is smaller than the fusing point of SiGe.

Owner:XIAMEN UNIV

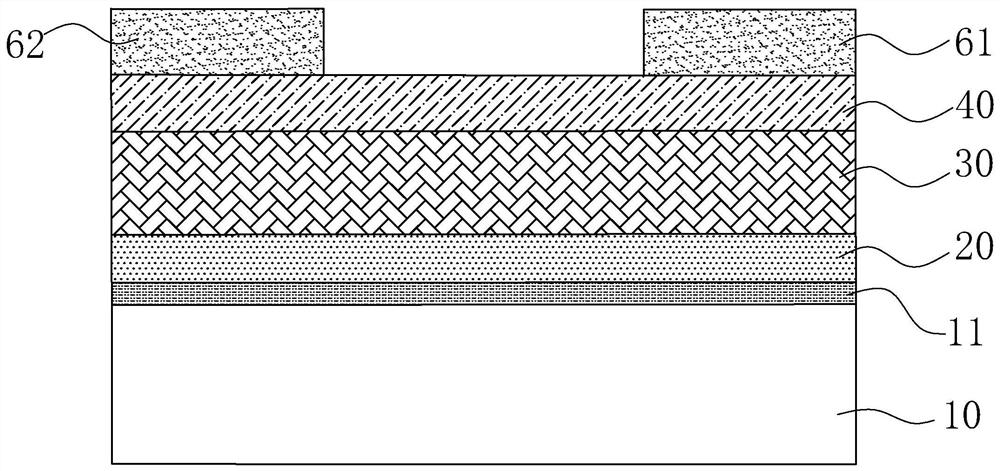

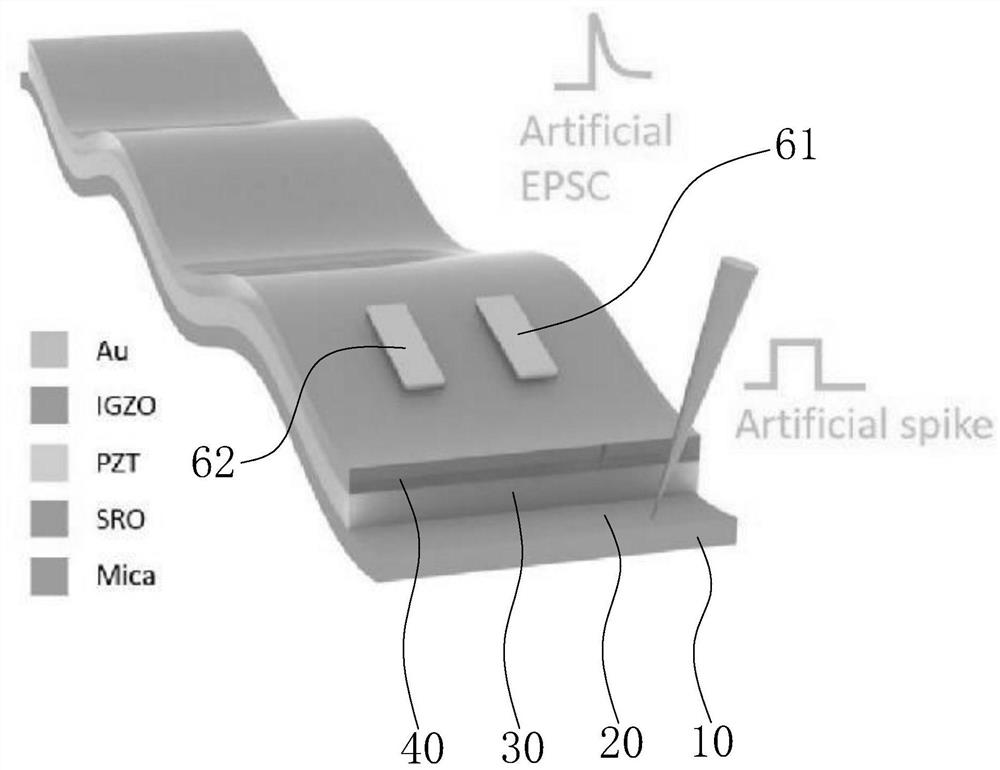

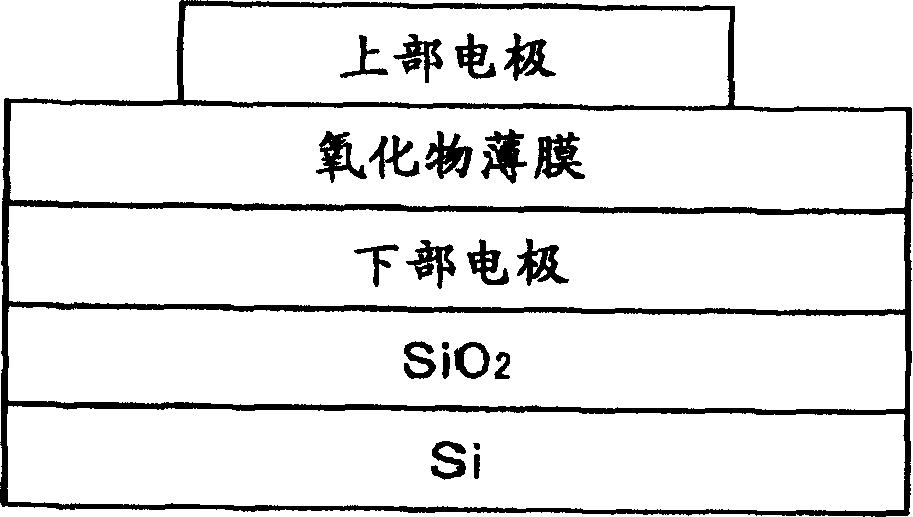

Inorganic synaptic transistor structure and manufacturing method thereof

PendingCN111739935AImproved leakage current resistanceEasy to operateSemiconductor/solid-state device manufacturingPhysical realisationGate dielectricBottom gate

The invention relates to an inorganic synaptic transistor structure and a manufacturing method thereof. The structure comprises a flexible substrate; a buffer layer formed on the substrate; a bottom gate electrode formed on the buffer layer; an epitaxial gate dielectric layer formed on the bottom gate electrode; a channel layer formed on the epitaxial gate dielectric layer; and a source electrodeand a drain electrode which are disposed on the channel layer. The manufactured synaptic transistor effectively overcomes the defects that the miniaturization and integration of the synaptic transistor adopting ionic liquid or solid electrolyte as a gate medium are difficult to achieve, the linearity and symmetry of a device are worse, and the synaptic transistor is not resistant to high temperature. The synaptic transistor prepared by the method has flexibility, bending resistance and high temperature resistance, the performance can still be kept basically unchanged under the bending condition or at 100 DEG C, and the energy consumption of each device in the learning process is only 10-30 pJ, which is beneficial to the practical application of the synaptic transistor in the field of high-precision artificial neuromorphic calculation.

Owner:SHENZHEN INST OF ADVANCED TECH

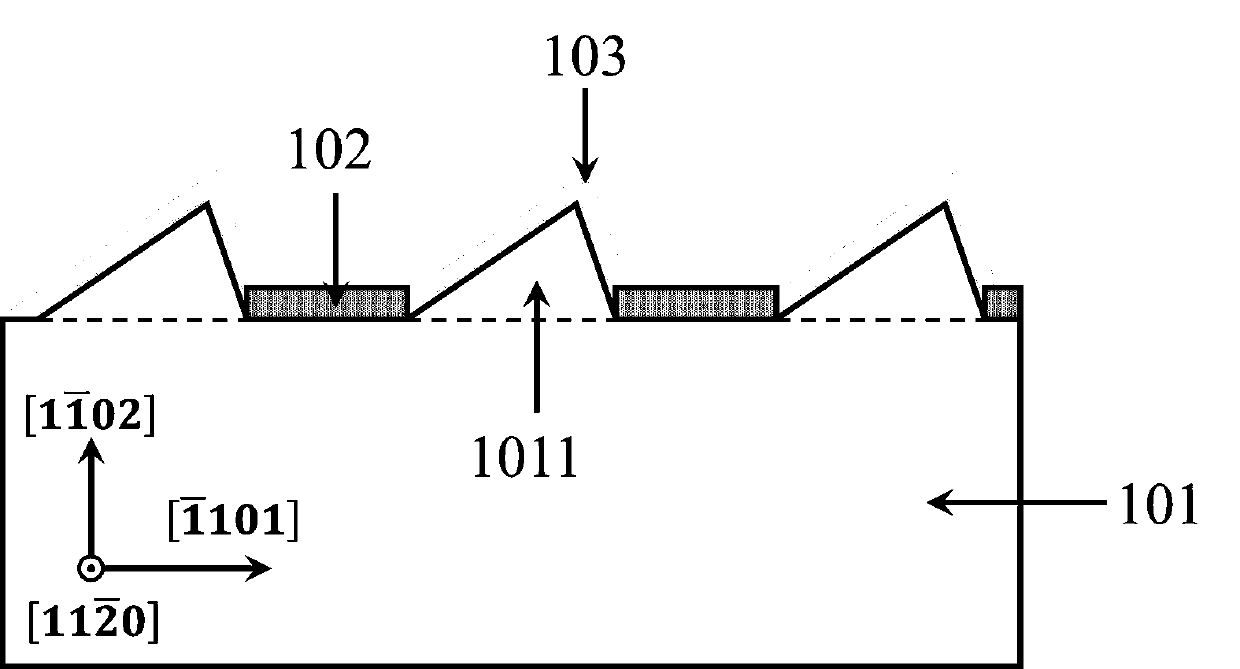

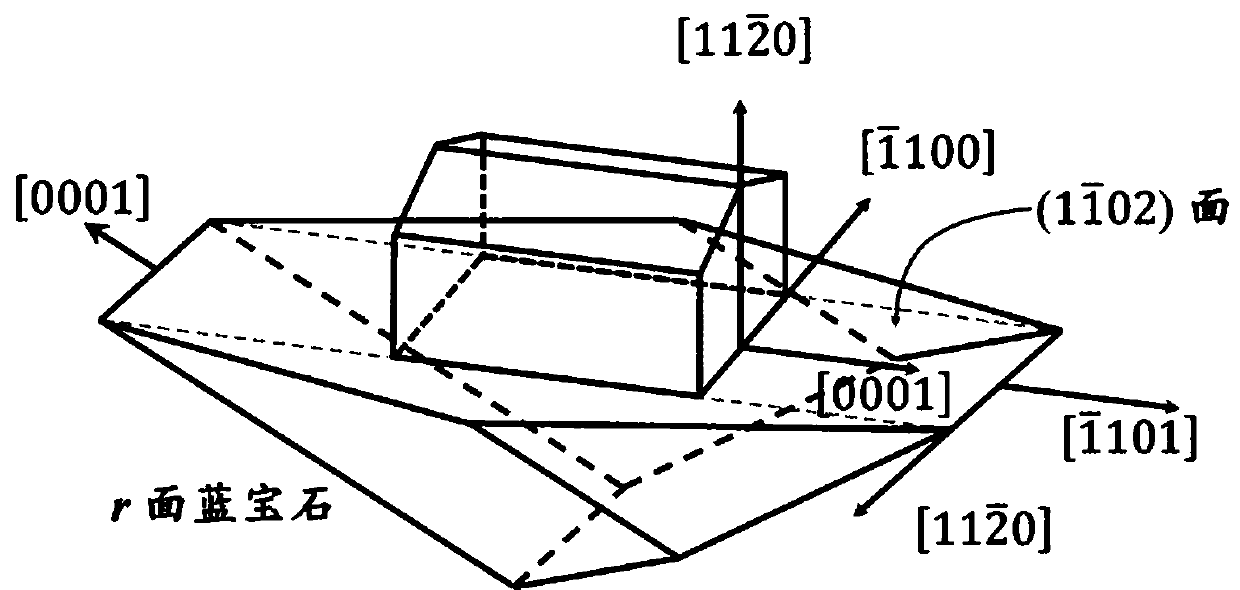

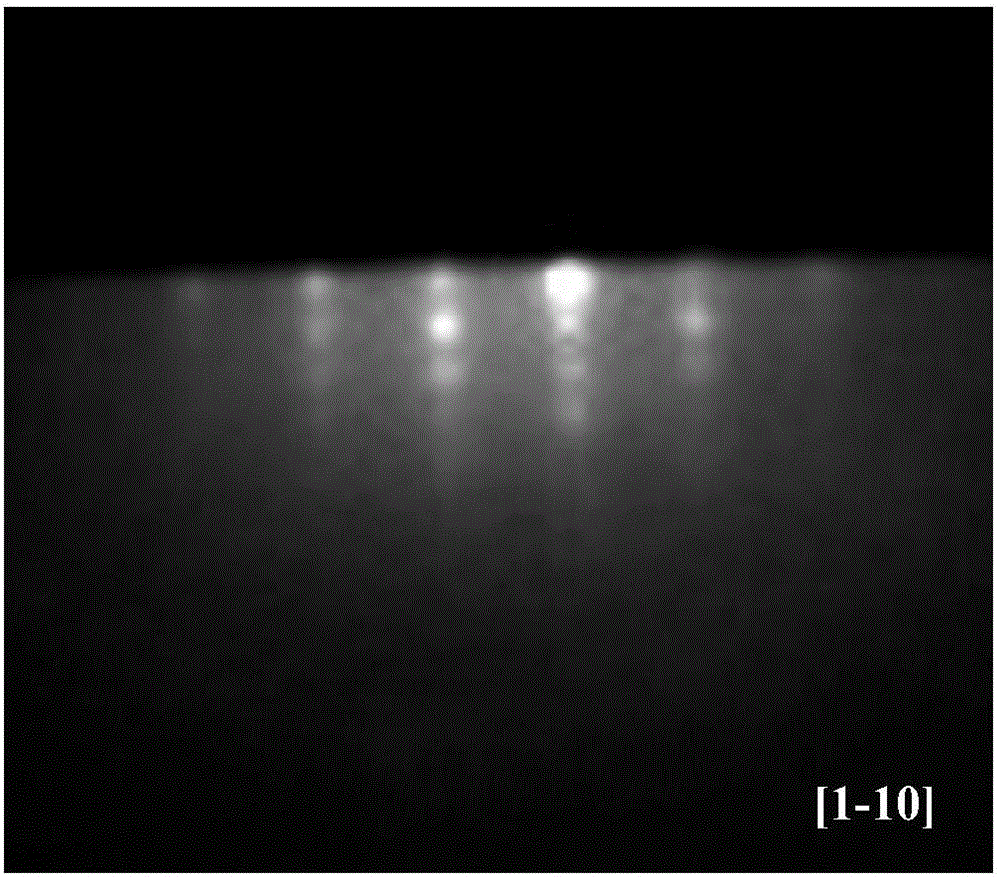

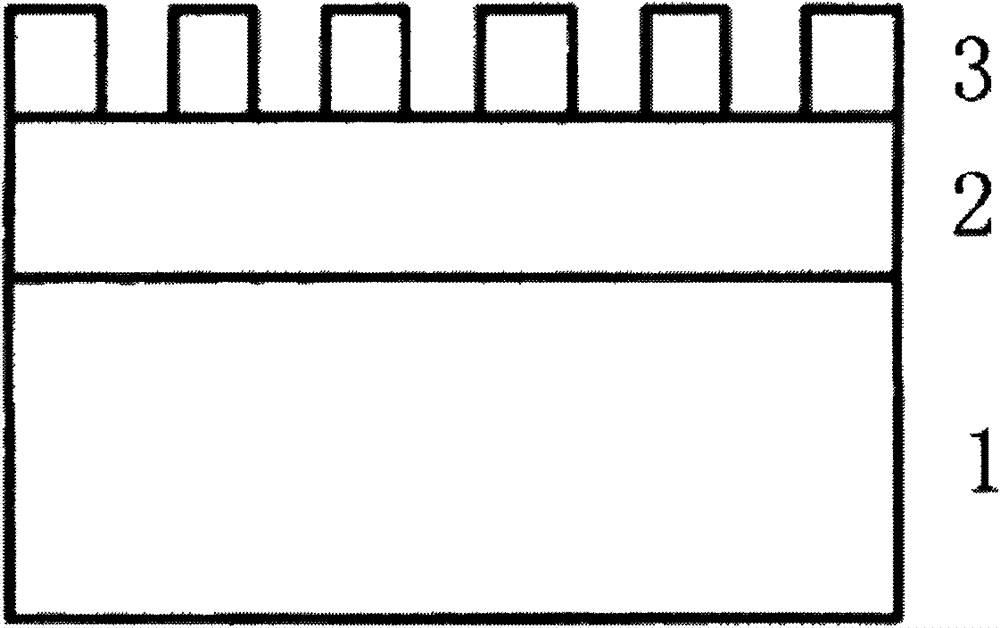

Non-polar patterned AlN/sapphire composite substrate and manufacturing method thereof

ActiveCN109545933AImprove crystal qualityReduce incorporationSemiconductor/solid-state device manufacturingSemiconductor devicesComposite substrateCrystal orientation

The invention discloses a non-polar patterned AlN / sapphire composite substrate and a manufacturing method thereof. The structure thereof comprises a r-plane patterned sapphire substrate, a sapphire pattern, a mask layer and an AlN covering layer. The sapphire pattern is a part of the r-plane patterned sapphire substrate, and is an asymmetric conical or pyramidal structure, that is, inclines towarda [1101] crystal orientation. The structure can effectively solve a problem that crystal quality is difficult to improve since growth rates along different directions are different during epitaxial growth of non-polar III-nitride. The AlN covering layer is formed by direct reaction with NH3 while the sapphire substrate is decomposed under high temperature in an NH3 atmosphere. The composite substrate provided by the invention can effectively reduce combination of O-containing impurities in an epitaxial growth process of the III-nitride, and can also obtain a dense high-quality non-polarity AlN covering layer on the surface of the sapphire substrate on the premise of not consuming an Al source, and has important significance on growing the high-quality non-polar III-nitrides and related devices on the substrate.

Owner:SOUTHEAST UNIV

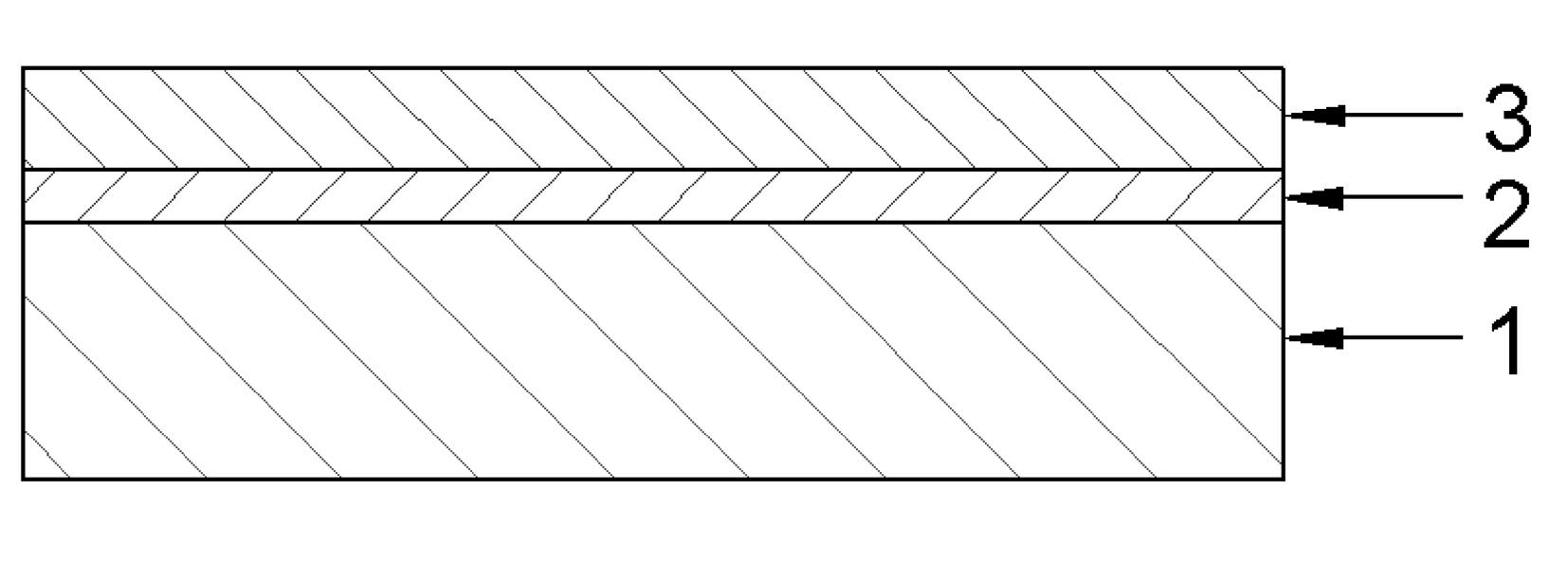

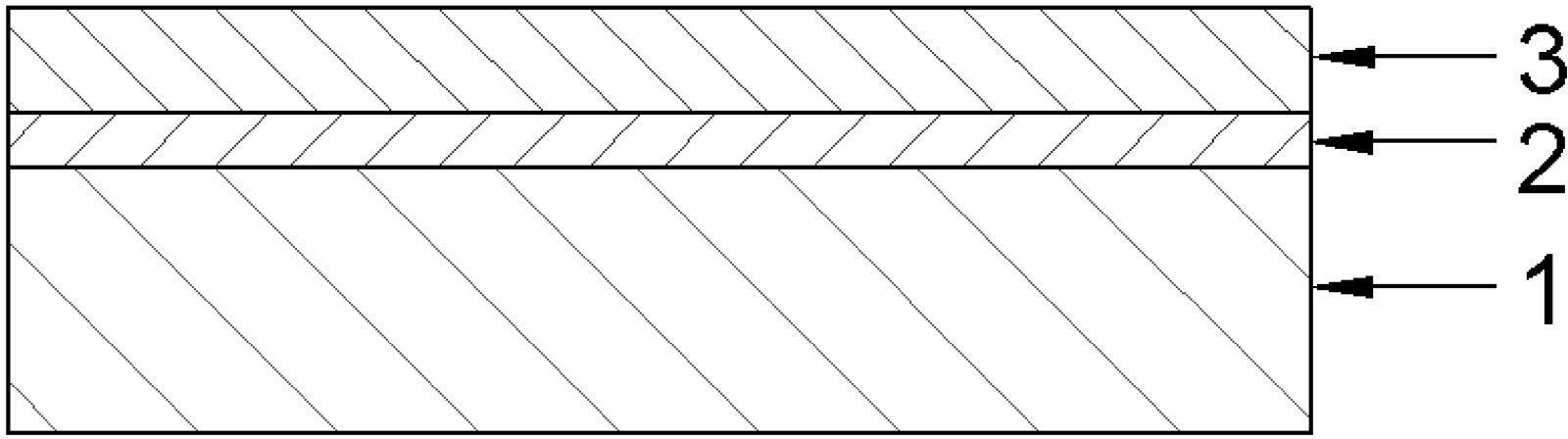

Coating for improving bioactivity of stainless-steel bone lamella and bone nail

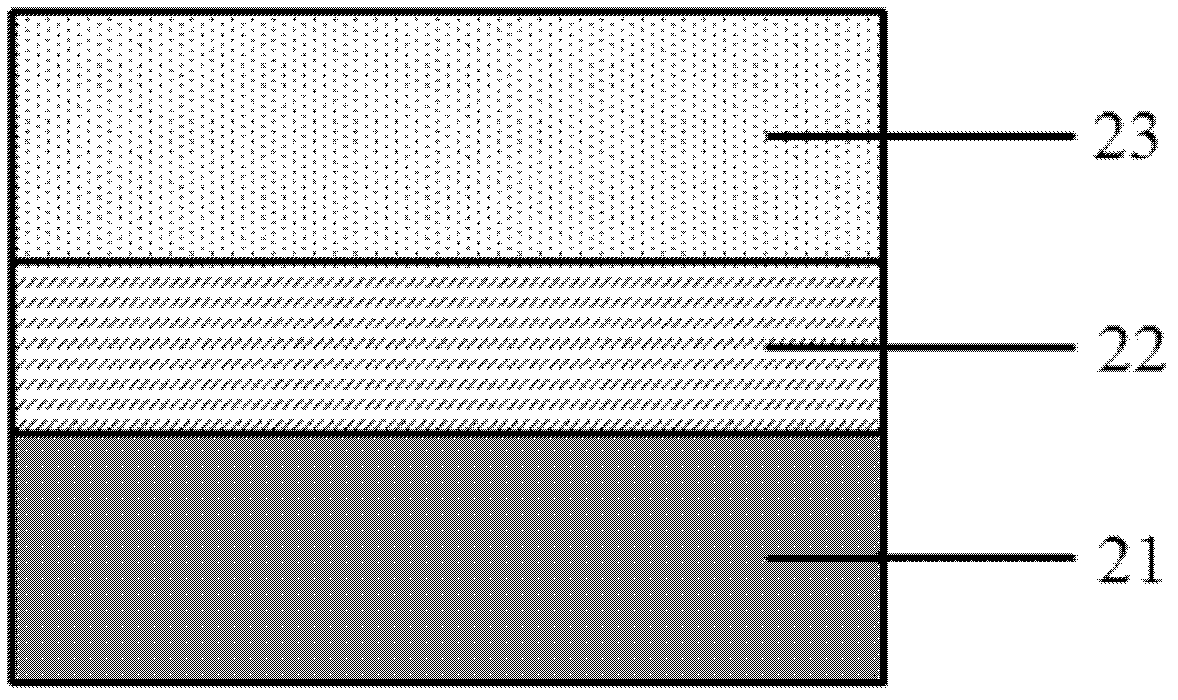

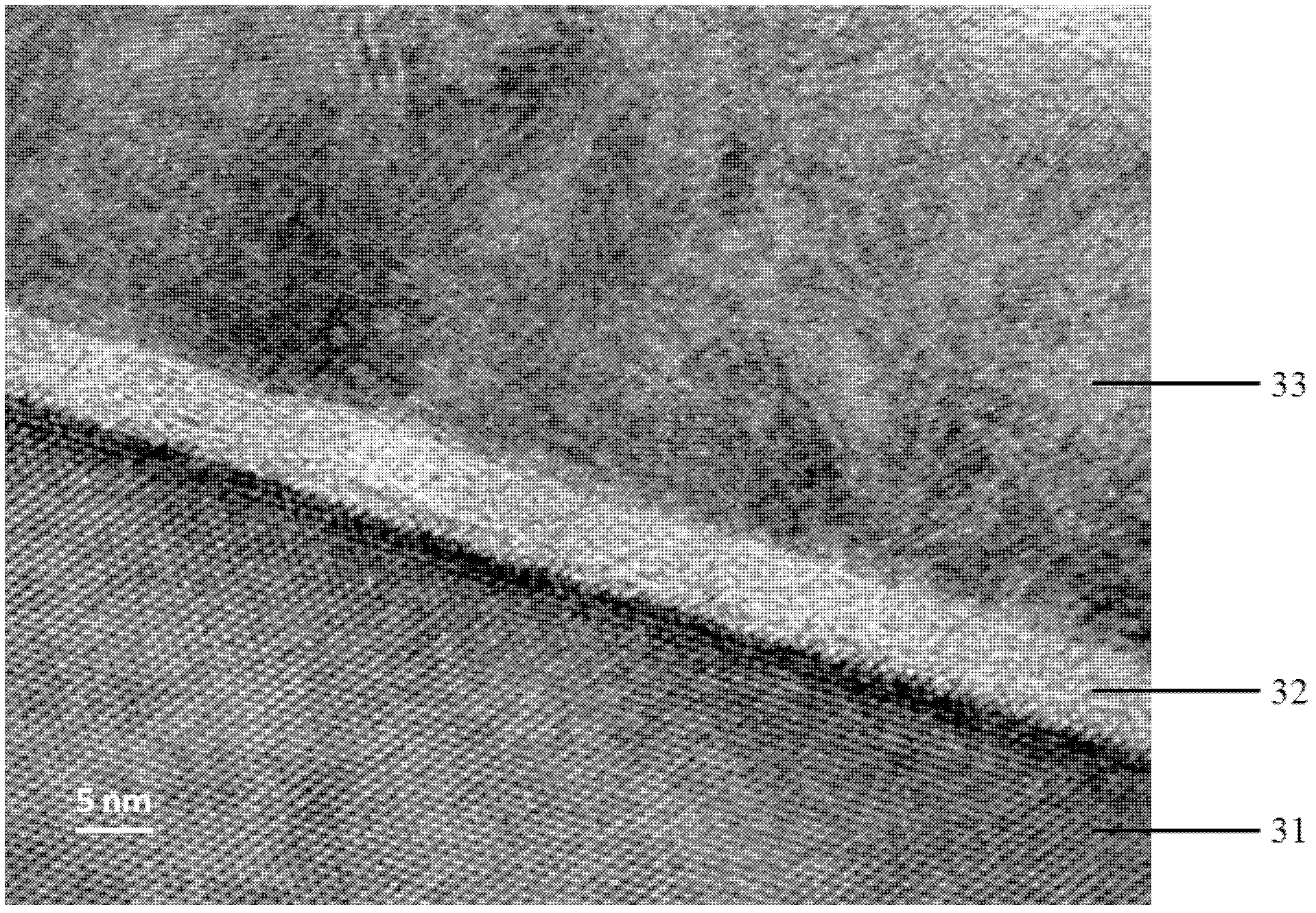

InactiveCN102580169AImprove bindingImprove biological activityVacuum evaporation coatingSputtering coatingMatrix nailBiocompatibility

The invention discloses a coating for improving bioactivity of a stainless-steel bone lamella and a bone nail. The Ti / TiB2 composite coating grows on the surface of a stainless-steel bone lamella and bone nail matrix (1), and the thickness of the Ti / TiB2 composite coating ranges from 500nm to 5mum; the inner layer of the composite coating, close to the bone lamella and bone nail matrix, is a pure-metal Ti layer (2) serving as a transition layer; and an external layer, namely a TiB2 layer (3), grows on the pure-metal Ti layer and serves as a function film layer. According to the invention, the pure-metal Ti layer grows on the surface of the bone lamella and bone nail matrix (1) by an ultrahigh vacuum magnetron sputtering method, and the TiB2 layer grows on the pure-metal Ti layer, so that the composite coating has better biocompatibility, frictional wear resistance and chemical stability, can effectively inhibit dissolution and seepage of toxic elements in stainless-steel matrix materials, and can reduce tissue reaction and aseptic loosening of the matrix, prolong the service life of the matrix and enhance the reliability of the matrix.

Owner:HUAIYIN INSTITUTE OF TECHNOLOGY

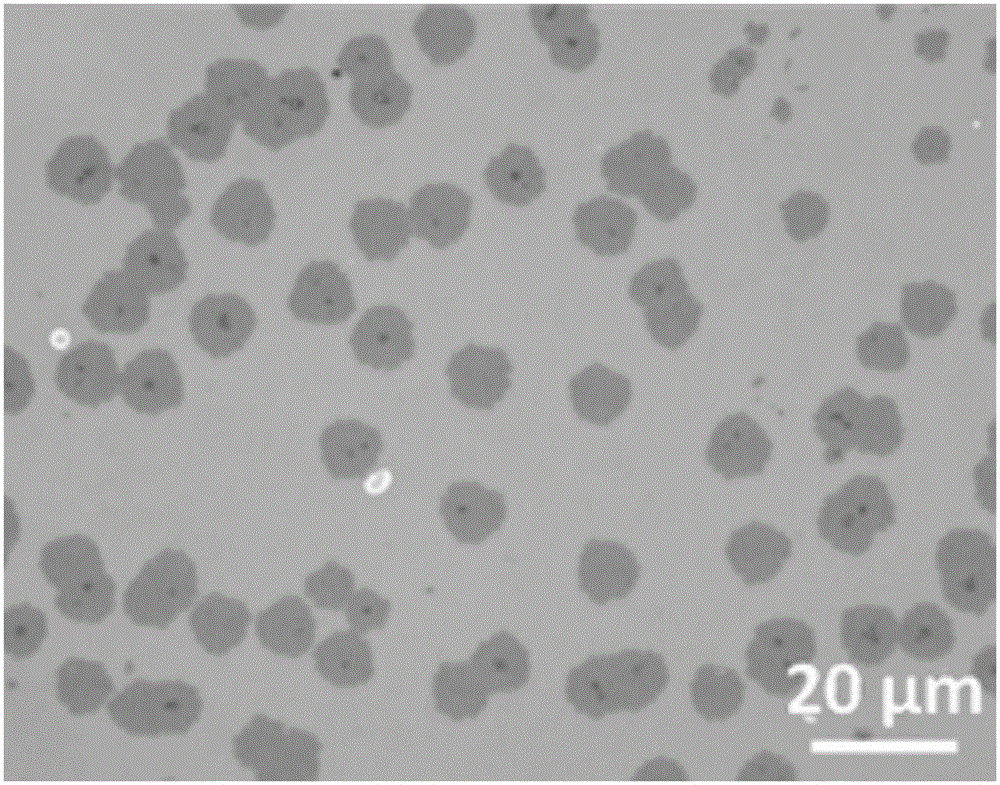

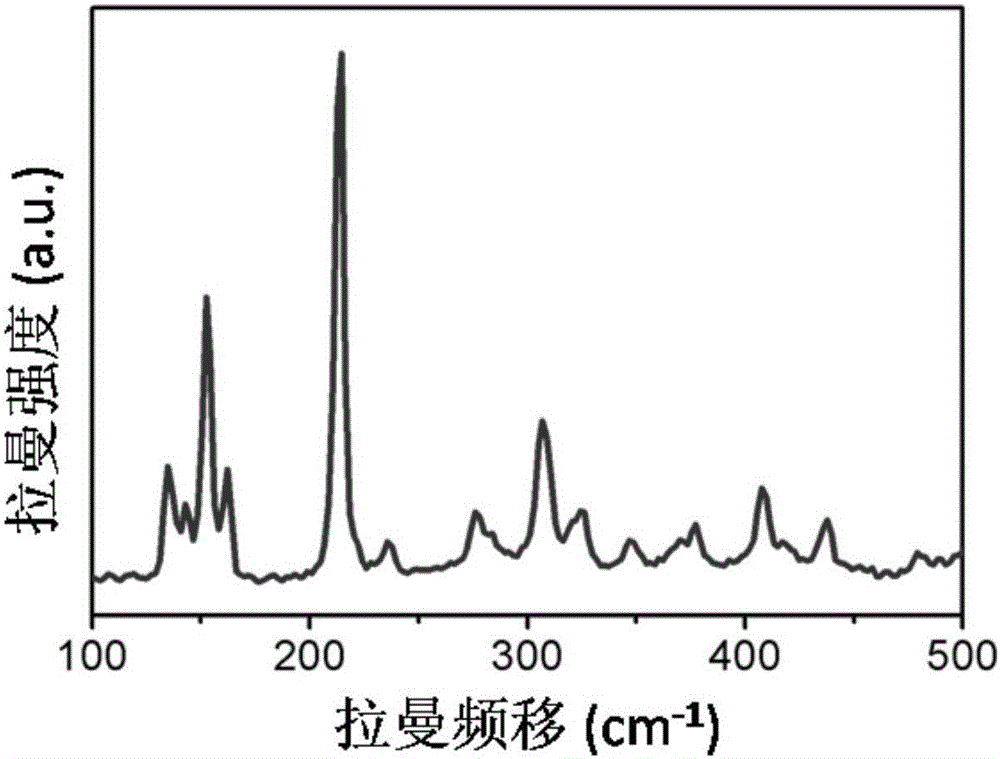

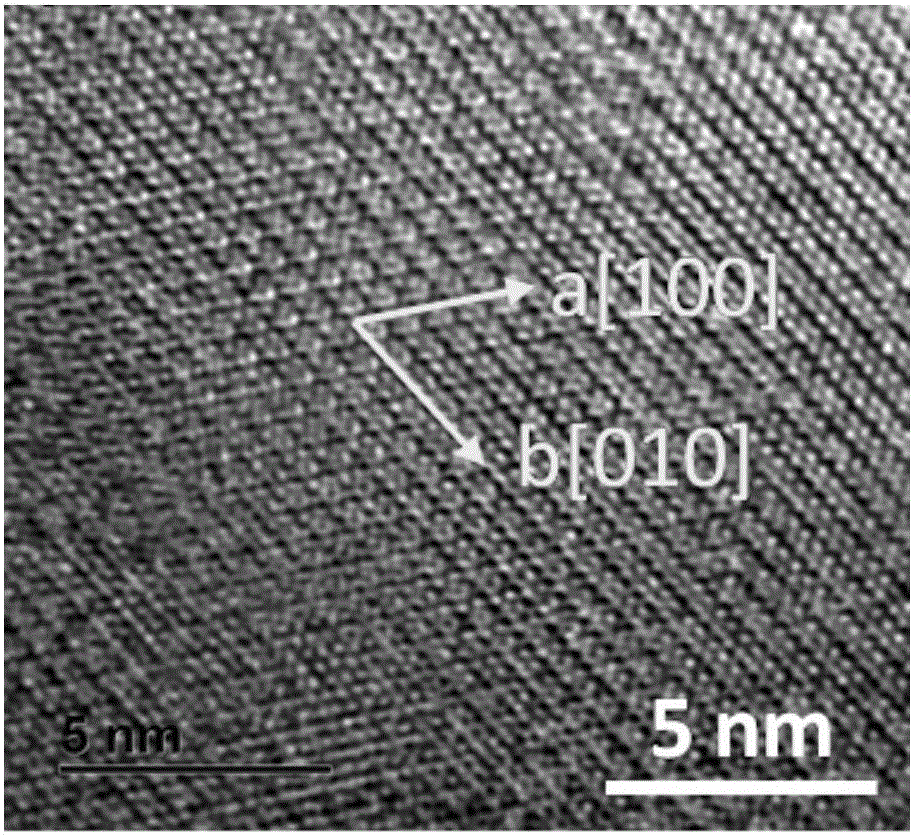

Method for preparing rhenium disulfide thin film through chemical vapor deposition

InactiveCN105839072AImprove growth efficiencyPromotes epitaxial growthChemical vapor deposition coatingRheniumArgon atmosphere

The invention discloses a method for preparing a rhenium disulfide thin film through chemical vapor deposition. According to the method, a two-element eutectoid alloy formed by a mixture of rhenium powder and tellurium powder is used as a rhenium source, powdered sulfur is used as a sulfur source, mica is used as a growth substrate, and the two-dimensional rhenium disulfide thin film grows under the argon atmosphere at the temperature ranging from 500 DEG C to 900 DEG C. Compared with an existing rhenium disulfide preparation method, the requirement for device conditions is low, the operation process is simple, the method has the beneficial effects of being low in reaction temperature, high in growth efficiency, even in layer number, high in lattice quality of the obtained product and good in controllability, large-area, high-quality and layer-number-controllable controlled growth of rhenium disulfide is achieved, and a reliable sample preparation method is provided for application of rhenium disulfide in the field of electronic and photoelectron devices.

Owner:SHAANXI NORMAL UNIV

GaAs thin film growing on Si substrate and method for preparing same

ActiveCN104835718AImprove surface topographyReduce residual stressLaser detailsFinal product manufactureOptoelectronicsPre treatment

The present invention discloses a GaAs thin film growing on a Si substrate and a method for preparing the same. The method comprises the steps of (1) cleaning the Si substrate; (2) pre-processing the Si substrate; (4) growing a buffer layer, namely growing an InxGa(1-x)As buffer layer on the surface of the Si substrate after the processing of the step (3) at the growth temperature of 350-500 DEG C, wherein the 0.08<x<0.12; and (5) growing the GaAs thin film, namely growing the GaAs thin film at the growth temperature of 500-580 DEG C. The present invention also discloses the GaAs thin film growing on the Si substrate. The GaAs thin film growing on the Si substrate comprises the Si substrate, the InxGa(1-x)As buffer layer and the GaAs thin film which are laminated orderly. The preparation method of the present invention is simple, enables the structure of the buffer layer and an epitaxial growth technology to be simplified greatly, and obtains the GaAs epitaxial thin film which is good in surface appearance and low in residual stress.

Owner:SOUTH CHINA UNIV OF TECH

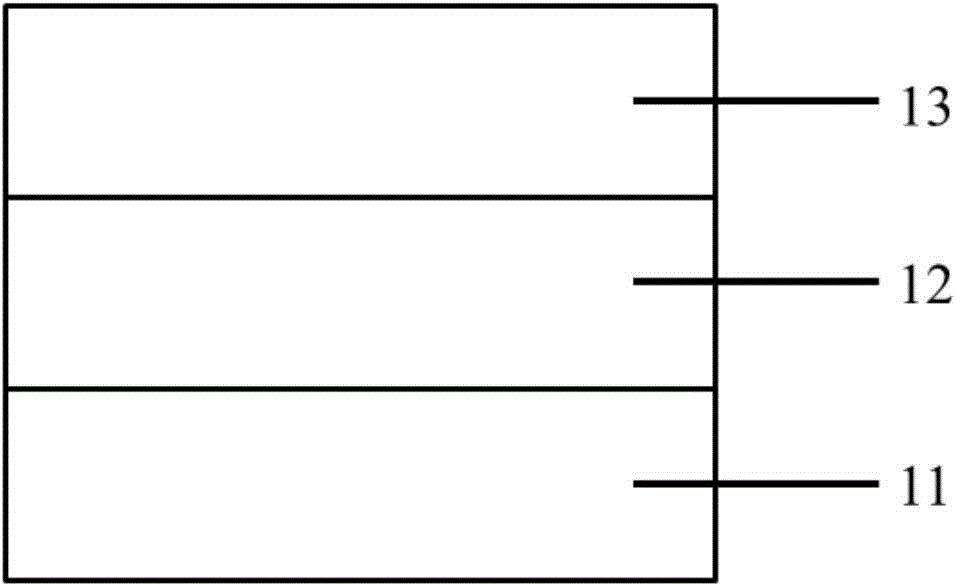

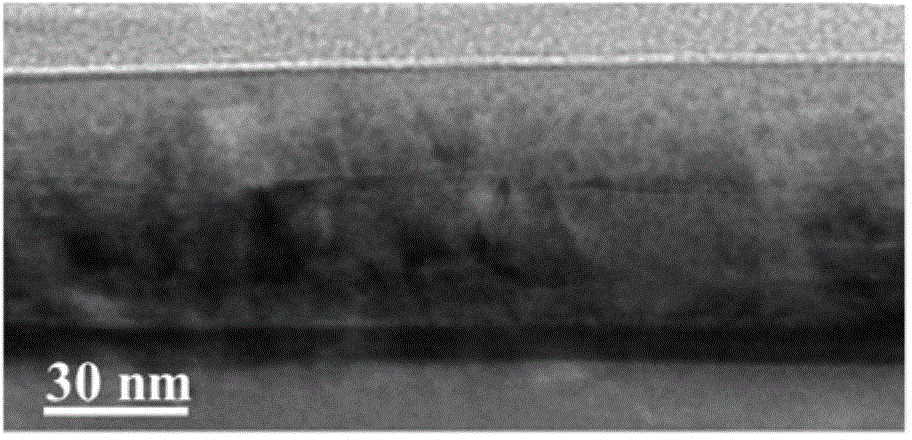

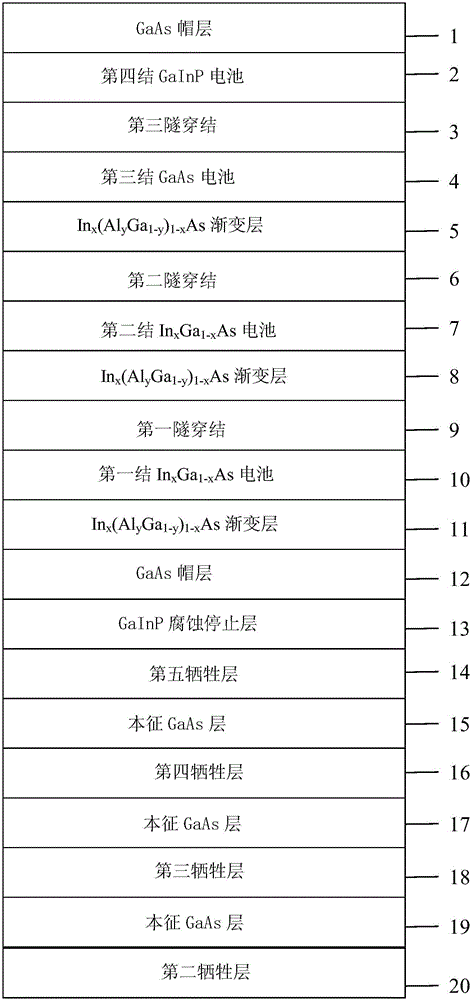

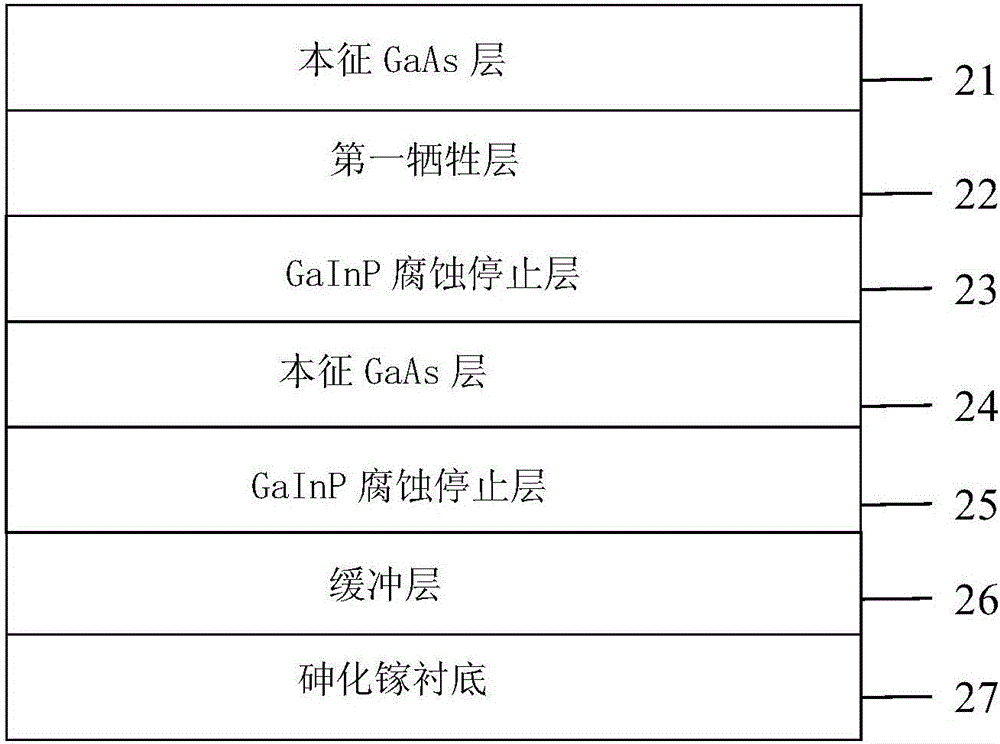

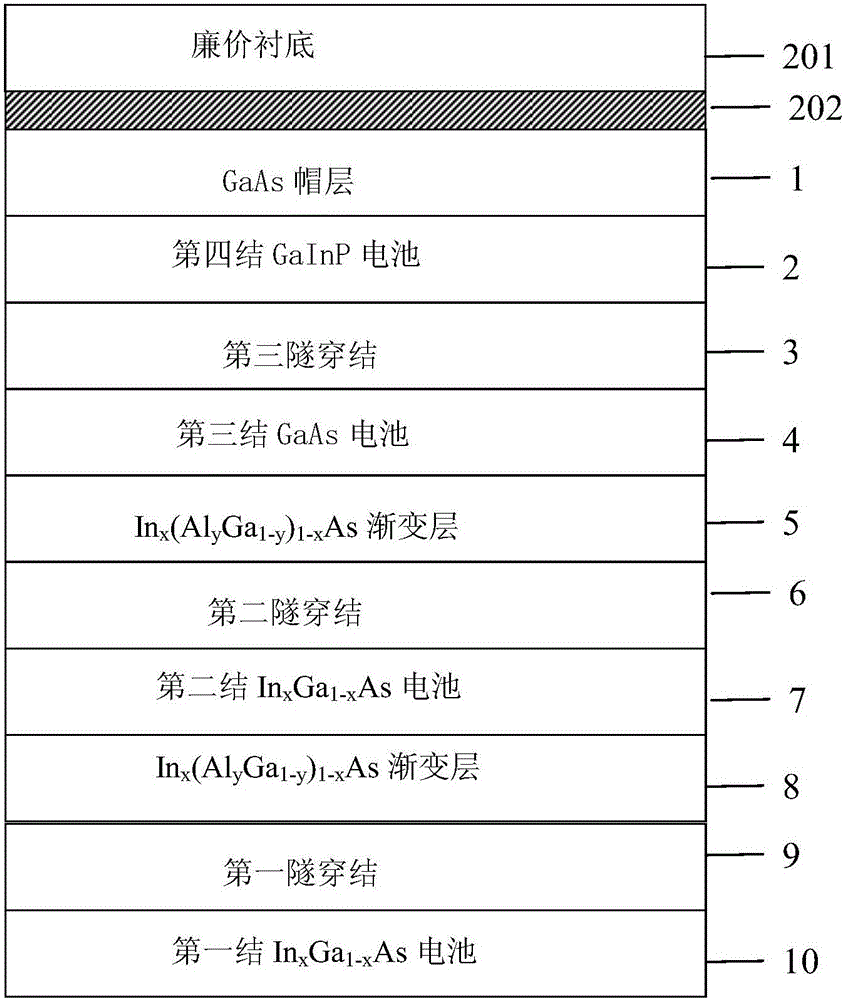

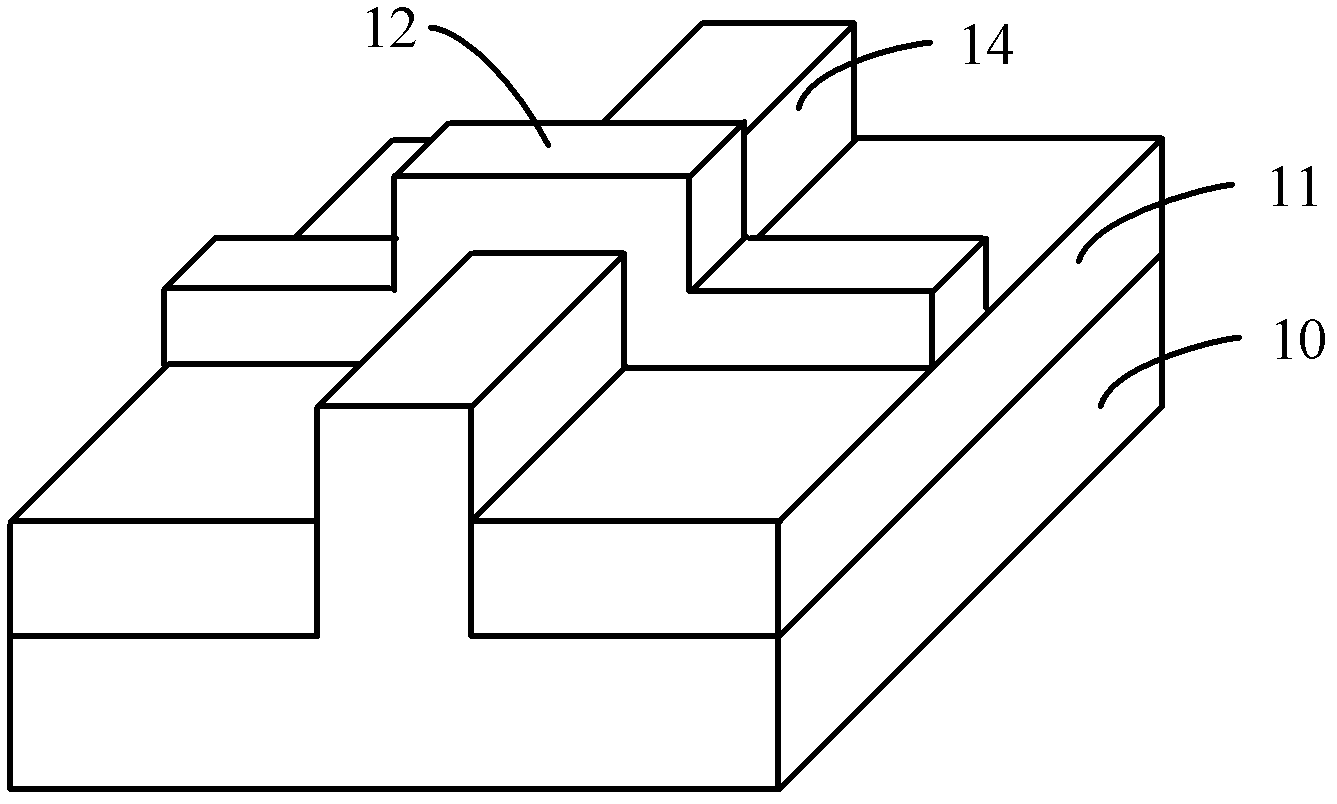

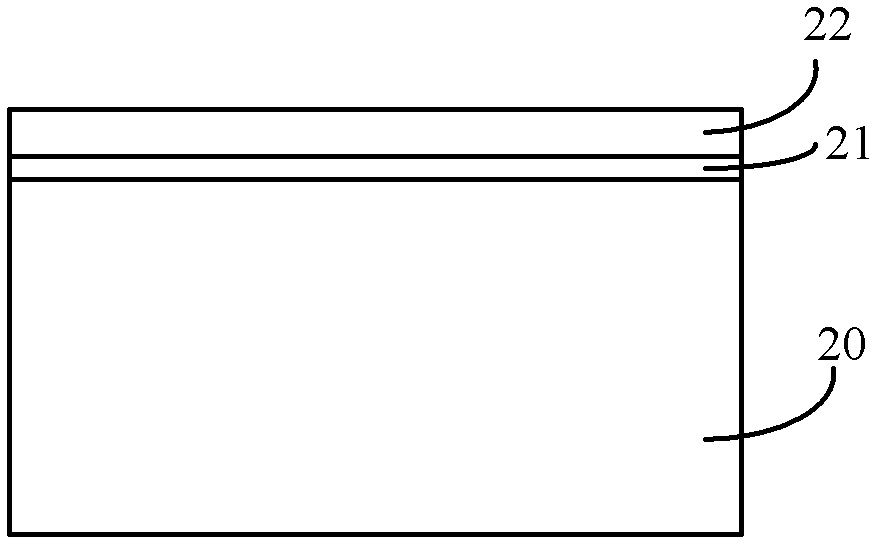

Multi-junction GaAs thin-film solar cell based on forward mismatched epitaxial growth

InactiveCN104993005AImprove photoelectric conversion efficiencyHigh mechanical strength of the connectionFinal product manufacturePhotovoltaic energy generationPhotoelectric conversion efficiencyThin film solar cell

The invention belongs to the field of solar cells and particularly relates to a multi-junction GaAs thin-film solar cell based on forward mismatched epitaxial growth. The solar cell comprises a GaAs cap layer, an In<x>(Al<y>Ga<1-y>)<1-c>As gradually-changing layer, a first knot In<x>Ga<1-x>As cell, a first tunnel junction knot, an In<x>(Al<y>Ga<1-y>)<1-x>As gradually-changing layer, a second knot In<x>Ga<1-x>As cell, a second tunnel junction knot, an In<x>(Al<y>Ga<1-y>)<1-c>As gradually-changing layer, a third GaAs cell, a third tunnel junction knot, a fourth knot GaInP cell, and a GaAs cap layer. The solar cell is prepared by using the forward mismatched epitaxial growth technology and the corroded substrate stripping technology. The stripped GaAs substrate can be reused for the epitaxial growth of the solar cell by the chemical-mechanical polishing, and cleaning technology, thereby achieving reuse of the GaAs substrate. Via the forward epitaxial growth technology, micro-area defects alternatively generated and controlled via lattice mismatching are gradually annihilated or extend toward edges, thereby ensuring well epitaxial growth of the cell and further improving photoelectric conversion efficiency of the solar cell.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST

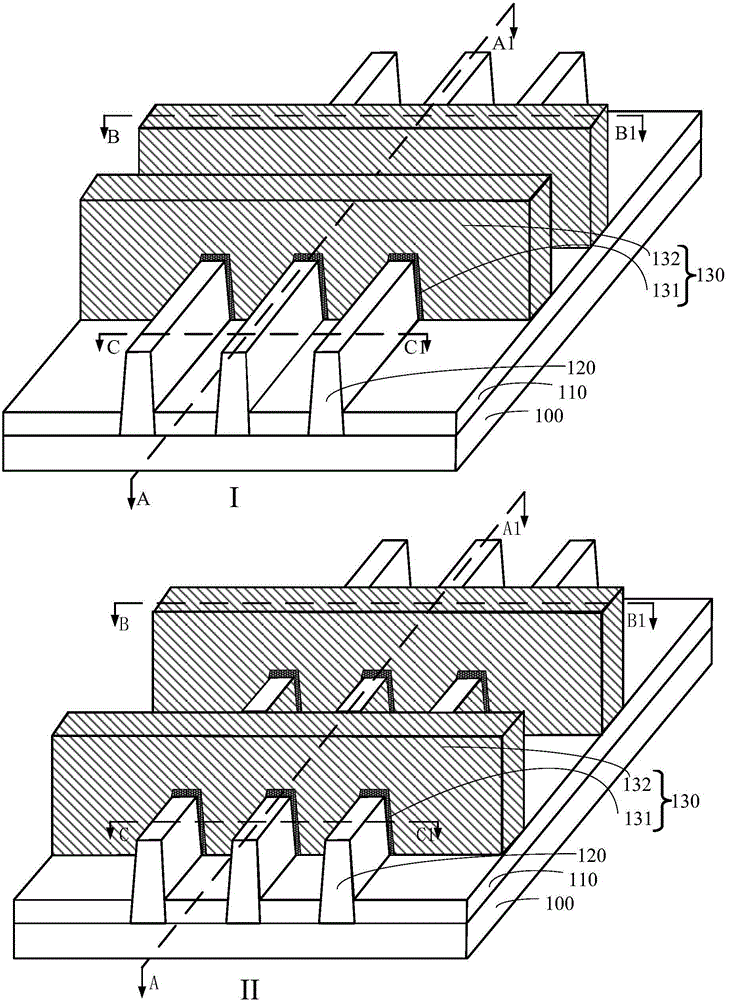

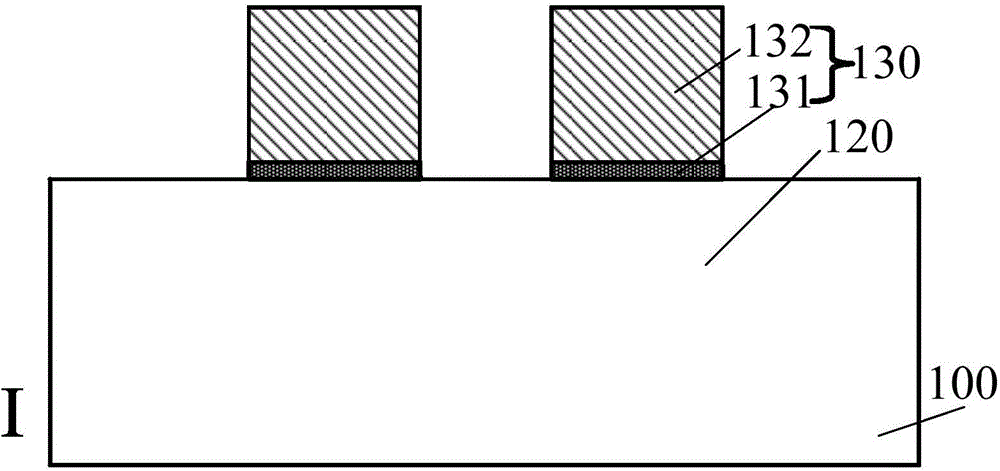

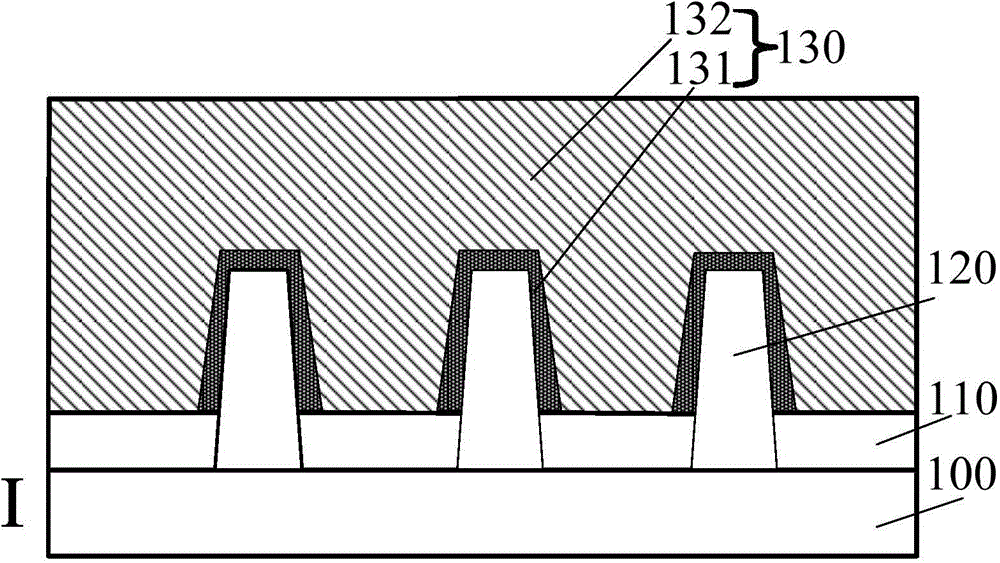

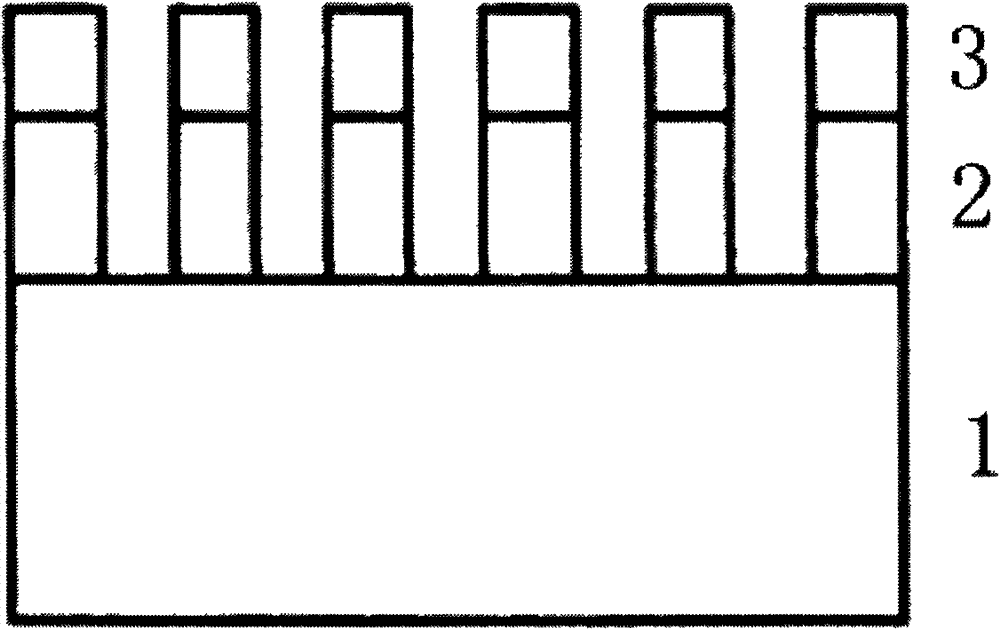

Method for forming fin portion of fin field effect tube and fin field effect tube

ActiveCN103177948AImprove performance and stabilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsField-effect transistor

The invention provides a method for forming a fin portion of a fin field effect tube and the fin field effect tube. The method for forming the fin portion of the fin field effect tube includes the steps: providing a semi-conductor substrate, forming a silicon oxide layer on the surface of the semi-conductor substrate, and forming a hard mask layer on the surface of the silicon oxide layer; etching the silicon oxide layer and the hard mask layer, forming a fin portion groove and exposing the semi-conductor substrate; filling the fin portion groove with a polycrystal material or an amorphous semi-conductor material; forming the fin portion in the fin portion groove with the polycrystal material or the amorphous semi-conductor material through an epitaxial growth method; conducting smoothening with the surface of the hard mask layer as a termination position; and removing the hard mask layer and exposing the silicon oxide layer. Crystal lattice damage on the surface of the formed fin portion is reduced, the fin portion and the inside of the silicon oxide layer are compact and free of gaps, the height of the fin portion is controllable, the performance and reliability of the fin field effect tube are improved, and forming process of small semi-conductor devices is precise.

Owner:SEMICON MFG INT (SHANGHAI) CORP

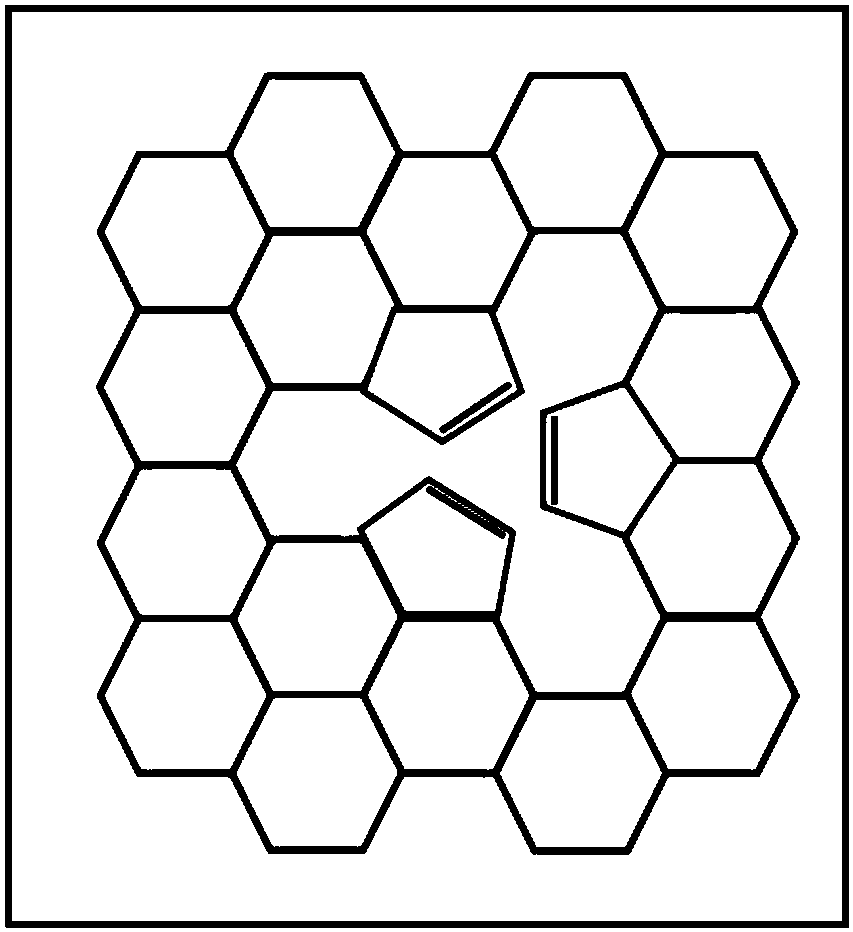

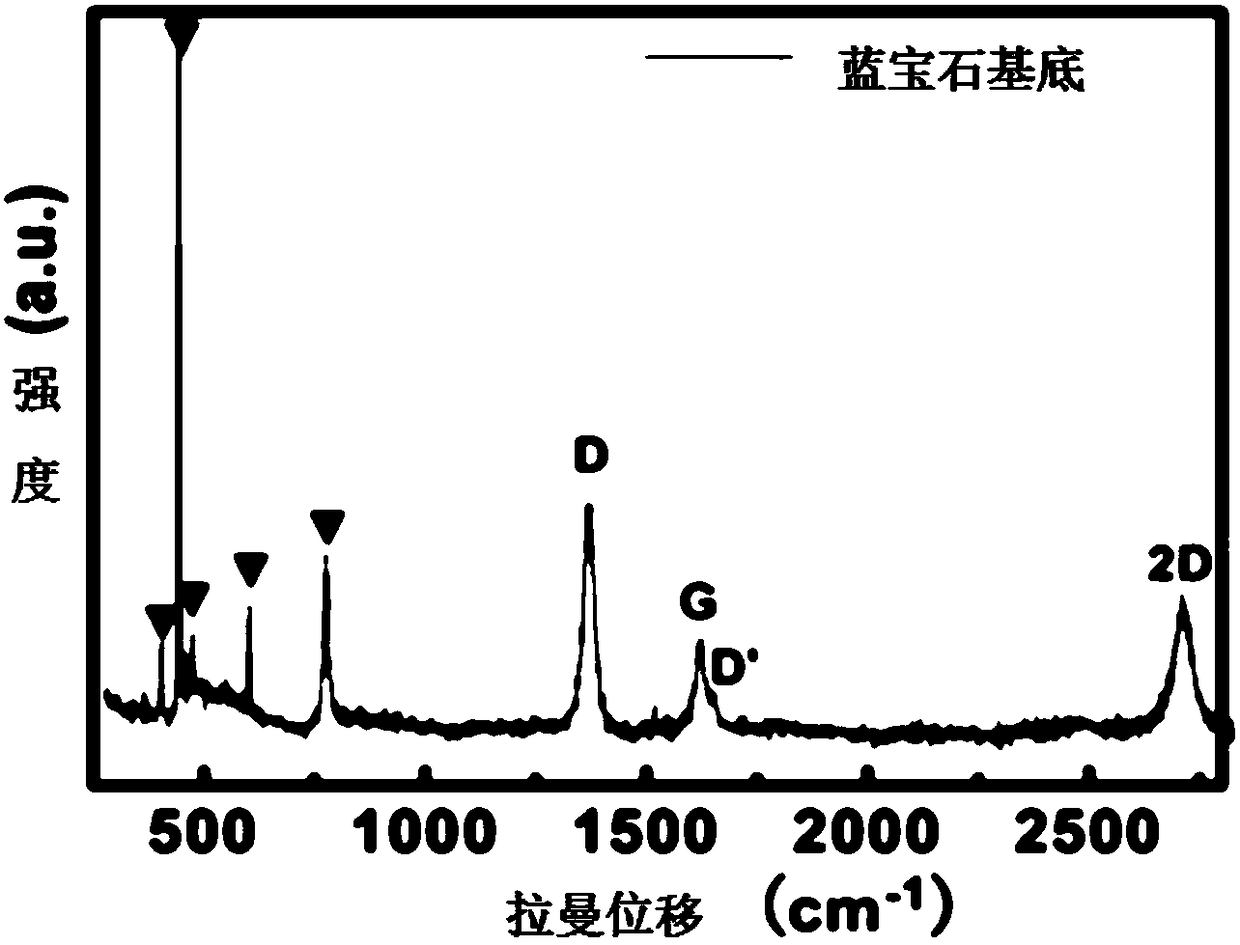

Preparation method for semiconductor material

InactiveCN109306466AImprove qualityPromotes epitaxial growthPolycrystalline material growthFrom chemically reactive gasesChemical treatmentSemiconductor materials

The invention discloses a preparation method for semiconductor material The preparation method comprises the steps that ethylene and / or acetylene are / is adopted asa carbon source; a chemical vapour deposition method is adopted, and graphene containing surface defect grows on a substrate which metal catalyst is not loaded; and in addition, the grapheme which is formed on the substrate and containsthe surface defects is adopted as a substrate body, and a semiconducting material epitaxially grows on the substrate body directly. According to the preparation method for the semiconductor materials,the graphene containing the great number of defects can be directly prepared through the chemical vapour deposition method; chemical treatment is not needed to be additionally conducted on the surface of the graphene; surface chemistry activity of the graphene can be improved; the graphene which is large in size and is uniformly provided with the great number of defects is obtained; The obtainedgraphene is directly adopted as the substrate body to grow the semiconducting material; transfer is not needed; and the problem that contamination is introduced in the substrate transfer process, so that the growing semiconducting material has macroscopic defects is avoided.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

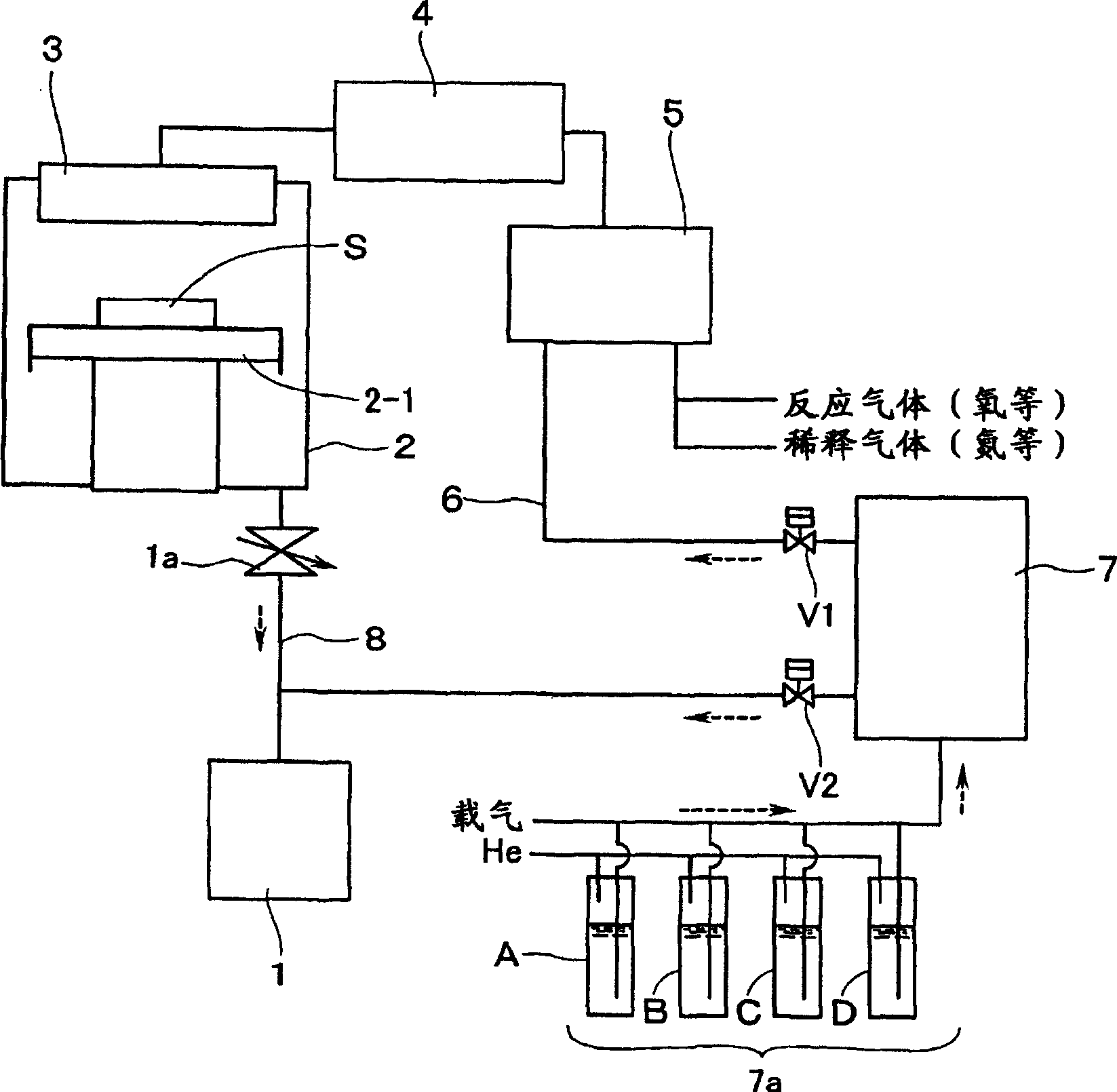

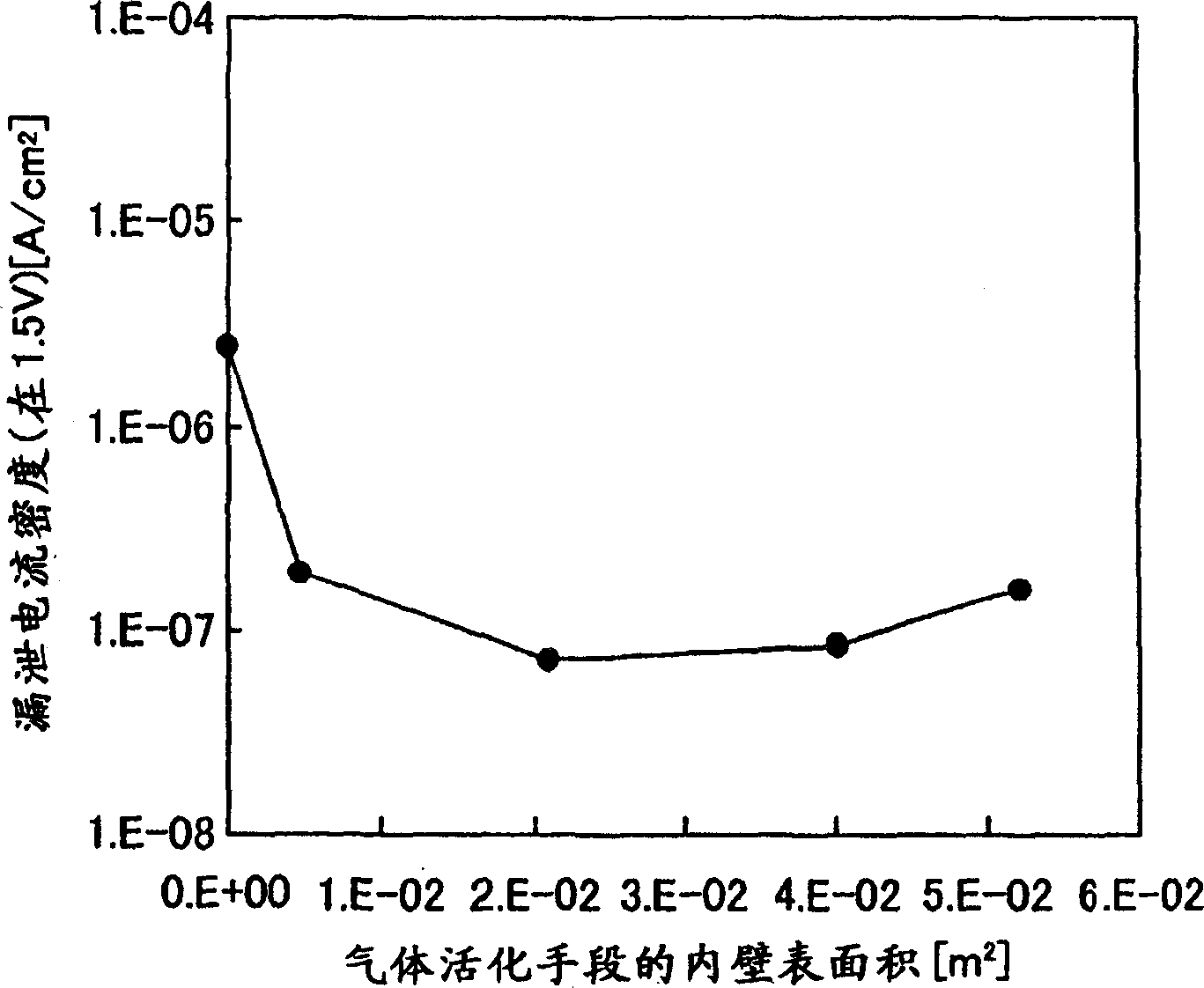

Process for producing oxide thin film and production apparatus therefor

ActiveCN1842901ASuitable decomposition stageImprove featuresSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPhysical chemistryProduct gas

The invention relates to a method and apparatus for manufacturing an oxide thin film. An oxide thin film having good characteristic properties is prepared by reducing an occurrence of an oxygen defect of the resulting oxide thin film and promoting the epitaxial growth of the film. The oxide thin film is prepared by admixing a raw gas, a carrier gas and an oxidation gas and supplying the resulting gas mixture on a heated substrate placed in a reaction chamber from a shower plate through a gas activating means which is maintained, by a heating means, at such a temperature that any liquefaction, deposition and film-formation of a raw material are never caused, to thus make the oxidation gas react with one another and to prepare the oxide thin film on the substrate. In this case, a rate of the oxidation gas flow rate is not less than 60% on the basis of the gas mixture. Furthermore, a flow rate of oxidation gas used for forming an initial layer by nucleation is less than 60%, and a flow rate of oxidation gas used in a subsequent film-forming process for forming a second layer is not less than 60%. Furthermore, in an apparatus for preparing the oxide thin film, a heating means is arranged between a gas-mixing unit and a shower plate.

Owner:ULVAC INC

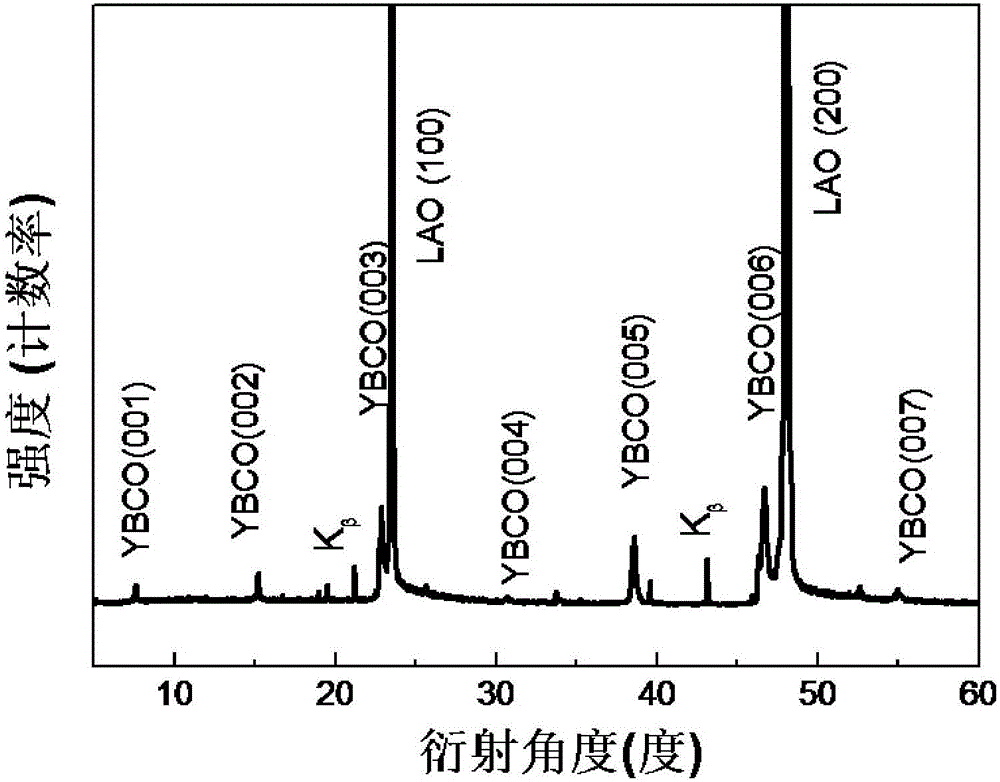

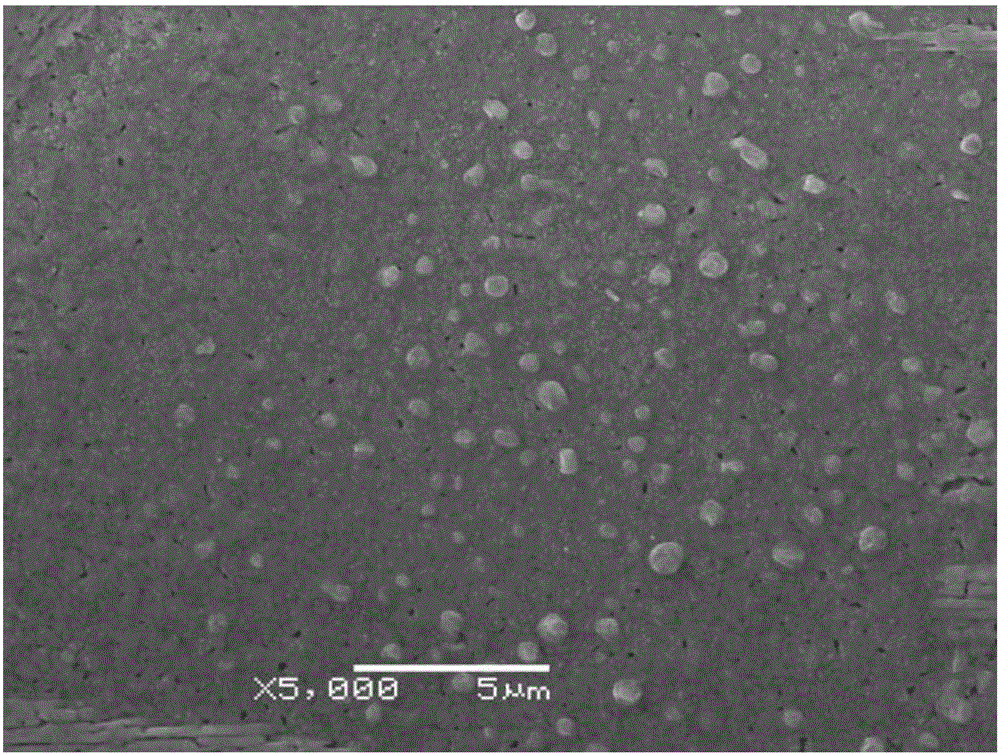

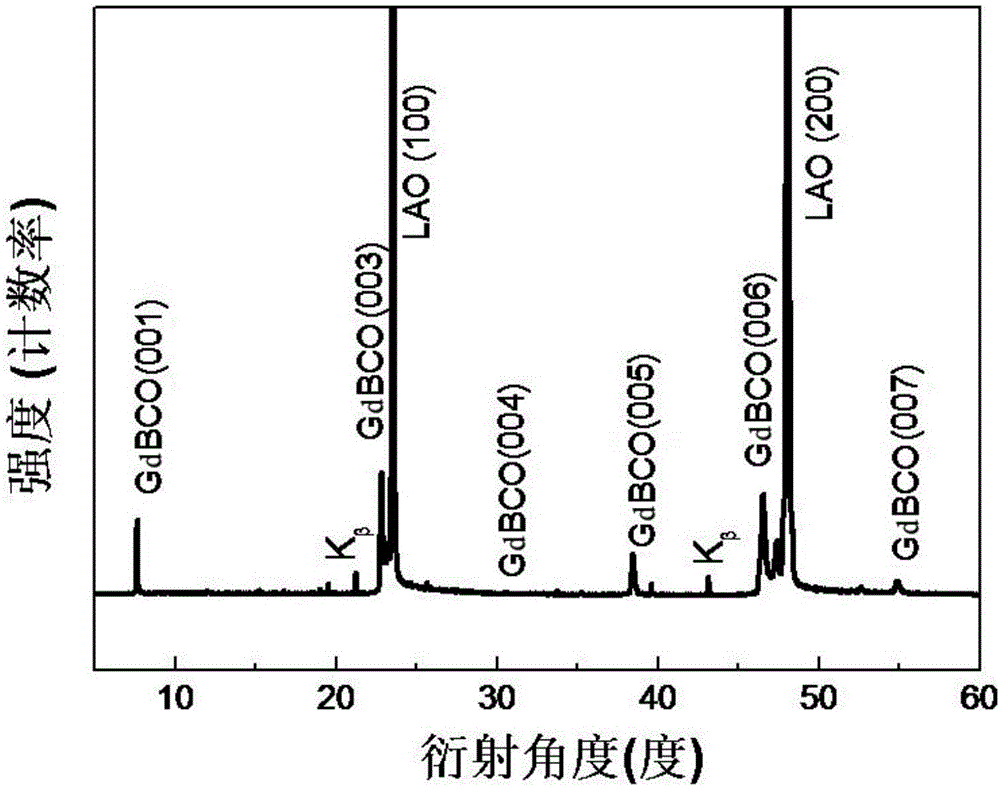

Production method of high-temperature superconductive REBCO film

ActiveCN106242553ASolving the problem of poor superconductivityInhibit carbon contentFluorine containingHeat treated

The invention provides a production method of a high-temperature superconductive REBCO film. The method comprises the following steps: 1, preparing a fluorine-free precursor solution according to an atom ratio of RE:Ba:Cu of 1:1.75:3; 2, preparing a fluorine-containing precursor solution according to an atom ratio of RE:Ba:Cu of 1:(1.5-2):3; 3, uniformly coating a LaAlO3 substrate with the fluorine-free precursor solution through adopting a spin coating technology, and carrying out heat treatment to obtain a fluorine-free monolayer precursor film; 4, uniformly coating the fluorine-free monolayer precursor film with the fluorine-containing precursor solution through adopting the spin coating technology, and carrying out heat treatment to obtain a fluorine-free / fluorine-containing bilayer precursor film; and 5, carrying out heat treatment on the fluorine-free / fluorine-containing bilayer precursor film to obtain the REBCO superconductive film. The production method is simple, allows the produced high-temperature superconductive REBCO film to have sharp cubic orientation and excellent superconductive performance, and improves the current carrying performance of the high-temperature superconductive REBCO film at 77 K.

Owner:NORTHWEST INSTITUTE FOR NON-FERROUS METAL RESEARCH

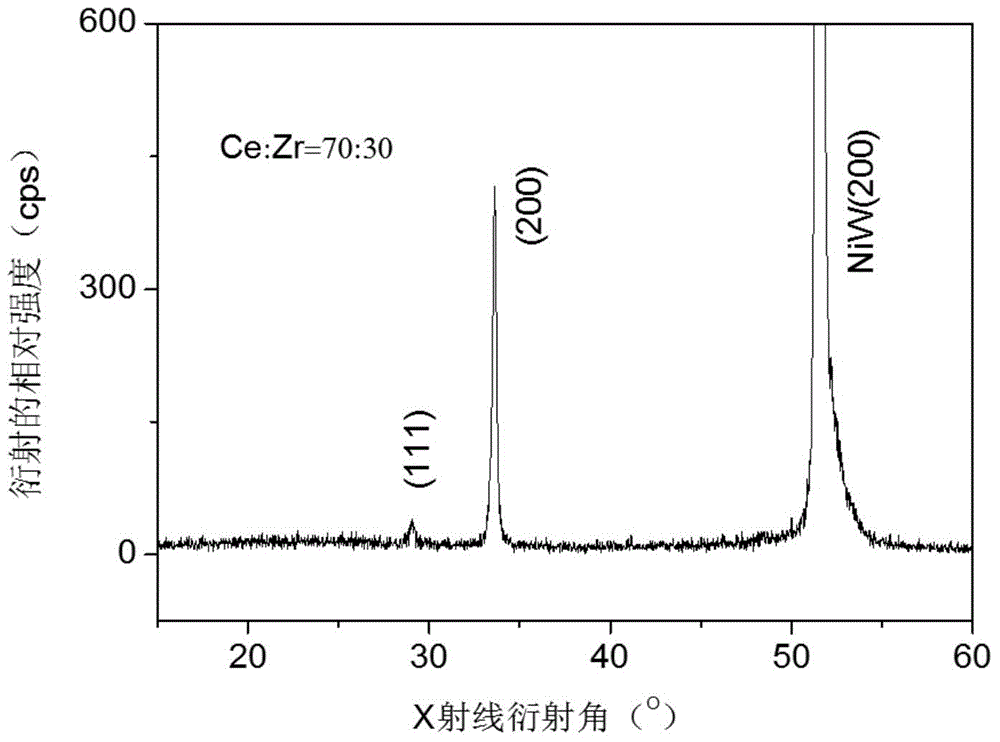

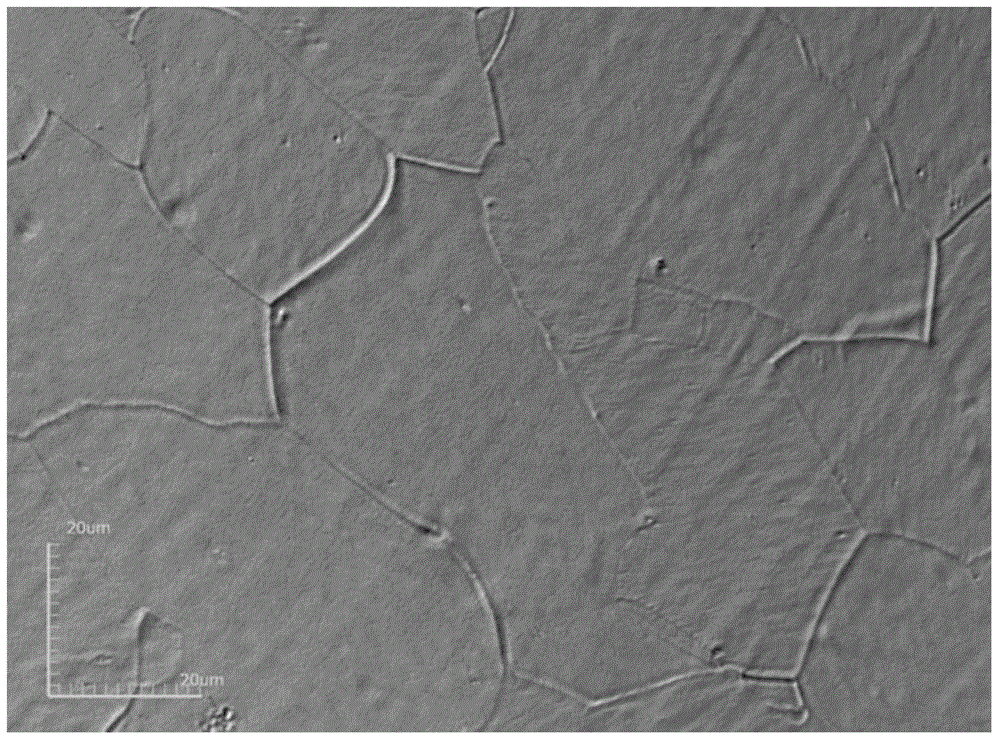

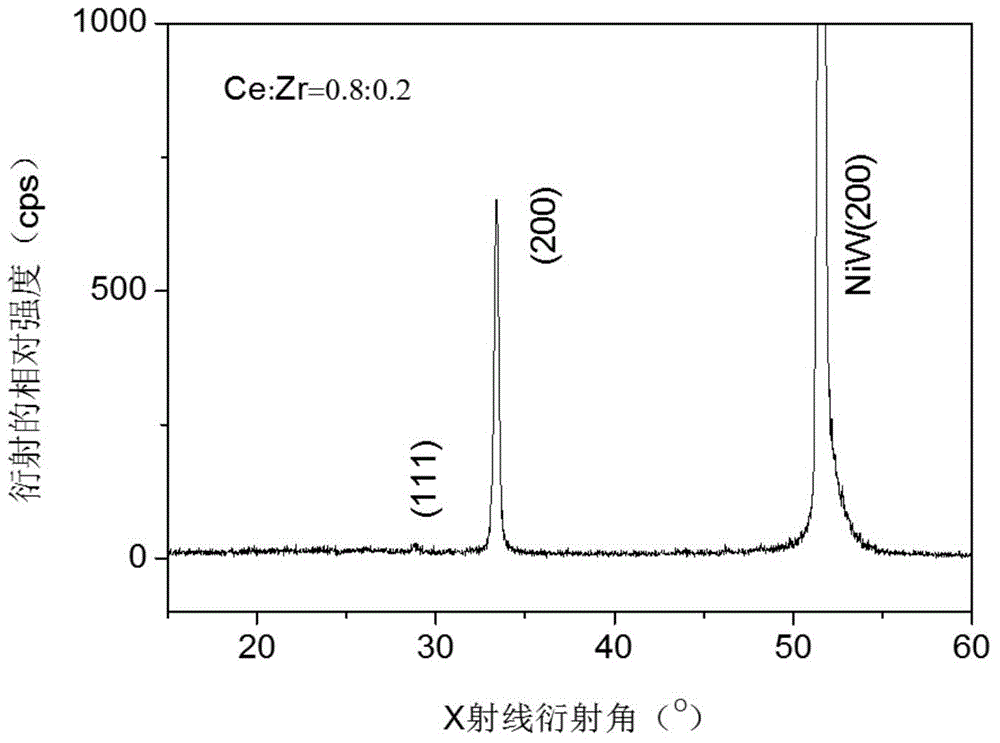

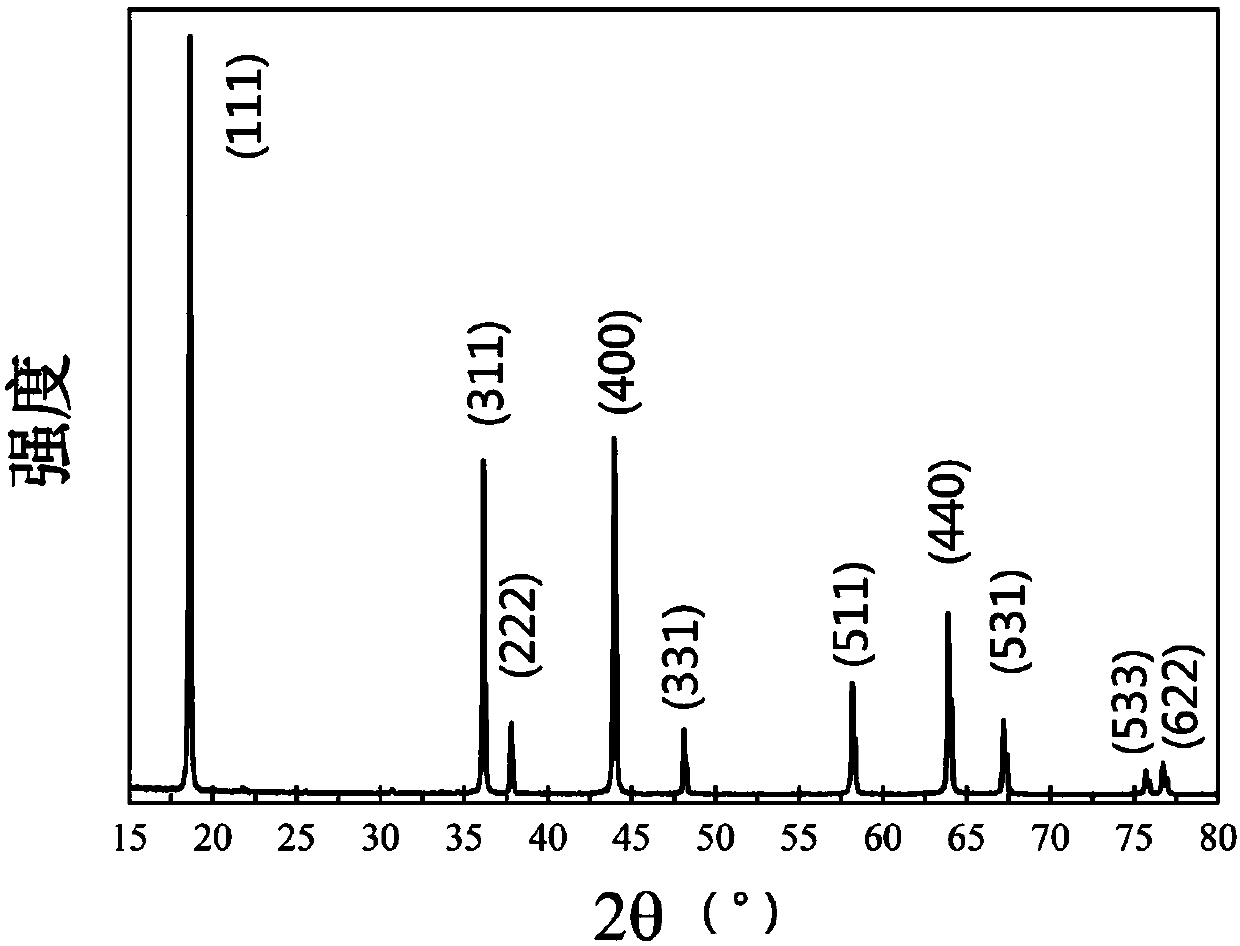

Ce<1-x>Zr<x>O2 buffer layer and preparation method thereof

The invention discloses a Ce<1-x>Zr<x>O2 buffer layer of which the chemical composition is Ce<1-x>Zr<x>O2. The buffer layer is prepared through extension phase forming thermal treatment, wherein 0.1 <= x <= 0.3. The invention also discloses a preparation method of the buffer layer, comprising the following steps: (1) dissolving Ce(NO3)3.6H2O and ZrOCl2.8H2O in a solvent according to the molar ratio of Ce:Zr=(1-x):x, and regulating the addition quantity of the solvent according to the total mole number of metal ions to obtain a precursor solution being 0.1-0.6 mol / L in metal ion concentration; and (2) coating a NiW metal base bar by the precursor solution and performing thermal treatment to prepare the Ce<1-x>Zr<x>O2 buffer layer. The invention provides a template for growing a superconductive layer YBCO, and furthermore, a series of new oxides Ce<1-x>Zr<x>O2 substitutional solid solution is obtained. The method is low in raw material cost, is wide in raw material source, is simple in process and is beneficial to industrial large-scale production.

Owner:XIAN UNIV OF TECH

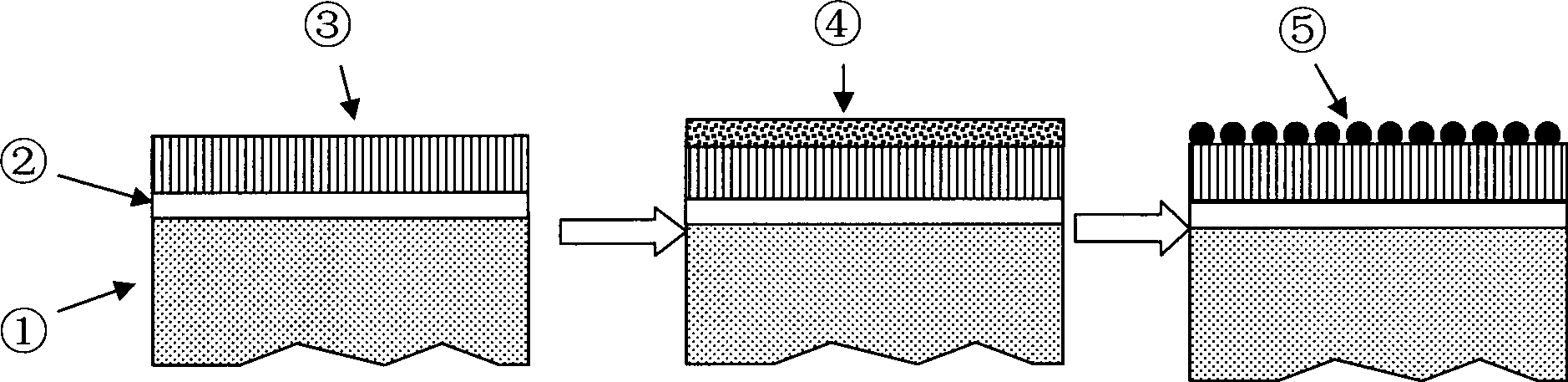

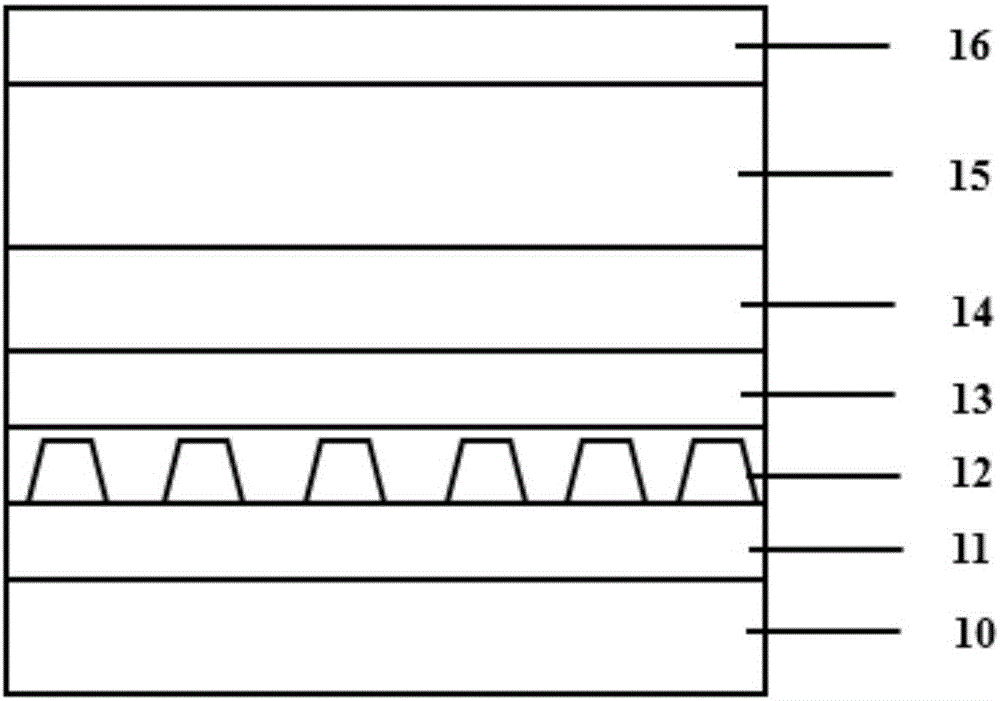

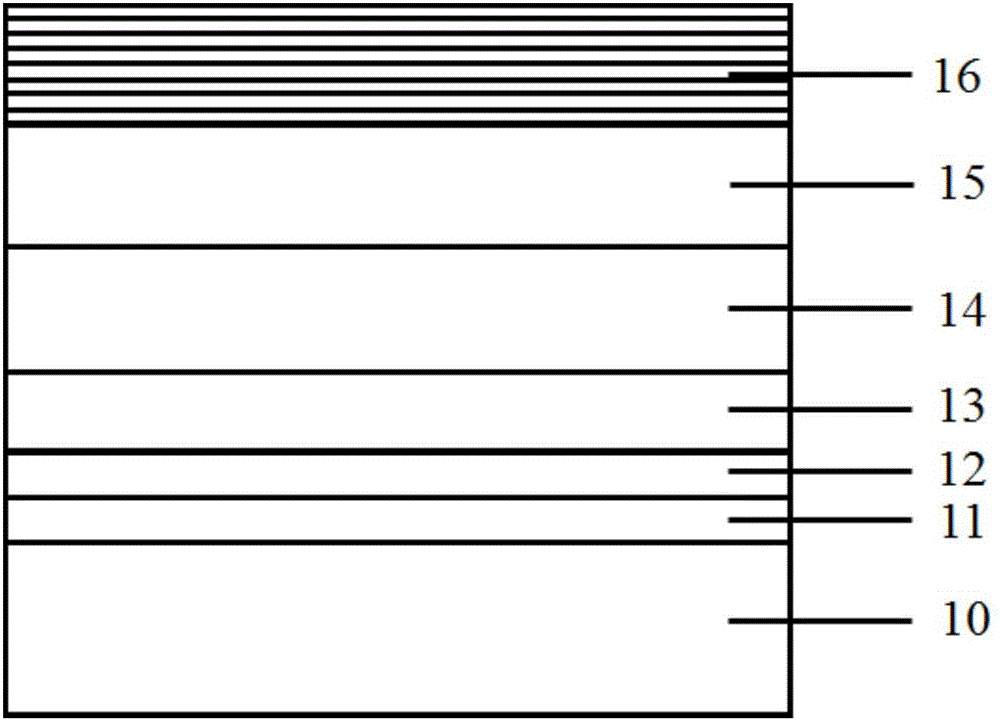

LED epitaxial wafer grown on magnesium aluminate scandium substrate and preparation method thereof

InactiveCN106257694AGood for heat dissipationImprove performanceSemiconductor devicesMagnesium AluminateSmooth surface

The invention discloses an LED epitaxial wafer grown on a magnesium aluminate scandium substrate. The LED epitaxial wafer comprises a GaN buffer layer grown on the magnesium aluminate scandium substrate, an Al nano island layer grown on the GaN buffer layer, a non-doped GaN layer grown on the Al nano island layer, an n-type doped GaN film grown on the non-doped GaN layer, an InGaN / GaN quantum well grown on the n-type doped GaN film and a p-type doped GaN film grown on the InGaN / GaN quantum well. The invention also discloses a preparation method of the LED epitaxial wafer grown on the magnesium aluminate scandium substrate The LED epitaxial wafer grown on the magnesium aluminate scandium substrate has the advantages of being simple in growth technology and low in preparation cost, and the prepared LED epitaxial wafer has smooth surface, low defect density and great photoelectric performance.

Owner:SOUTH CHINA UNIV OF TECH

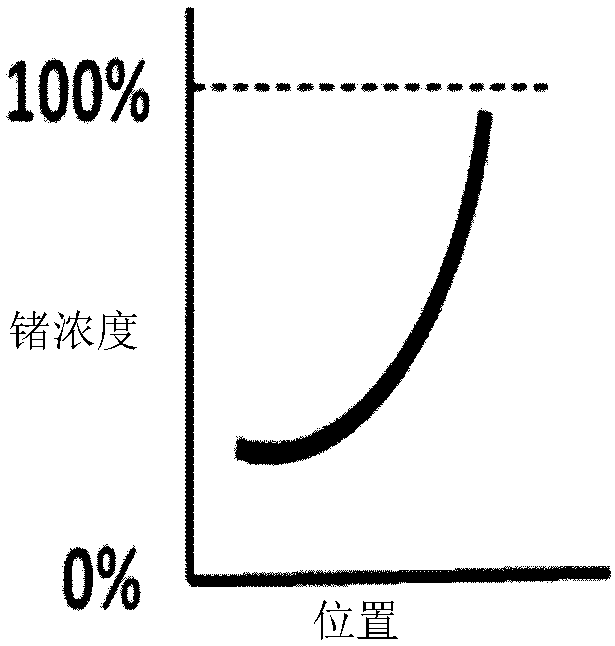

Fin transistor and making method thereof

InactiveCN108470770AImprove electrical conductivityLow manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesIsotropic etchingInsulation layer

The invention discloses a fin transistor comprising a silicon fin body with an initial first width. The bottom of the silicon fin body is isolated by a first insulation layer. A source region and a drain region are formed in the silicon fin body. After pseudo grid removing and before metal gate structure forming, isotropic etching type thinning is carried out on the silicon fin body exposed by anarea with the pseudo grid removed; and a germanium-silicon epitaxial layer coats the lateral surface and the top surface of the thinned silicon fin body by epitaxial growth, wherein the germanium concentration of the germanium-silicon epitaxial layer is in gradient distribution. The metal gate structure covers the top surface and the lateral surface of the germanium-silicon epitaxial layer and thegermanium-silicon epitaxial layer forms a channel region. In addition, the invention also discloses a making method of a fine transistor. Therefore, the channel region is formed by using a germaniumsilicon material without the need to use the silicon germanium fin body separately, so that the conductive performance of the device is improved; and no SRB layer is need, so that the cost is loweredand the process is simplified.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

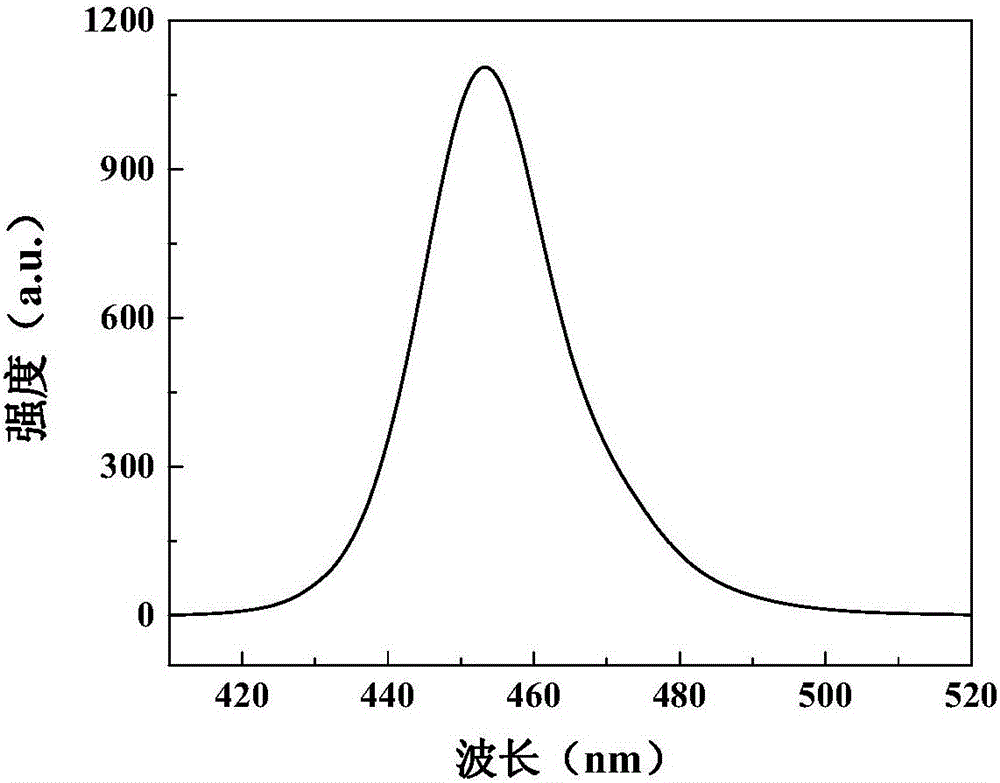

InGaN/GaN multi-quantum well grown on glass substrate and preparation method therefor

ActiveCN106505135AEfficient nucleationMore growth energySemiconductor devicesQuantum wellOptoelectronics

The invention discloses an InGaN / GaN multi-quantum well grown on a glass substrate. The InGaN / GaN multi-quantum well comprises an aluminum metal layer grown on the glass substrate, a silver metal layer grown on the aluminum metal layer, an AlN buffer layer grown on the silver metal layer, a GaN buffer layer grown on the AlN buffer layer, a non-doped GaN layer grown on the GaN buffer layer, and an InGaN / GaN quantum well grown on the non-doped GaN layer. The invention also discloses a preparation method for the InGaN / GaN multi-quantum well grown on the glass substrate. The multi-quantum well has the advantages of simple growth process and low preparation cost; and in addition, the prepared InGaN / GaN multi-quantum well is low in defect density, good in crystal quality, and good in electrical and optical performance.

Owner:SOUTH CHINA UNIV OF TECH

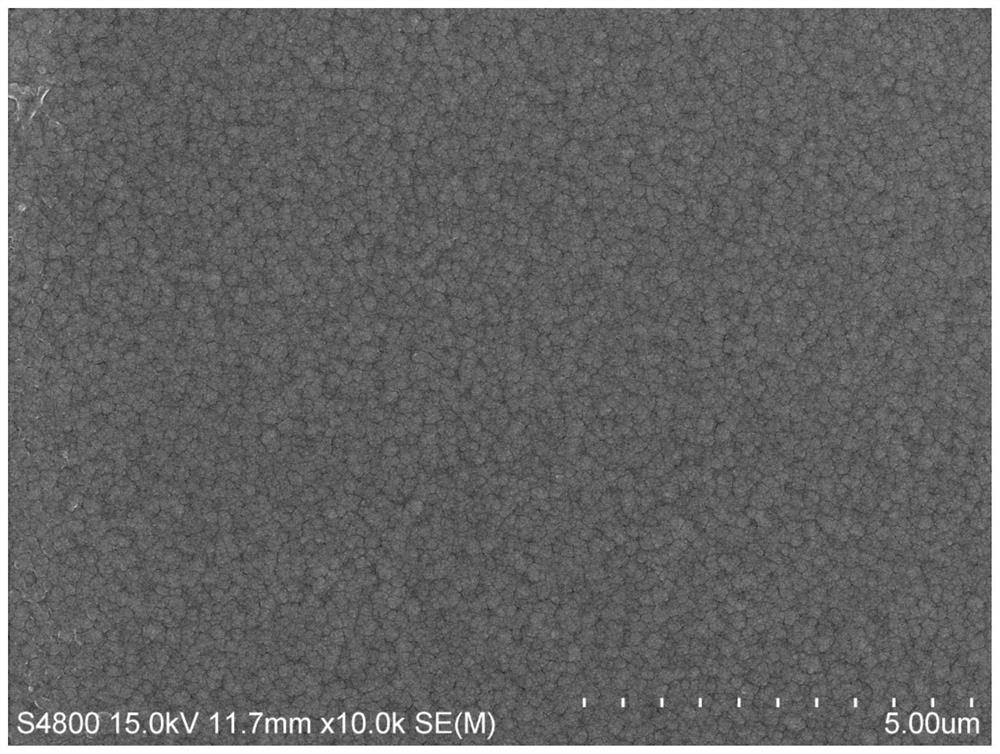

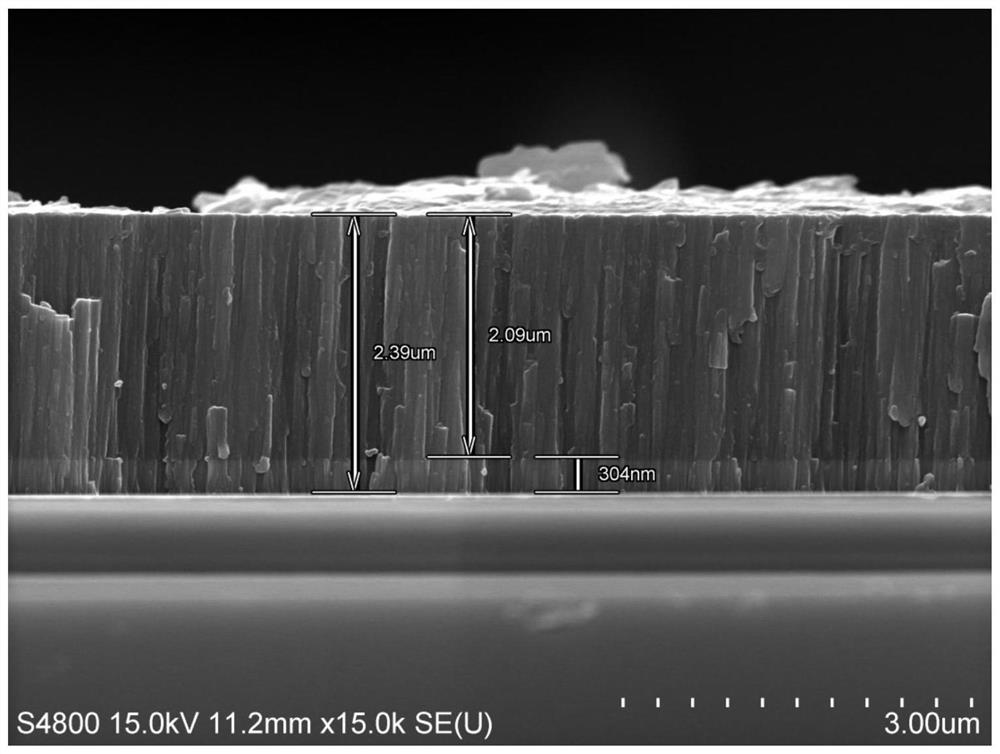

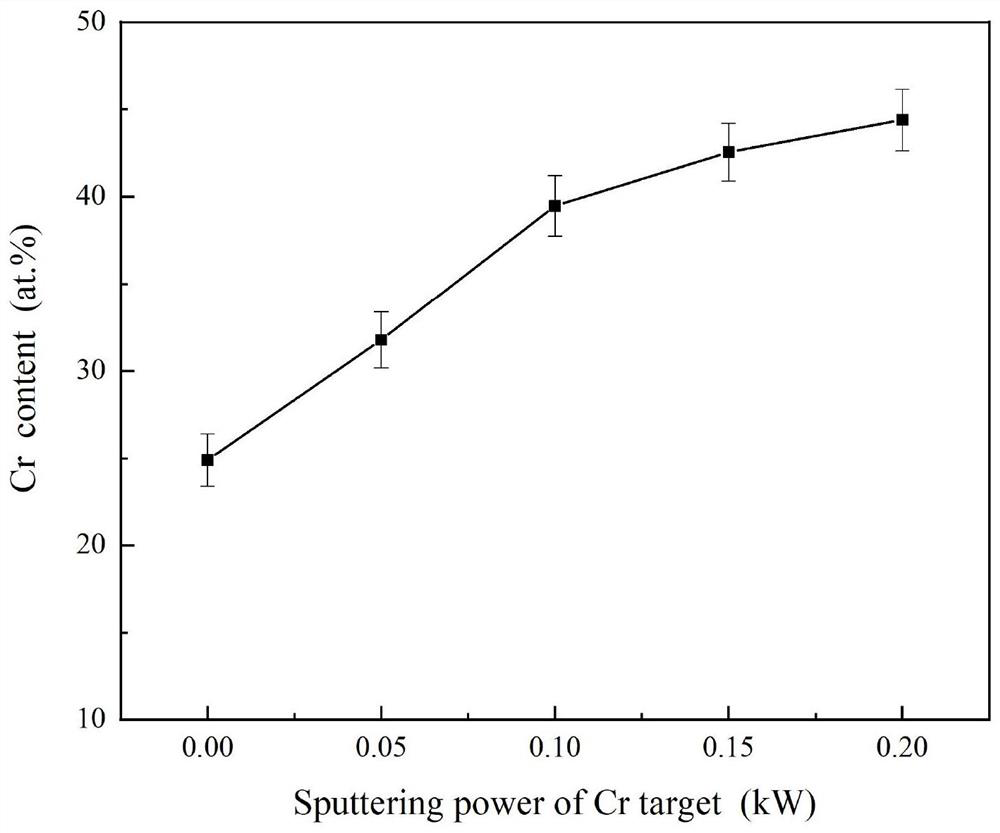

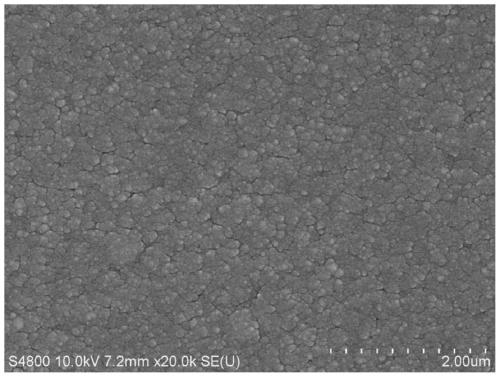

Preparation process of CrB2-Cr coating with high Cr content

ActiveCN112410728AIncrease ionization rateAchieve resilienceVacuum evaporation coatingSputtering coatingArgon atmosphereHeat stability

The invention discloses a preparation process of a CrB2-Cr coating with high Cr content, and belongs to the technical field of coating preparation. The CrB2-Cr nano composite coating is prepared on ametal or hard alloy matrix by adopting a high-power pulse and pulse direct-current composite magnetron sputtering technology. In order to better control the content of Cr in the coating, a CrB2 targetand two metal Cr targets are selected and used as target materials at the same time, a metal Cr transition layer is deposited after glow discharge cleaning and ion bombardment cleaning are conductedon the surface of a base material, finally, the Cr targets and the CrB2 target are started at the same time, the CrB2-Cr coating is deposited, and the coating process is conducted in the argon atmosphere all the time. The process is simple and good in repeatability; and the Cr element content in the prepared CrB2-Cr coating is remarkably increased, the coating has high hardness, a high melting point and excellent high-temperature thermal stability and corrosion resistance, the toughness of the coating is also improved to a certain extent, and the coating is compact in structure and high in binding force with the matrix.

Owner:TIANJIN UNIV OF TECH & EDUCATION TEACHER DEV CENT OF CHINA VOCATIONAL TRAINING & GUIDANCE

Method for surface coating modified spinel phase positive electrode material

InactiveCN110112371AUniform thicknessReduce scatterCell electrodesSecondary cellsMagnificationHYDROSOL

The invention discloses a method for surface coating modified spinel phase positive electrode material. The method comprises the following steps: 1. preparing a sol A by mixing metal salt and a chelating agent; 2, adding the spinel phase positive electrode material into the sol A and stirring so as to obtain a sol B; 3, heating and evaporating the sol B so as to obtain an xerogel; and 4, performing post-treatment on the xerogel so as to obtain the final product. According to the prepared surface coating modified spinel phase positive electrode material, the coating layer and the bulk phase material have similar crystal structure and cell parameters, and the thickness of the surface coating epitaxial growth layer is uniform so that the positive electrode material has good magnification performance and cycling performance. The method is simple and feasible, low in cost, low in energy consumption and simple in industrial large-scale production.

Owner:TIANJIN GUOAN MGL NEW MATERIALS TECH CO LTD

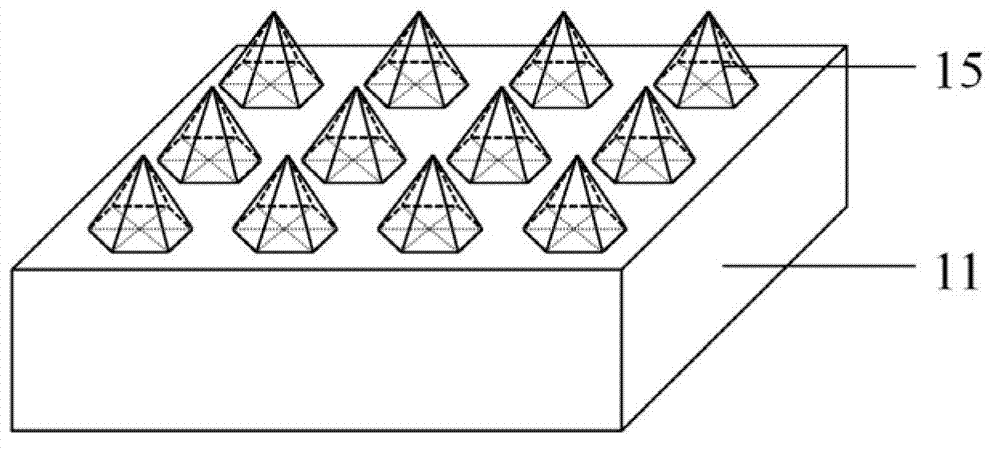

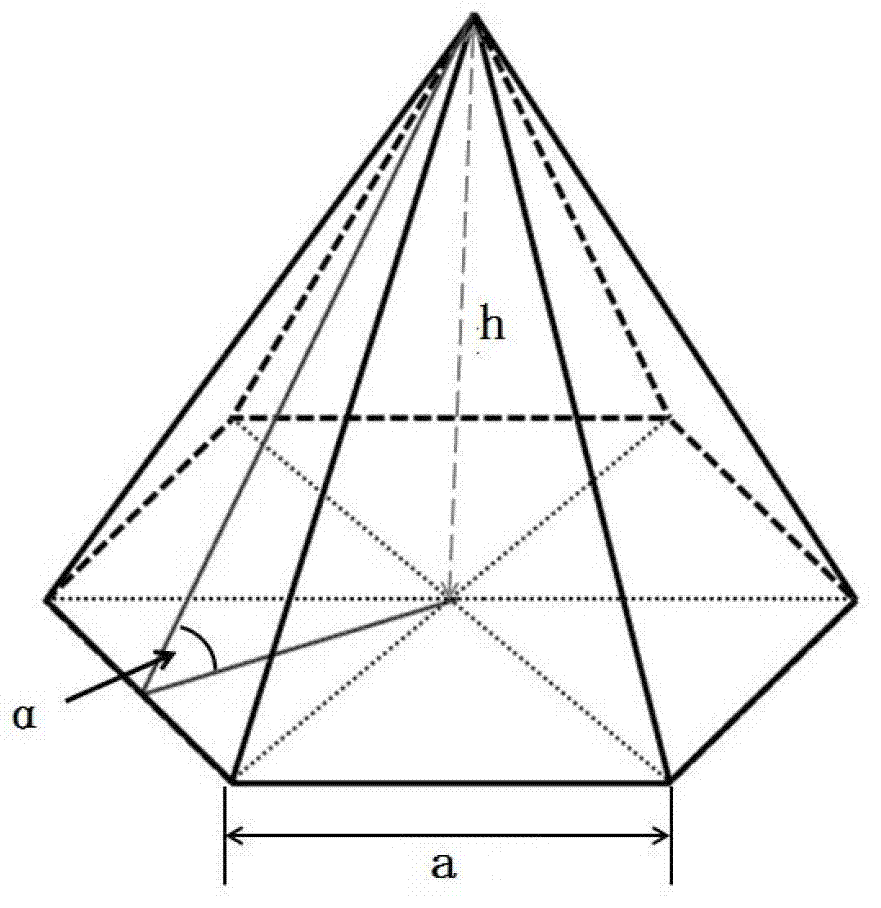

Optimized light-emitting diode (LED) chip patterned substrate and LED chip

InactiveCN103035792AImprove light extraction efficiencyImprove external quantum efficiencySemiconductor devicesEngineeringPatterned substrate

The invention discloses an optimized light-emitting diode (LED) chip patterned substrate. A Pattern of the LED chip patterned substrate is composed of a plurality of regular hexagonal pyramids with the same shape, the regular hexagonal pyramids are arranged on the surface of the LED chip patterned substrate, dip angles Alpha of the regular hexagonal pyramids are 55 degrees to 60 degrees, and edge distances between regular hexagonal pyramids next to each other are 1.0-1.2 Mum. Compared with the prior art, the LED chip patterned substrate has the advantages that luminous efficiency of the patterned substrate LED chip is greater than that of a ordinary patterned substrate LED chip, available effective light rays are increased greatly, and external quantum efficiency of the LED chip is improved. What is more, the pattern of regular hexagonal pyramids is coincident with a lattice structure of GaN, so the LED chip patterned substrate is beneficial for epitaxial growth of high quality GaN crystals, quality of epitaxy is further improved, and accordingly internal quantum efficiency of the LED chip is improved.

Owner:SOUTH CHINA UNIV OF TECH

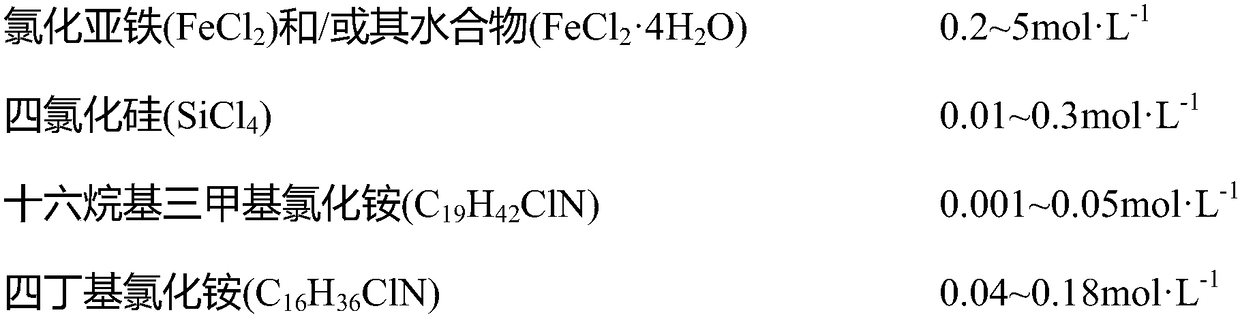

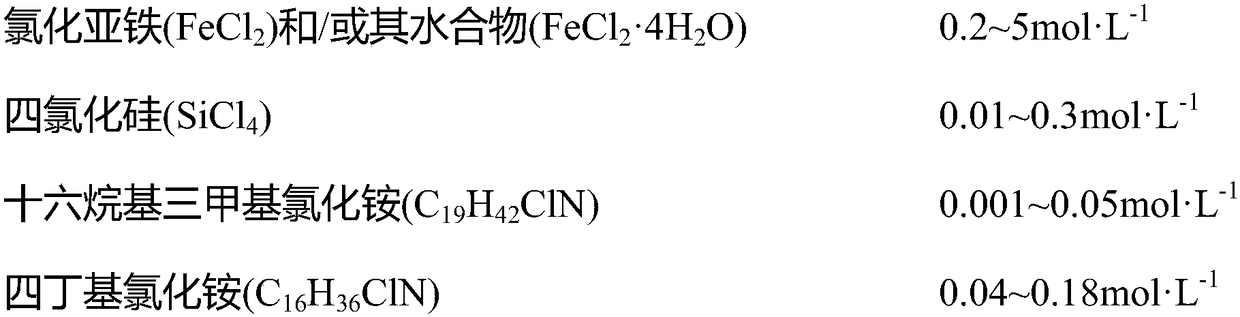

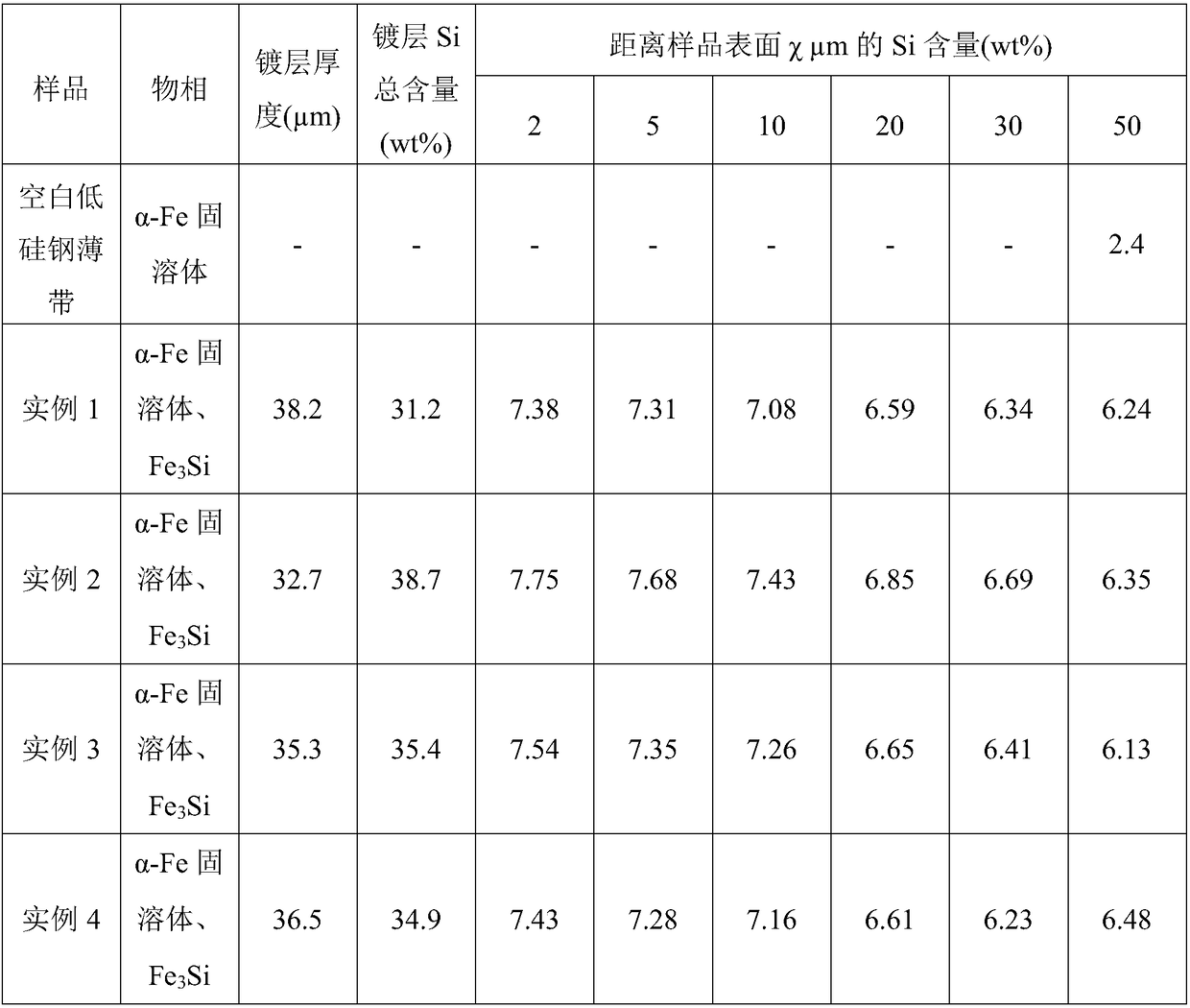

Method for preparing gradient silicon steel thin strip through normal-temperature electro-deposition-expansion percolation and special plating solution

The invention discloses a method for preparing a gradient silicon steel thin strip through normal-temperature electro-deposition-expansion percolation and a special plating solution. The method is characterized by comprising the following steps: taking a low-silicon steel thin strip as a cathode plated part, taking tetrabutyl ammonium chloride as supporting electrolyte in a propylene carbonate system which is dissolved with SiCl4, FeCl2 and / or hydrate thereof, and performing electro-deposition preparation on a Fe-Si alloy layer for the cathode plated part through a pulse electro-deposition method in an anhydrous oxygen-free environment; putting into a reducing atmosphere furnace, performing thermal expansion percolation treatment, and enabling Si to effectively percolate into a substrate surface layer, thereby preparing the gradient silicon steel thin strip. The method adopts the electro-deposition method and a thermal treatment process to perform surface treatment on the low-silicon steel thin strip, realizes secondary adding of Si of the common low-silicon steel thin strip surface layer, prepares the gradient high silicon steel thin strip, and is simple and efficient.

Owner:SUZHOU UNIV

Fin field effect transistor forming method

ActiveCN106206693ABlocking Ability EliminationImprove performanceSemiconductor devicesEtchingField-effect transistor

The invention discloses a fin field effect transistor forming method. The method comprises steps: a semiconductor substrate is provided, wherein the semiconductor substrate is provided with a gate structure dense region and a gate structure sparse area, and the surface of the semiconductor substrate is provided with convex fin parts and gate structures crossing the fin parts; a side wall material layer is formed, and the side wall material layer coats the fin parts and the gate structures; first etching is carried out on the side wall material layer, first side walls are formed at two sides of the fin parts in the gate structure dense region, second side walls are formed at two sides of the fin parts in the gate structure sparse region, and the first side walls and the second side walls are lower than the top surfaces of the fin parts; second etching is carried out on fin parts at two sides of the gate structures, first fin parts are formed, the first side walls are flush with the first fin parts, and the second side walls are higher than the first fin parts; third etching is carried out to reduce the height difference between the second side wall and the first fin part; and source and drain areas are formed on the first fin part. The fin field effect transistor forming method of the invention can improve the performance of the fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for patterning sapphire by combining wet etching and dry etching

ActiveCN102184842BIncrease corrosion rateLow mass production costElectric discharge tubesSemiconductor/solid-state device manufacturingLithographic artistSilicon dioxide

The invention discloses a method for patterning a sapphire substrate by combining wet etching and dry etching. The method comprises the following steps of: depositing a layer of silicon dioxide film on the sapphire substrate; preparing a photoresist masking film with a pattern on the silicon dioxide film through lithography; etching the lithography pattern onto the silicon dioxide film; etching the pattern onto the sapphire substrate by a method of combining wet etching and short-time dry etching, wherein the patterned silicon dioxide film serves as a masking film; and removing the silicon dioxide film through wet etching, cleaning the sapphire substrate and finishing the preparation of the patterned sapphire substrate. Because of the combination of wet etching and dry etching and the optimization of related technical parameters, the etching speed is guaranteed, the etching cost is reduced, better pattern precision can be achieved, and good etching effect can be achieved. The patterned sapphire substrate can be applied to the epitaxial growth of nitrides with low dislocation density and high crystal quality.

Owner:HC SEMITEK CORP

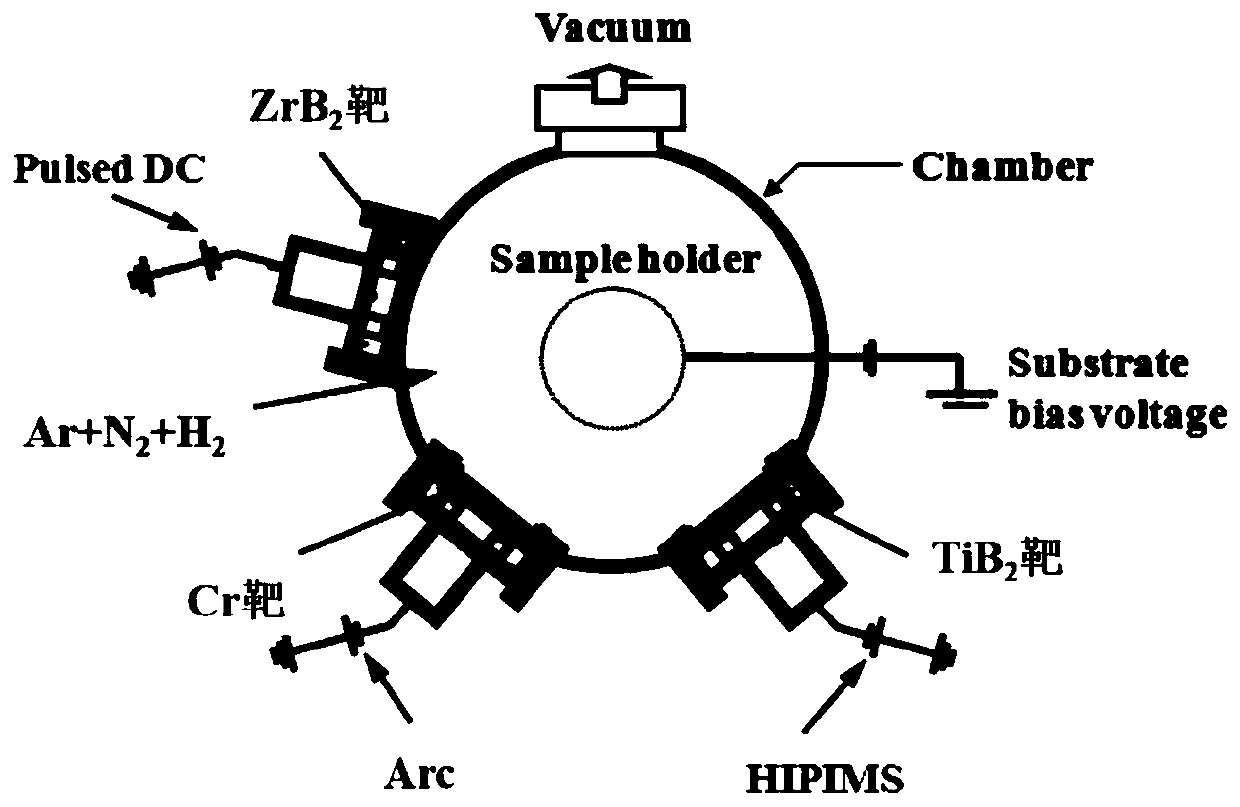

Zr-Ti-B-N nano composite coating and preparation method thereof

ActiveCN111500990AImprove adhesionIncrease deposition rateMaterial nanotechnologyVacuum evaporation coatingAmorphous phaseWear resistance

The invention discloses a Zr-Ti-B-N nano composite coating and a preparation method thereof, and belongs to the technical field of composite coatings and preparation thereof. The composite coating comprises an amorphous BN phase, a ZrN crystal phase, a TiN crystal phase, a ZrB2 crystal phase and a Ti2N crystal phase, wherein the ZrB2 phase preferentially grows along a (001) crystal face, and the Ti2N phase preferentially grows along a (110) crystal face. The Zr-Ti-B-N nano composite coating is deposited on a substrate by adopting a high-power pulse and pulse direct-current composite magnetronsputtering technology, and a TiB2 target and a ZrB2 target are connected to a high-power pulse magnetron sputtering cathode and a pulse direct-current magnetron sputtering cathode correspondingly; andthe Zr-Ti-B-N coating is deposited in a mixed atmosphere of Ar, N2 and H2. The nano-composite coating has the advantages of higher hardness and elasticity modulus, good wear resistance, the compact organizational structure and strong binding force between the coating and the substrate.

Owner:TIANJIN UNIV OF TECH & EDUCATION TEACHER DEV CENT OF CHINA VOCATIONAL TRAINING & GUIDANCE

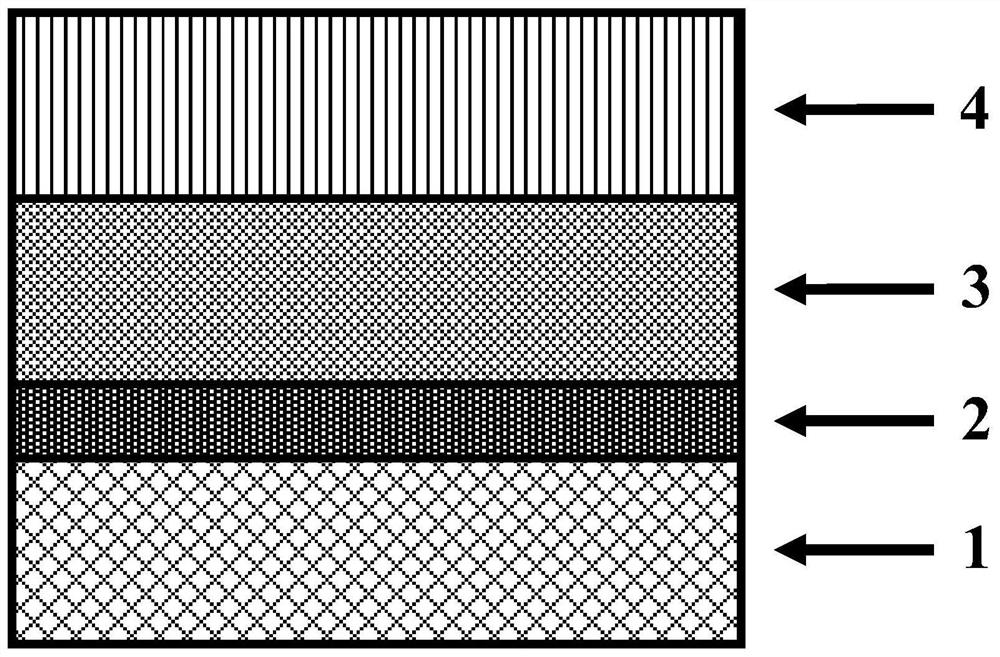

A kind of nitride LED epitaxial wafer structure and its preparation method based on copper substrate

InactiveCN104538526BImprove crystal qualityNitride Epitaxial Growth of High Crystal QualitySemiconductor devicesOptical propertyNitride

Owner:江苏巨晶新材料科技有限公司

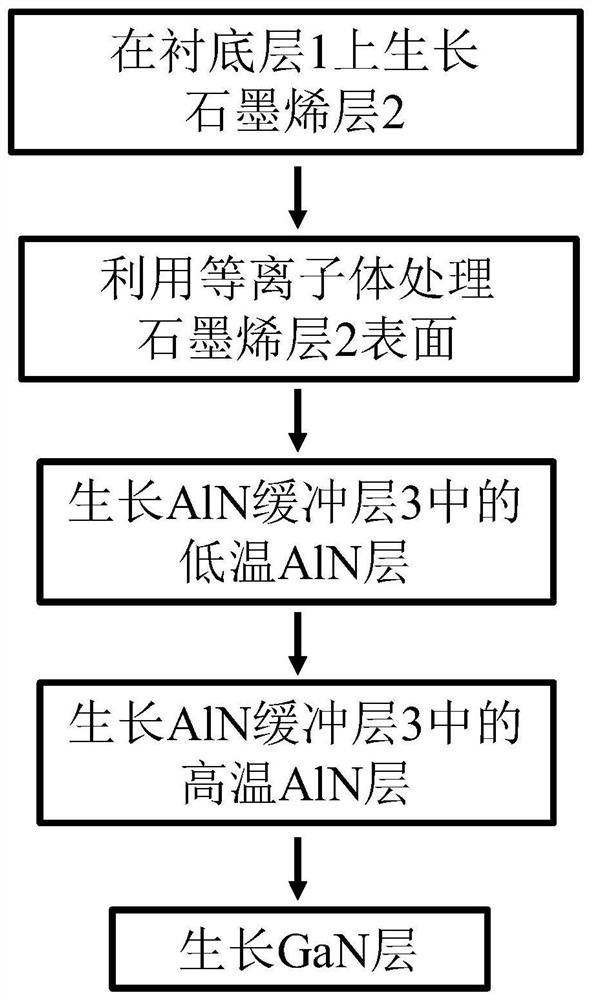

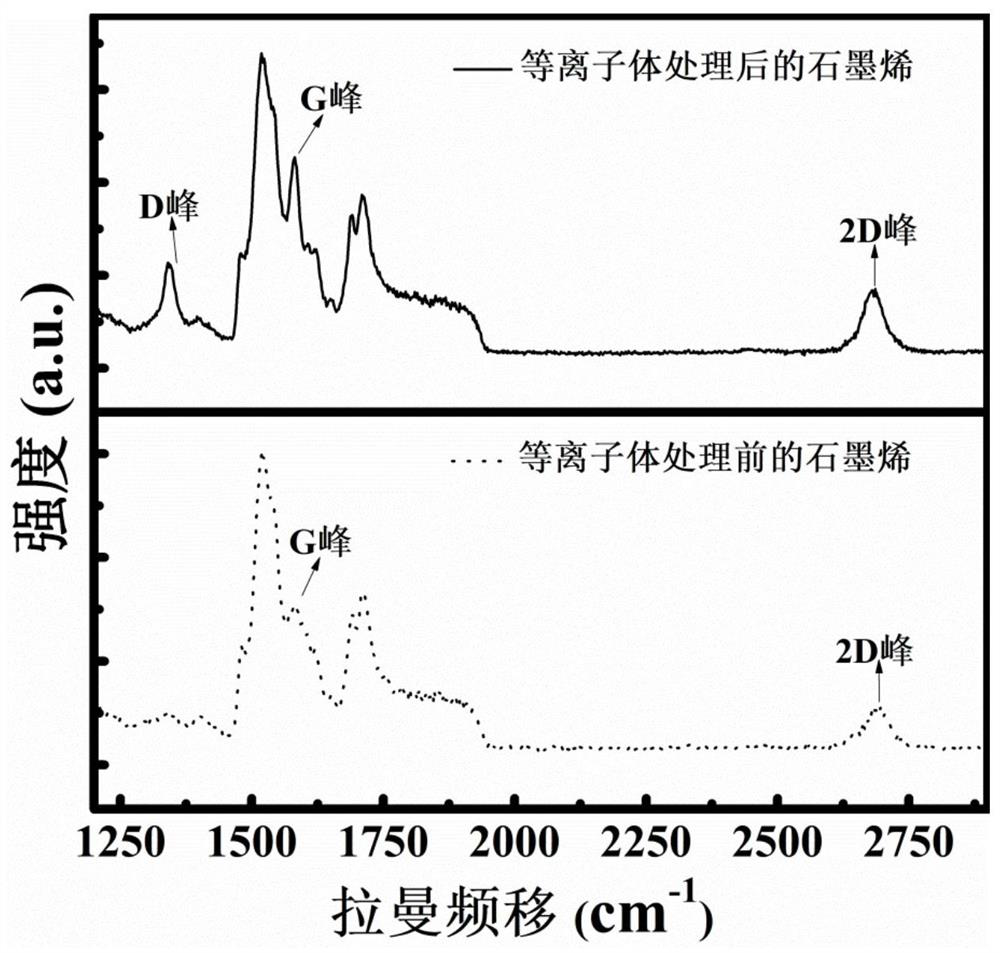

Method for growing GaN film on graphene

PendingCN112053942AReduce stressLow crystal qualitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh densityPhysical chemistry

The invention discloses a method for growing a GaN film on graphene, and belongs to the technical field of semiconductors. The method comprises the following steps: firstly, growing a graphene layer on a substrate layer, and then pretreating the surface of the grown graphene layer by utilizing plasma; then sequentially growing an AlN buffer layer and a GaN layer on the graphene layer in an epitaxial mode through an MOCVD method, wherein growth sources are trimethyl aluminum, trimethyl gallium and high-purity ammonia gas, the growth temperature ranges from 700 DEG C to 1300 DEG C, and the growth pressure intensity ranges from 50 mbar to 400 mbar; and growing on the graphene to obtain the GaN film. The AlN buffer layer is prepared by adopting a two-step temperature growth method, that is, alow-temperature AlN layer is extended outside the graphene layer at a low temperature(700-900 DEG C), and then a high-temperature AlN layer is extended continuously by raising the temperature(1000-1300 DEG C). According to the method disclosed by the invention, high-density AlN nucleation islands can be obtained on the graphene, and the transverse combination of the high-density AlN nucleation islands can be promoted, so that enough nucleation sites can be provided for the subsequent growth of GaN, and the epitaxial growth of the GaN film is realized.

Owner:JILIN UNIV

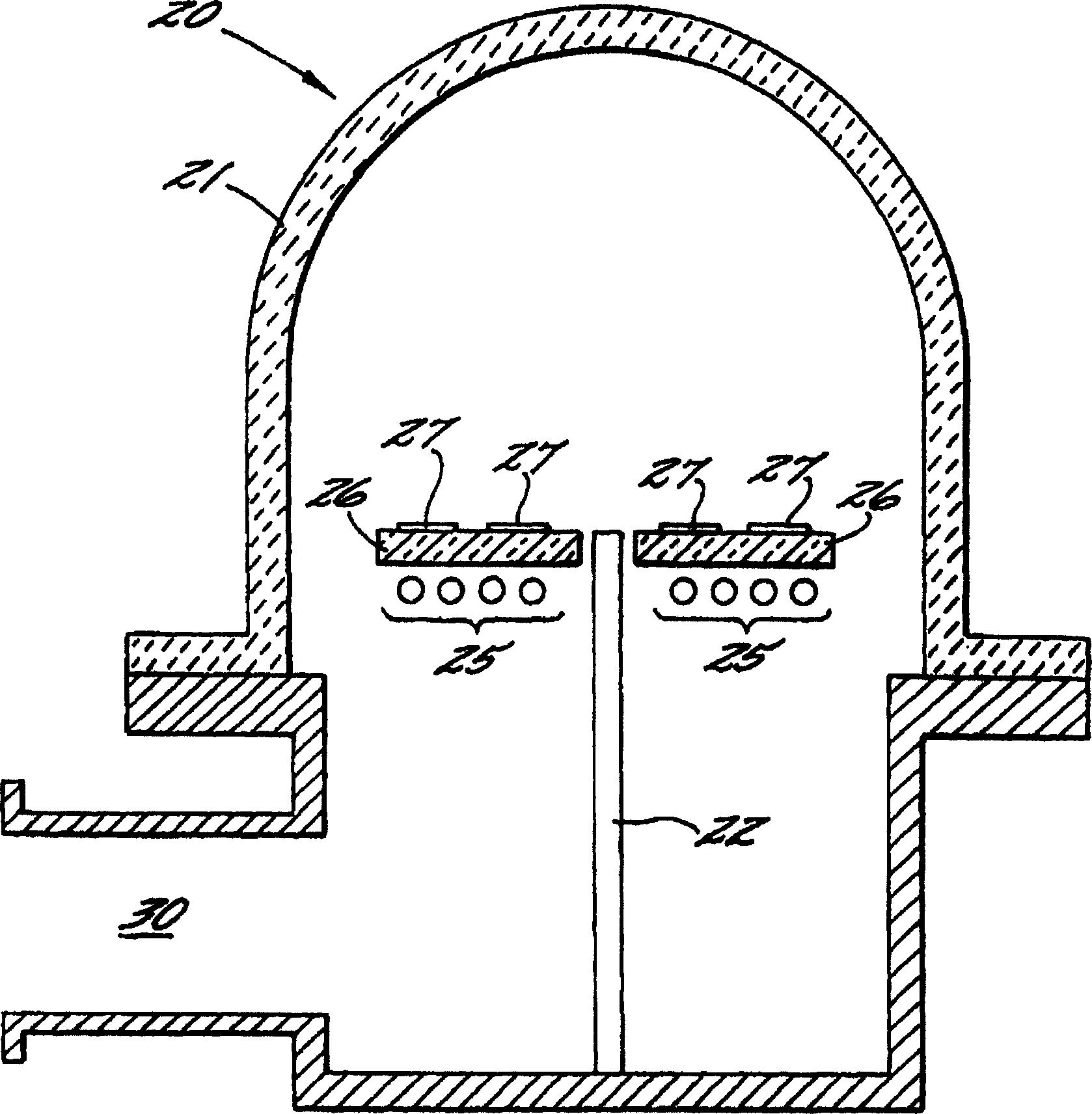

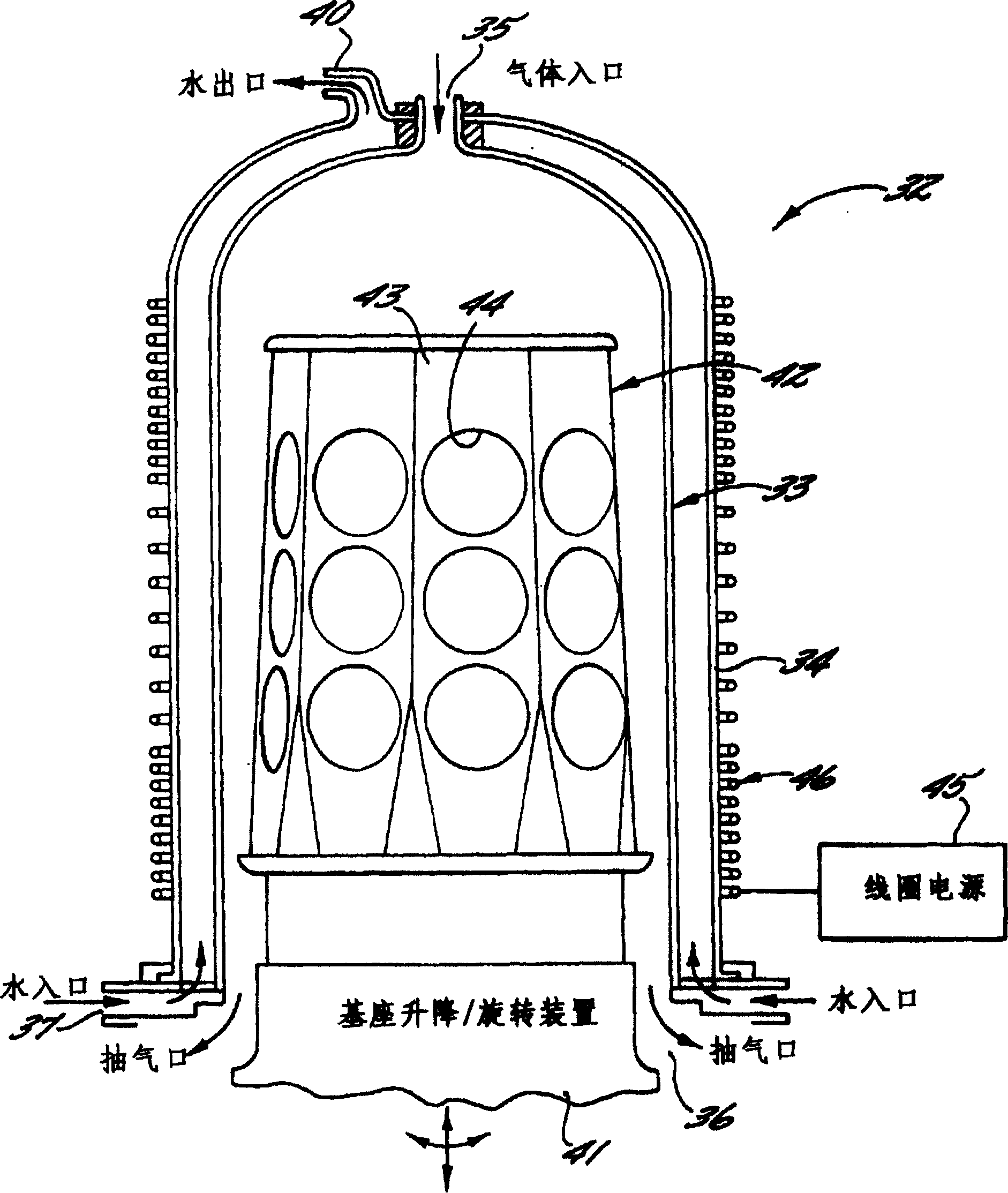

Susceptor designs for silicon carbide thin films

InactiveCN1220800CAvoid flowMinimize or eliminate temperature gradientsSemiconductor/solid-state device manufacturingFrom chemically reactive gasesSusceptorEngineering

A susceptor is disclosed for minimizing or eliminating thermal gradients that affect a substrate wafer during epitaxial growth. The susceptor includes a first susceptor portion including a surface for receiving a semiconductor substrate wafer thereon, and a second susceptor portion facing the substrate receiving surface and spaced from the substrate-receiving surface. The spacing is sufficiently large to permit the flow of gases therebetween for epitaxial growth on a substrate on the surface, while small enough for the second susceptor portion to heat the exposed face of a substrate to substantially the same temperature as the first susceptor portion heats the face of a substrate that is in direct contact with the substrate-receiving surface.

Owner:CREE INC

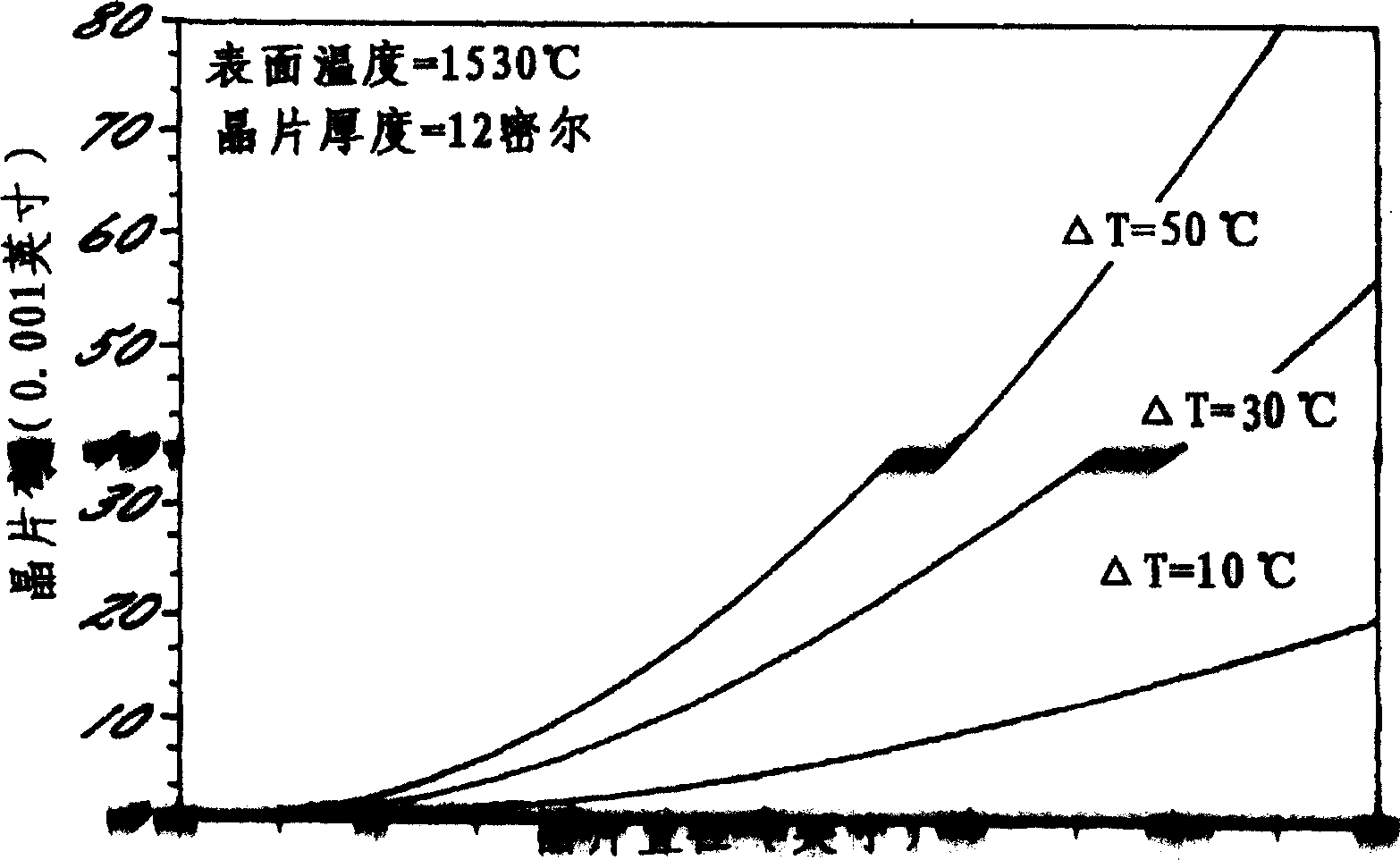

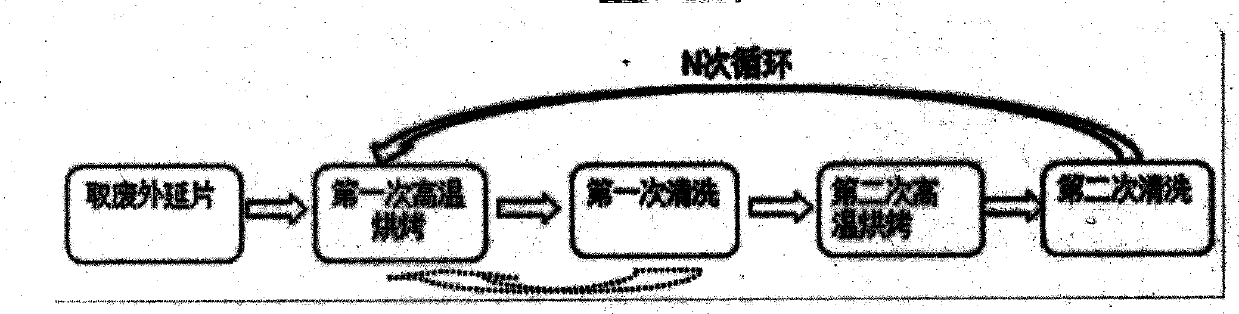

A kind of method of reclaiming sapphire substrate

The present invention aims at the problems of high production cost of sapphire substrates and non-reusable substrates existing in the prior art, and provides a method for recovering sapphire substrates, which uses physical high-temperature baking and wet etching, The special corrosion solution can not only remove gallium nitride particles and general residues, but also has a remarkable effect on removing refractory metal residues and surface oil stains. This method can be used for sustainable recycling of PSS substrates and flat substrates, with short recycling period, simple operation, and low cost. After the above operation process, each sapphire substrate can reach the level of the first use of the substrate and produce high-quality epitaxy The cost of recycling a single chip is only 10 yuan.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com