Fin transistor and making method thereof

A technology of a fin transistor and a manufacturing method, which is applied in the manufacturing of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of low thermal conductivity, high junction leakage, poor interface contact, etc., and achieve photolithography etching. The effect of simple process, improved electrical conductivity and reduced manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

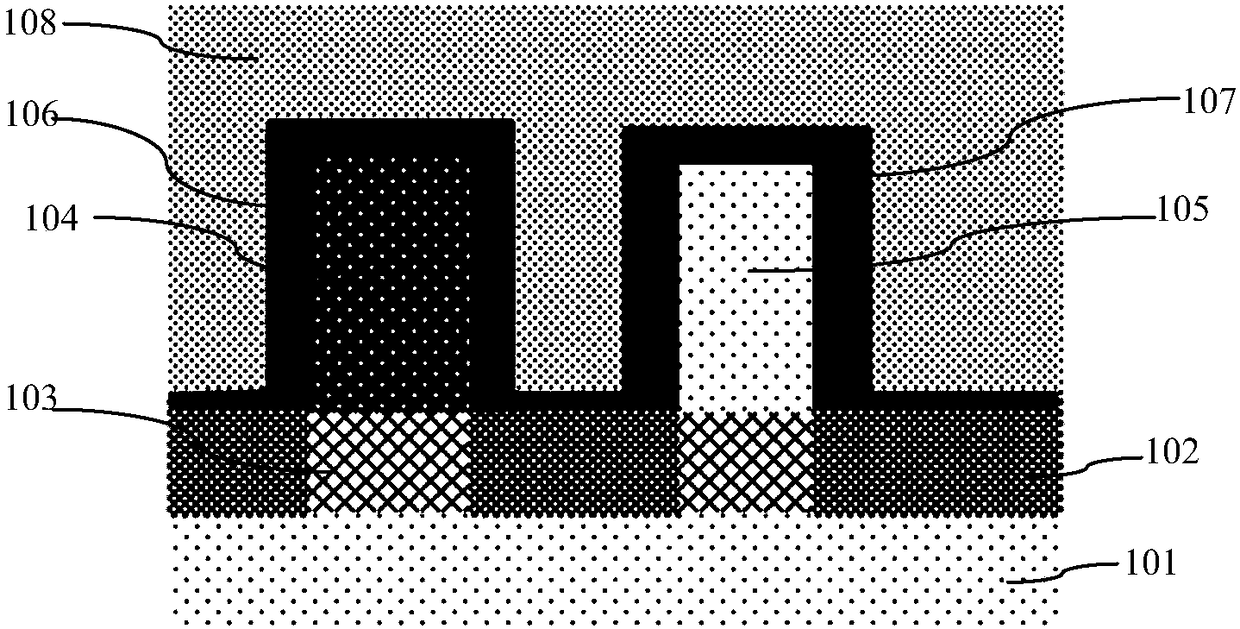

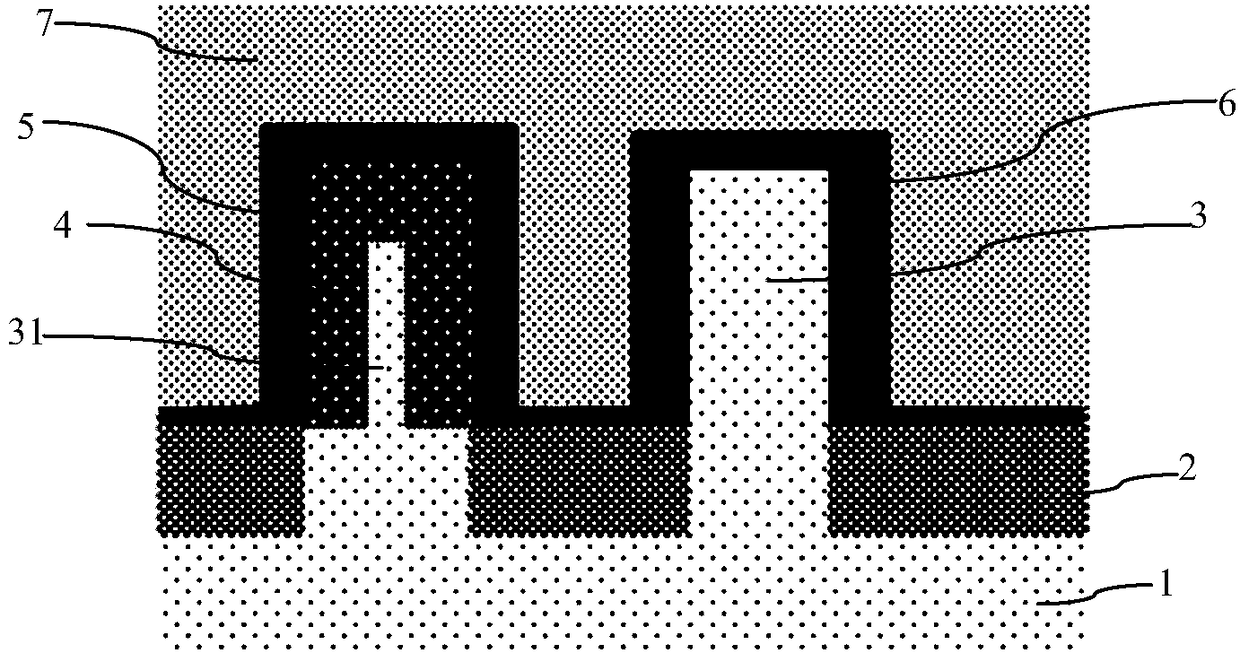

[0044] like figure 2 Shown is a cross-sectional view of the fin transistor of the embodiment of the present invention; the fin transistor of the embodiment of the present invention includes:

[0045] The silicon fin body 3 is a strip structure formed by photolithographically etching the silicon substrate 1 , and the silicon fin body 3 has an initial first width.

[0046] The bottom of the silicon fin body 3 is isolated by the first insulating layer 2 and the bottom of the silicon fin body 3 isolated by the first insulating layer 2 maintains a first width. The first insulating layer 2 is an oxide layer, for example, the first insulating layer 2 adopts shallow trench field oxygen.

[0047] A source region and a drain region are formed in the silicon fin body 3, and the formation regions of the source region and the drain region are automatically formed by dummy gates covering the top surface and side surfaces of the silicon fin body 3 having a first width. Alignment definitio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com