Method for preparing thick epitaxial layer on thin sb substrate for VDMOS device

A substrate and epitaxy technology, which is applied in the field of silicon epitaxial layer preparation process for VDMOS devices, can solve the problems of increased epitaxial debris rate, chipping, slip line, and increased difficulty in controlling the uniformity of epitaxial thickness, etc., to improve processing quality. High rate, good uniformity of thickness, and good quality of edge crystallization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

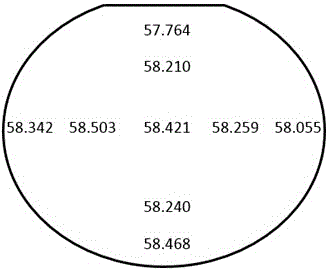

Embodiment 1

[0022] Step 1: The bottom end of the induction coil under the graphite base of the epitaxial furnace has 9 sets of distance-adjustable adjustment rods, named 4#~12# respectively. By rotating the adjustment rods to lift or pull down the position of the coil, adjust the coil The distance between each part and the graphite base can improve the temperature uniformity of the base. The scale value of the 4# adjustment rod is set to -10, the scale value of the 5# adjustment rod is set to -15, and the scale value of the 6# adjustment rod is set to -15. The scale value of the lever is set to -30, the scale value of the 7# adjusting lever is set to -30, the scale value of the 8# adjusting lever is set to 0, the scale value of the 9# adjusting lever is set to -30, 10# The scale value of the adjustment rod is set to -30, the scale value of the 11# adjustment rod is set to +3, and the scale value of the 12# adjustment rod is set to +3.

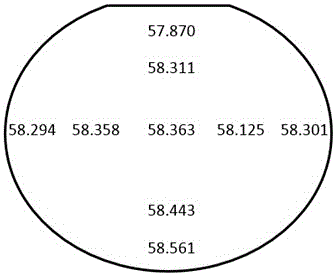

Embodiment 2

[0032] Step 1: The bottom end of the induction coil under the graphite base of the epitaxial furnace has 9 sets of distance-adjustable adjustment rods, named 4#~12# respectively. By rotating the adjustment rods to lift or pull down the position of the coil, adjust the coil The distance between each part and the graphite base can improve the temperature uniformity of the base. The scale value of the 4# adjustment rod is set to -8, the scale value of the 5# adjustment rod is set to -13, and the scale value of the 6# adjustment rod is set to -13. The scale value of the lever is set to -28, the scale value of the 7# adjusting lever is set to -28, the scale value of the 8# adjusting lever is set to +2, the scale value of the 9# adjusting lever is set to -29, 10 The scale value of the #adjusting lever is set to -30, the scale value of the 11# adjusting lever is set to +2, and the scale value of the 12# adjusting lever is set to +2.

[0033] Step 2: Use hydrogen chloride gas (HCl) to...

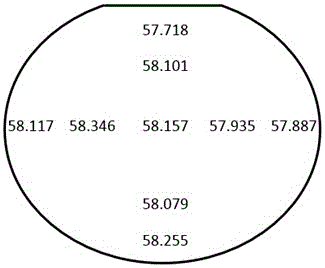

Embodiment 3

[0042] Step 1: The bottom end of the induction coil under the graphite base of the epitaxial furnace has 9 sets of distance-adjustable adjustment rods, named 4#~12# respectively. By rotating the adjustment rods to lift or pull down the position of the coil, adjust the coil The distance between each part and the graphite base can improve the temperature uniformity of the base. The scale value of the 4# adjustment rod is set to -7, the scale value of the 5# adjustment rod is set to -13, and the scale value of the 6# adjustment rod is set to -13. The scale value of the lever is set to -28, the scale value of the 7# adjusting lever is set to -30, the scale value of the 8# adjusting lever is set to +2, the scale value of the 9# adjusting lever is set to -27, 10# Set the scale value of the adjustment lever to -27, set the scale value of the 11# adjustment lever to +1, and set the scale value of the 12# adjustment lever to +1;

[0043] Step 2: Use hydrogen chloride (HCl) to polish th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More