Method for forming fin portion of fin field effect tube and fin field effect tube

A fin-type field effect transistor and fin technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of large size, poor performance and stability, leakage current, etc., and achieve small-sized semiconductors. The effect of precise manufacturing processes, improved performance, improved performance and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] A method for forming a fin portion of a fin field effect transistor in an existing process includes the steps of:

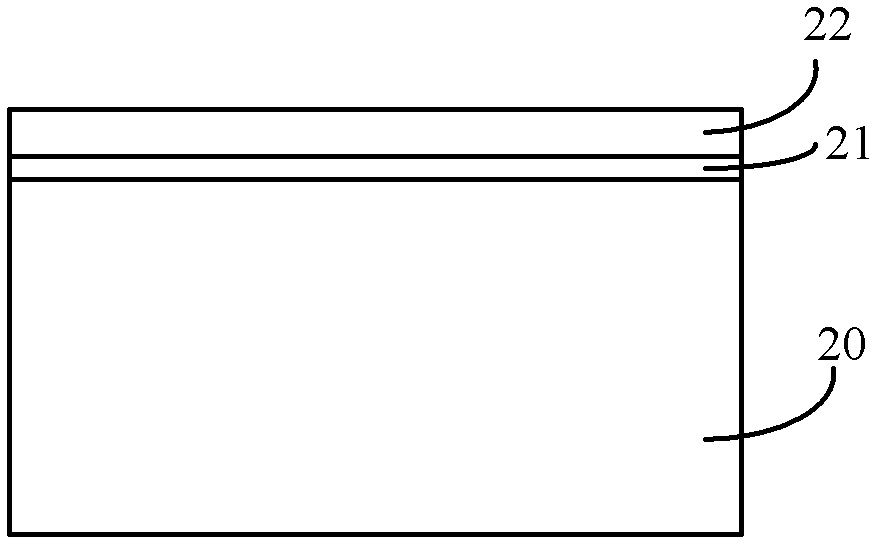

[0055] Please refer to figure 2 A semiconductor substrate 20 is provided, an oxide pad layer 21 is formed on the surface of the semiconductor substrate 20 , and a hard mask layer 22 is formed on the surface of the oxide pad layer 21 .

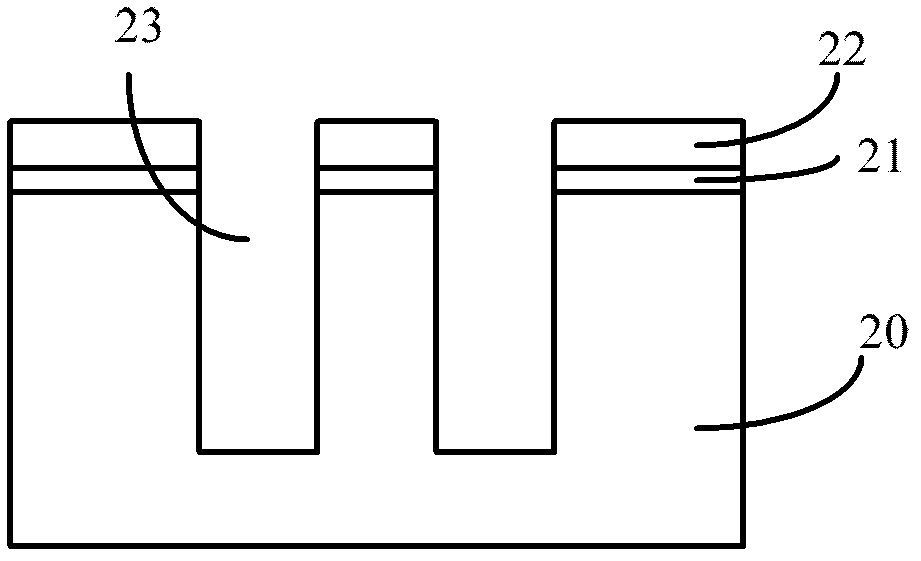

[0056] Please refer to image 3 , pattern the hard mask layer 22 and the oxide liner layer 21 , and use the patterned hard mask layer 22 and the oxide liner layer 21 as a mask to etch the semiconductor substrate 20 to form trenches 23 .

[0057] The formation process for forming the trench 23 is: dry etching or wet etching, preferably dry etching, because of its anisotropy, the shape of the trench 23 can be precisely formed.

[0058]However, the etching process is likely to cause lattice damage to the surface of the semiconductor substrate 20, thereby affecting the progress of the subsequent process and further affecting...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com