Method for preparing silicon-based high-mobility CMOS (complementary metal-oxide-semiconductor) provided with III-V/Ge channel

A high-mobility, silicon-based technology used in microelectronics to address misfit dislocations, unrealized integration, and unsatisfactory III-V or germanium material quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

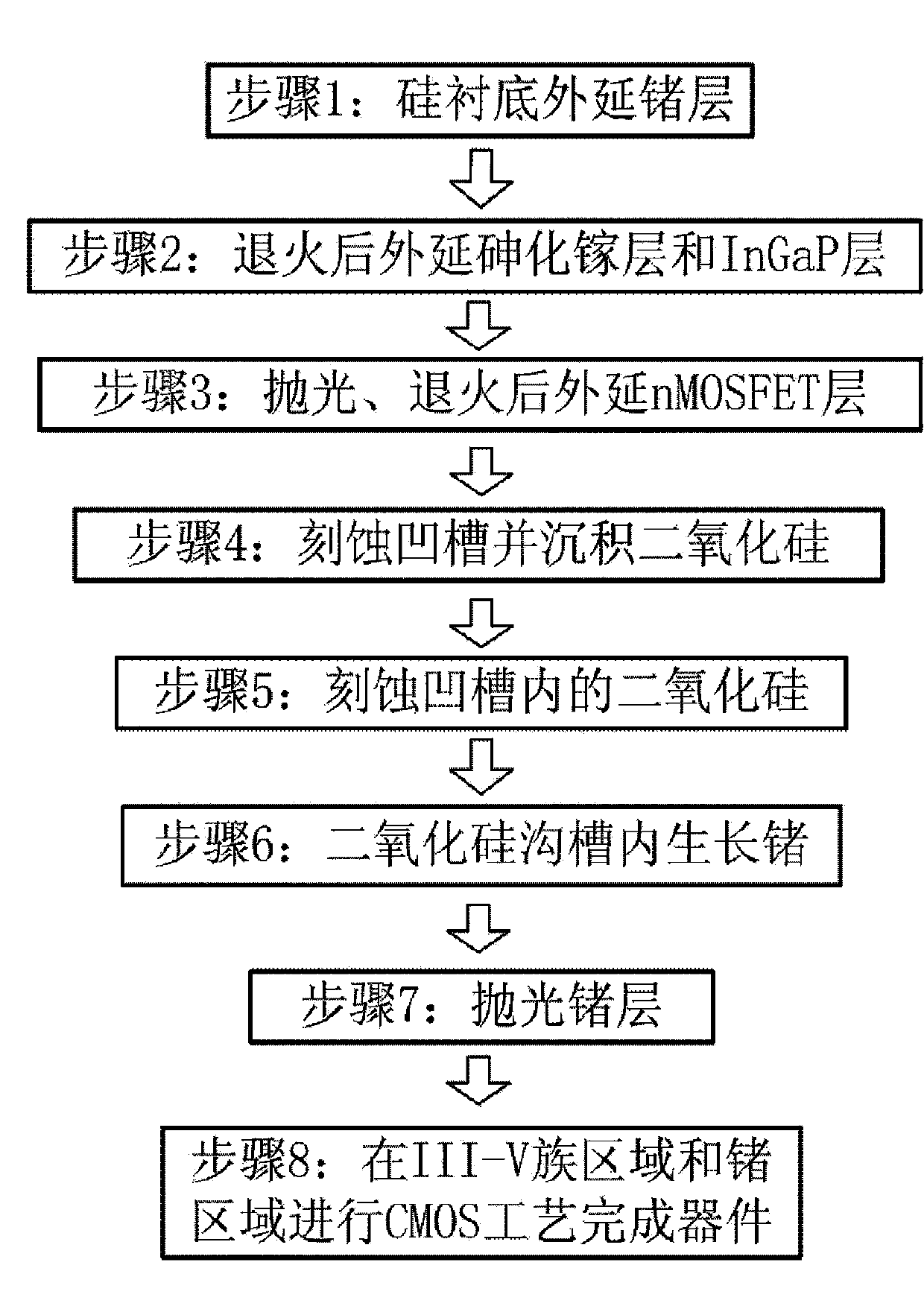

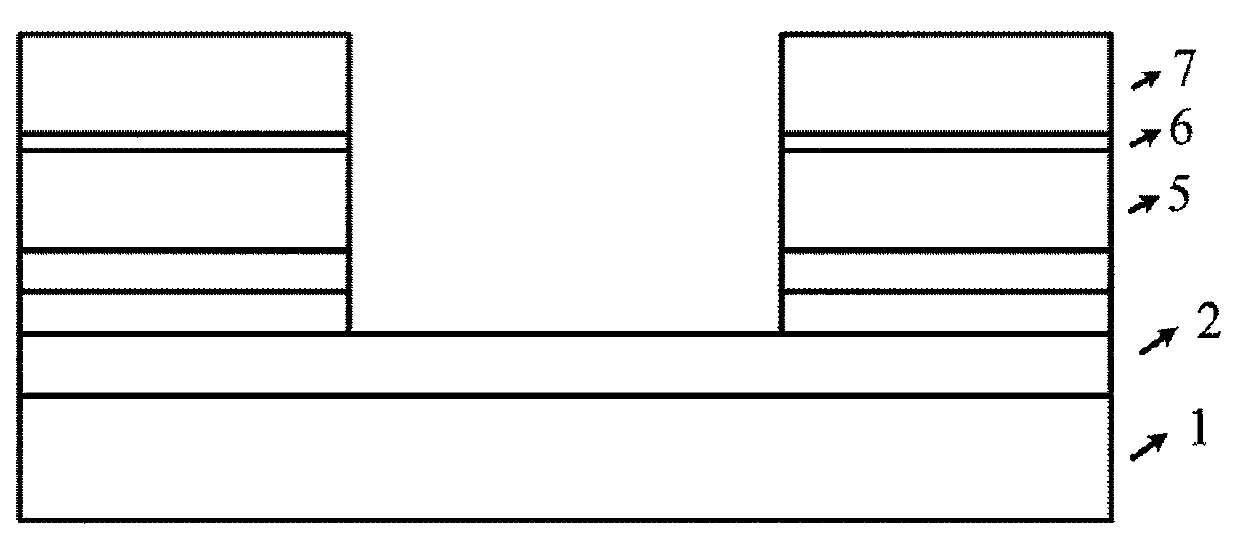

[0024] see figure 1 and refer to Figure 2 to Figure 9 , the invention provides a CMOS preparation method of a silicon-based high-mobility III-V / Ge channel, comprising the following steps:

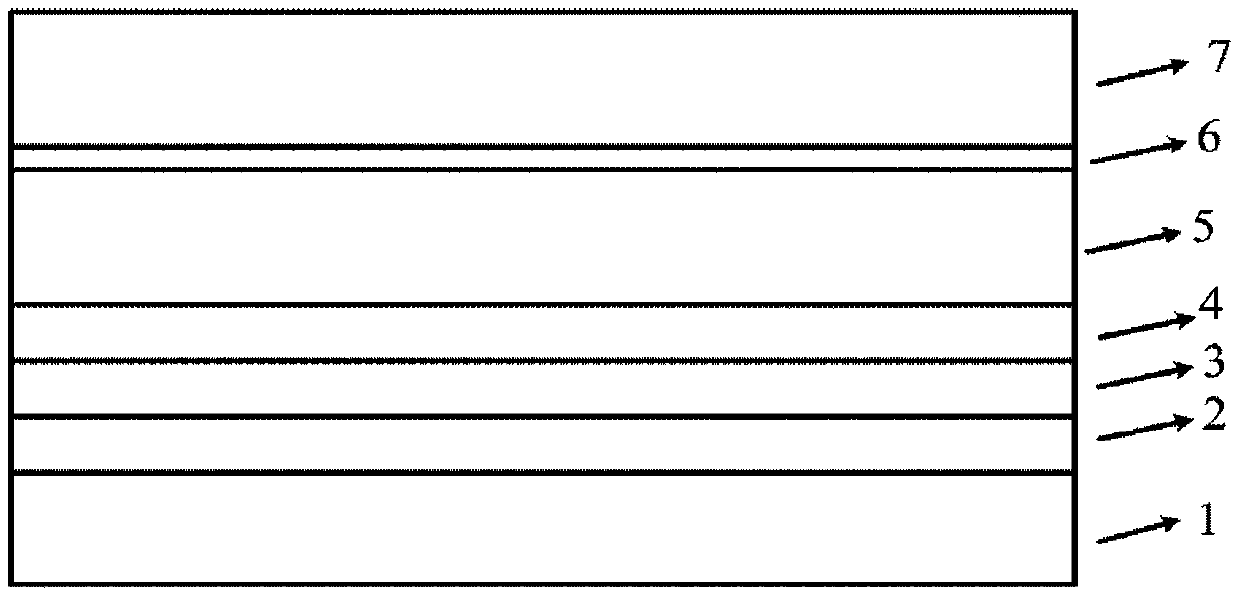

[0025] Step 1: On the cleaned silicon substrate 1, a germanium layer 2 is grown by ultra-high vacuum chemical vapor deposition (see figure 2 ). The silicon substrate 1 is a (100) substrate that is 4° off the [011] direction. The substrate off-angle is to ensure that atomic steps are formed on the surface of the final germanium layer to suppress the reverse domain when gallium arsenide is nucleated. The off angle is generally 3° to 6°; the transition of the lattice constant to gallium arsenide is realized through the germanium layer, and the defect density of the germanium layer needs to be 1×10 6 cm -2 Below, the surface roughness RMS is less than 0.5 nm.

[0026] Step 2: Put the silicon substrate 1 into the MOCVD reaction chamber immediately, after the first annealing, grow the low-...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More