Fin type field effect transistor formation method

A fin field effect transistor and fin technology are applied in semiconductor devices, electrical components, circuits, etc., and can solve the problem that the electrical performance of the fin field effect transistor needs to be improved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

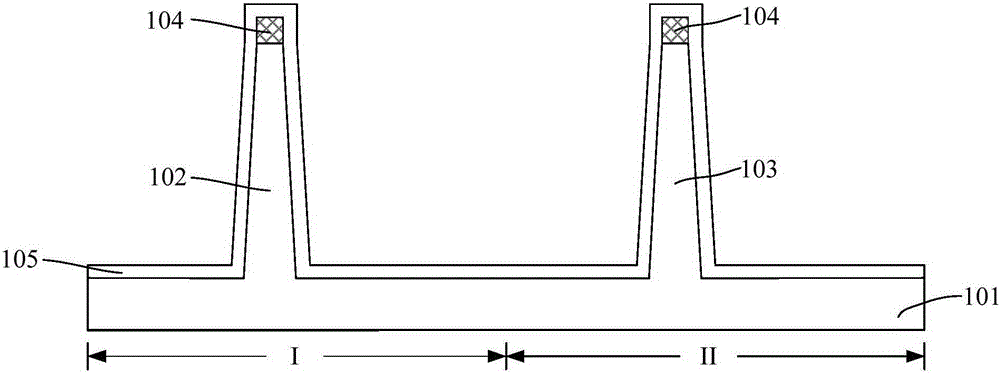

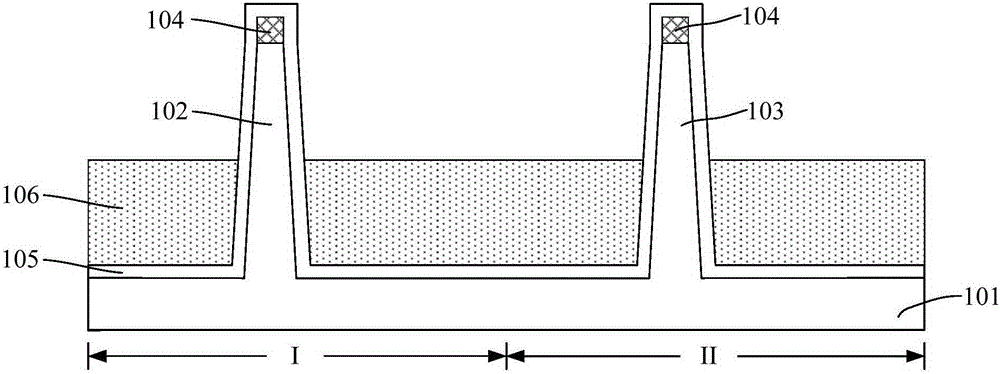

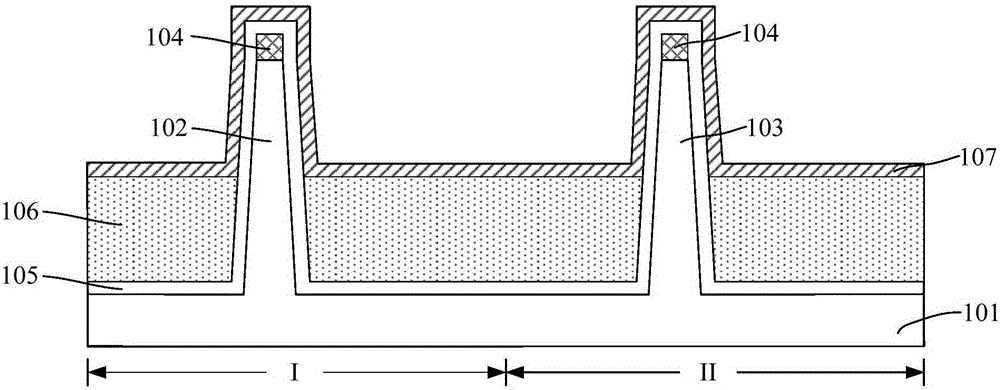

[0034] It can be seen from the background art that the electrical performance of the fin field effect transistor formed in the prior art needs to be improved.

[0035] It has been found through research that the distance between the bottom of the fin and the gate structure of the fin field effect transistor is relatively long, the ability of the gate structure to control the bottom of the fin is weak, and the doping concentration of the fin is small, and the channel The space charge region of the area is widened under the electric field, and the space charge region of the source region and the drain region are connected, resulting in a punch through phenomenon between the source region and the drain region at the bottom of the fin field effect transistor, resulting in a fin field effect The electrical performance of the tube is low. And in order to improve the electrical performance of the fin field effect transistor, the dopant is usually doped in the substrate, the dopant in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More