Efficient triple-junction solar cell and manufacturing method thereof

A solar cell and manufacturing method technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of limited conversion rate of solar cells, complex flip-chip growth process, affecting cell efficiency, etc., to reduce dark current and reduce fragmentation rate. , spectral absorption and reasonable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

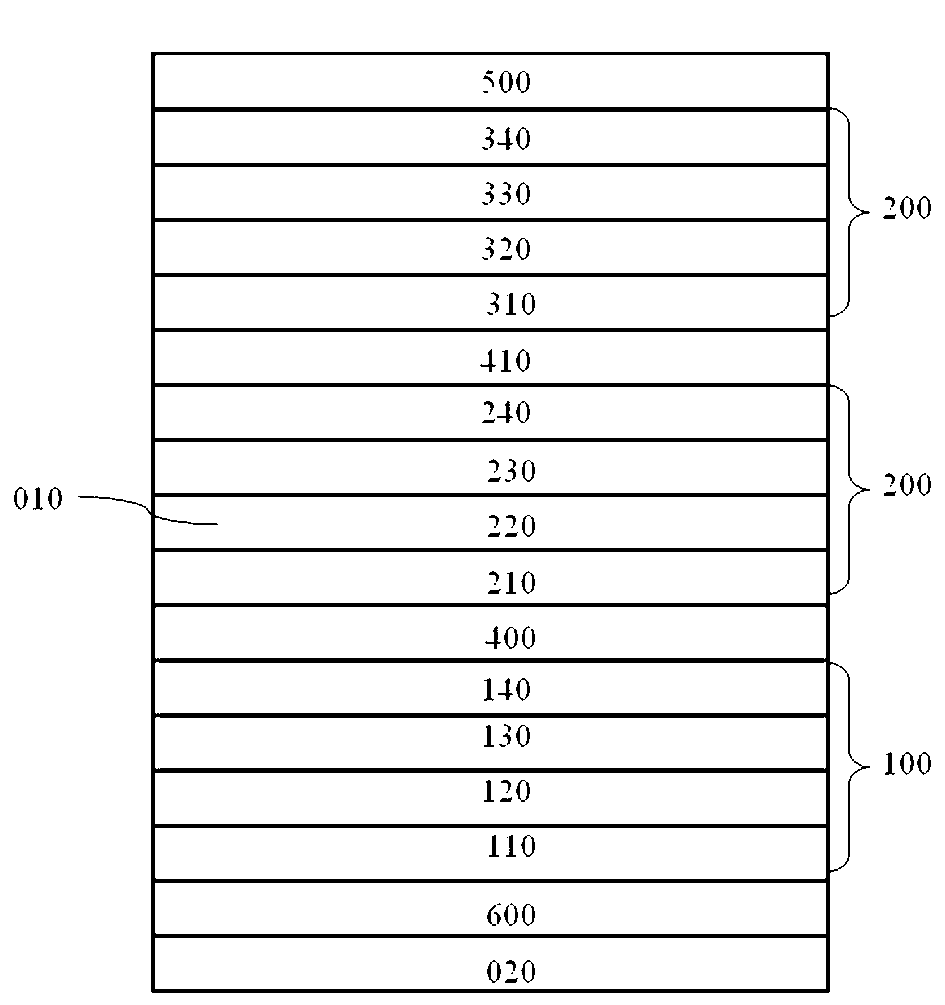

[0021] figure 1 It is a schematic structural diagram of a high-efficiency triple-junction solar cell implemented according to the present invention.

[0022] Such as figure 1 As shown, a high-efficiency triple-junction solar cell includes a support substrate 020, a DBR reflective layer 600, a bottom cell 100, a middle cell 200, a top cell 300, a highly doped capping layer 500, and tunnel junctions between each junction cell. 410, 420 connections. Wherein, the bottom cell 100 is grown upside down on the back side of the growth substrate 010, the middle cell uses the growth substrate 010 itself as the base region 220, the emitter region 230 is epitaxially grown on the front side of the growth substrate, and the top cell is formed on the middle cell . The specific structure thereof is described in detail below.

[0023] The growth substrate 010 is an ultra-thin substrate that has been polished on both sides. In the present invention, in this implementation, a p-type GaAs sub...

Embodiment 2

[0039] This embodiment is a manufacturing process of a high-efficiency triple-junction solar cell described in Example 1, which includes the formation process of the sub-cells 100, 200, 300, and layers between the sub-cells.

[0040] Concrete preparation process comprises the following steps:

[0041] In the first step, a growth substrate 010 is provided. The growth substrate 010 is an ultra-thin substrate that has been polished on both sides. In this implementation, a p-type GaAs substrate with a thickness of about 200 microns is selected, and its doping concentration is 2×10 17 cm -3 ~5×10 17 cm -3 .

[0042] In the next step, a neutron pool 020 is formed on the front surface of the growth substrate 010 with a band gap of 1.4-1.5eV. The specific process is as follows: In the MOCVD system, the above-mentioned GaAs substrate 010 polished on both sides is used as the base region 220 of the battery, and the n-type emitter region 230 is epitaxially grown on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More