Dual-gate field-effect transistor

A field-effect transistor, double-gate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problem of unreported semiconductor manufacturing processes, and achieve the advantages of avoiding secondary effects, small sub-threshold swings, and reducing energy consumption. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] It is known from the prior art that the green transistor has lower energy consumption and stable device characteristics in a small size, which meets the low energy consumption requirement of VDD scaling down. On this basis, the present invention provides a new dual-gate pole field effect transistor.

[0044] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

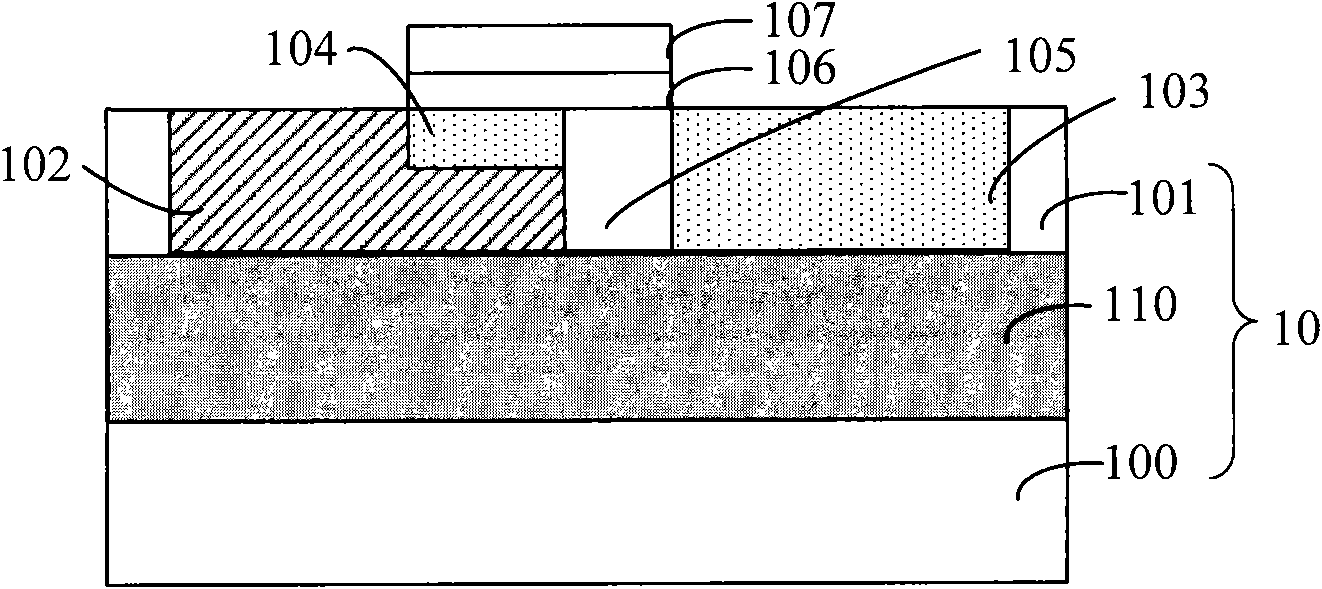

[0045] Figure 4 It is a schematic cross-sectional structure diagram of the double gate field effect transistor of the first embodiment provided by the present invention. include:

[0046] a device layer 200 having opposing first and second surfaces;

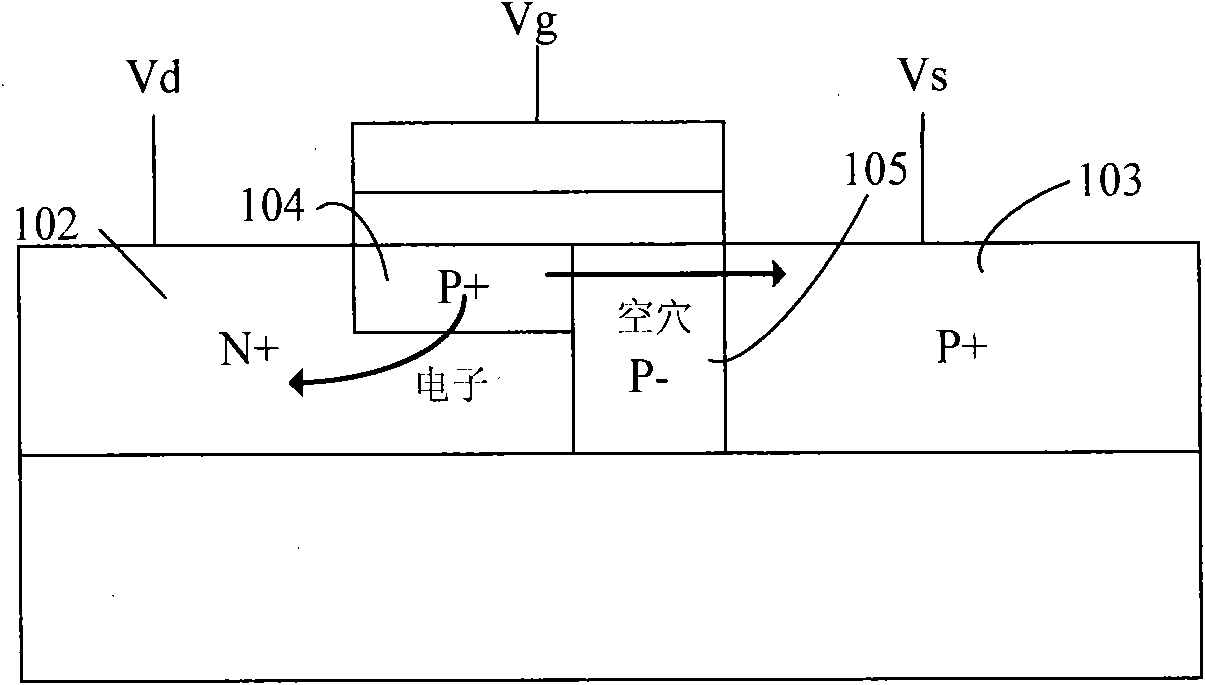

[0047] A source 1 and a drain 2 that are isolated from each other and have different conductivity types in the device layer 200;

[0048] a channel region between source 1 and drain 2;

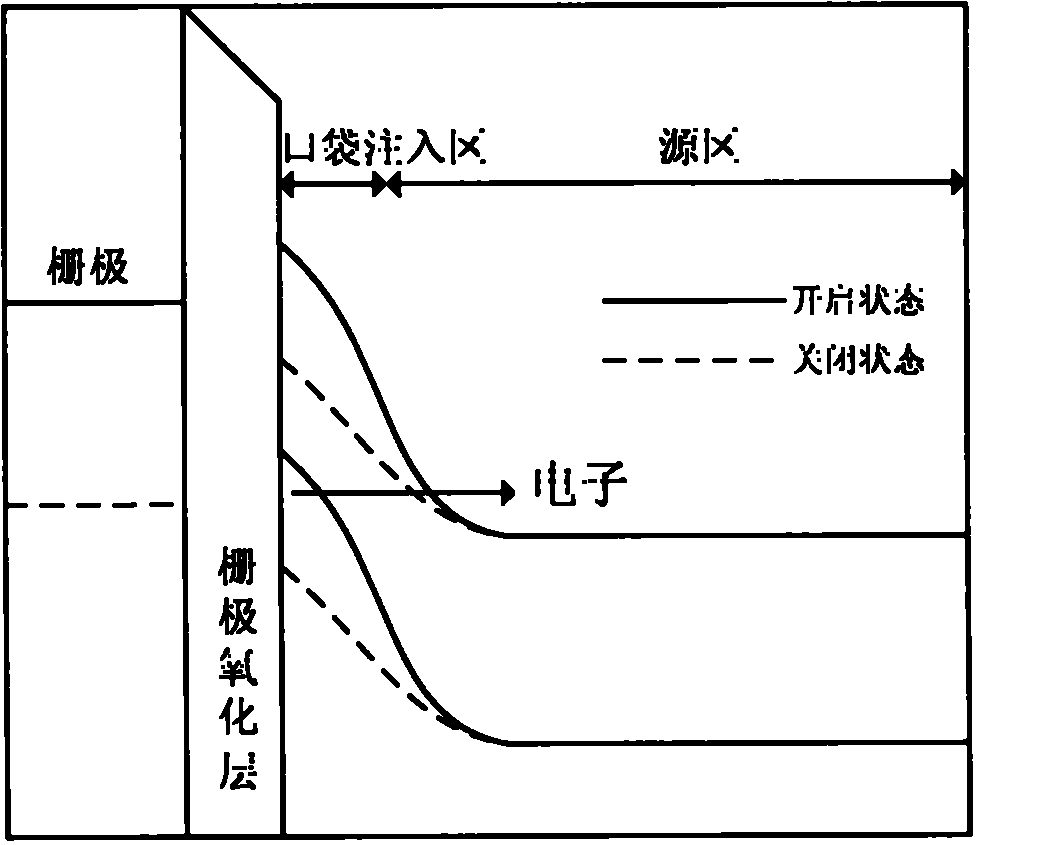

[0049] The channel region sequentially includes a first pocket injection region 3a, a source con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More