High voltage low resistance MOSFET device and its manufacture method

A device and semiconductor technology, applied in the field of metal oxide semiconductor field effect transistors, can solve the problems of increasing on-resistance, hindering the flow of channel electrons, increasing on-resistance, etc., to reduce on-resistance and improve device performance. performance, the effect of eliminating channel bend structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

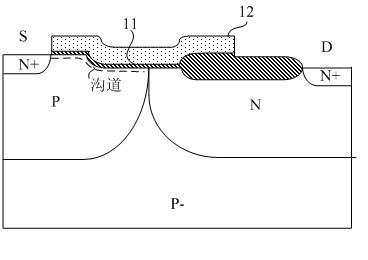

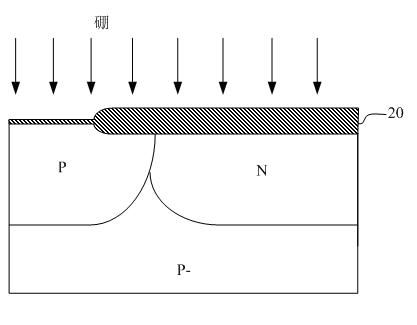

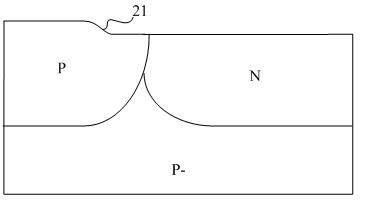

[0020] Figure 3A An embodiment of a high-voltage lateral N-type MOSFET (NMOS) 30 of the present invention is shown, wherein the gate region 31 of the high-voltage NMOS 30 is relatively short compared with the prior art, the gate region 31 and the semiconductor step 21 do not overlap, and the semiconductor step 21 is located outside the edge of the gate region 31, so that the channel region has a horizontal structure. Such as Figure 3A As shown, in the illustrated embodiment, the high voltage NMOS 30 includes a substrate 300 , a drain region D, a source region S and a gate region G. The illustrated substrate 300 is P-type doped. The drain region D and the source region S are formed on the P-type substrate 300 and are respectively located on two sides of the gate region G. From the upper surface of the P-type substrate 300, an N well 301 is formed on the drain region D side. A high concentration N+ drain contact region 308 is contained in the N well 301 . In another embodi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More