Nonvolatile memory with error detection/correction circuit and reading and writing method thereof

An error correction circuit and memory technology, applied in static memory, memory system, read-only memory, etc., can solve the problems of reducing the service life of EEPROM, wasting writing operation space, and reducing storage flexibility, so as to save area cost and reduce usage Influence of lifespan, effect of improving flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

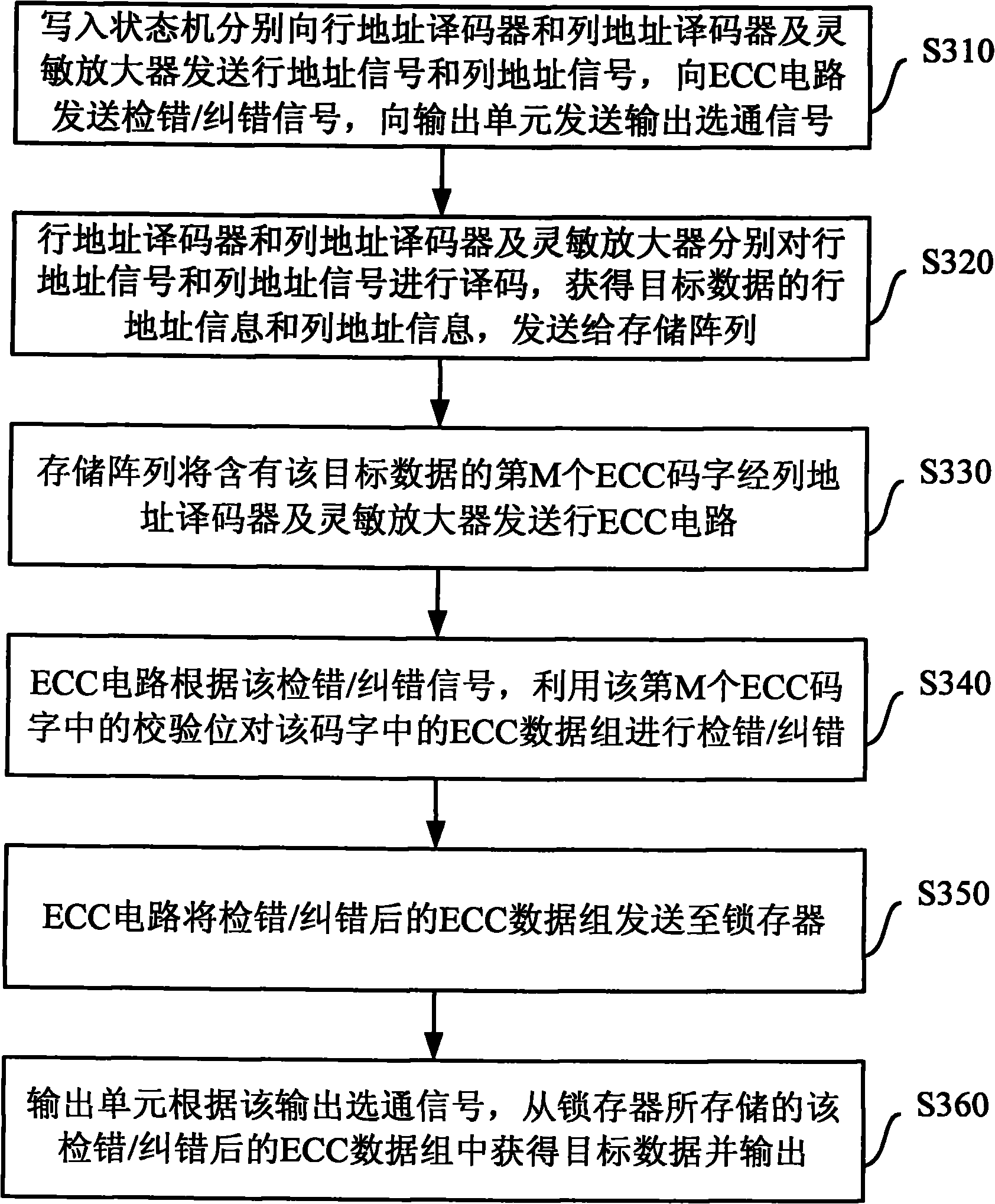

[0044] The implementation of the present invention will be described in detail below in conjunction with the accompanying drawings and examples, so as to fully understand and implement the process of how to apply technical means to solve technical problems and achieve technical effects in the present invention.

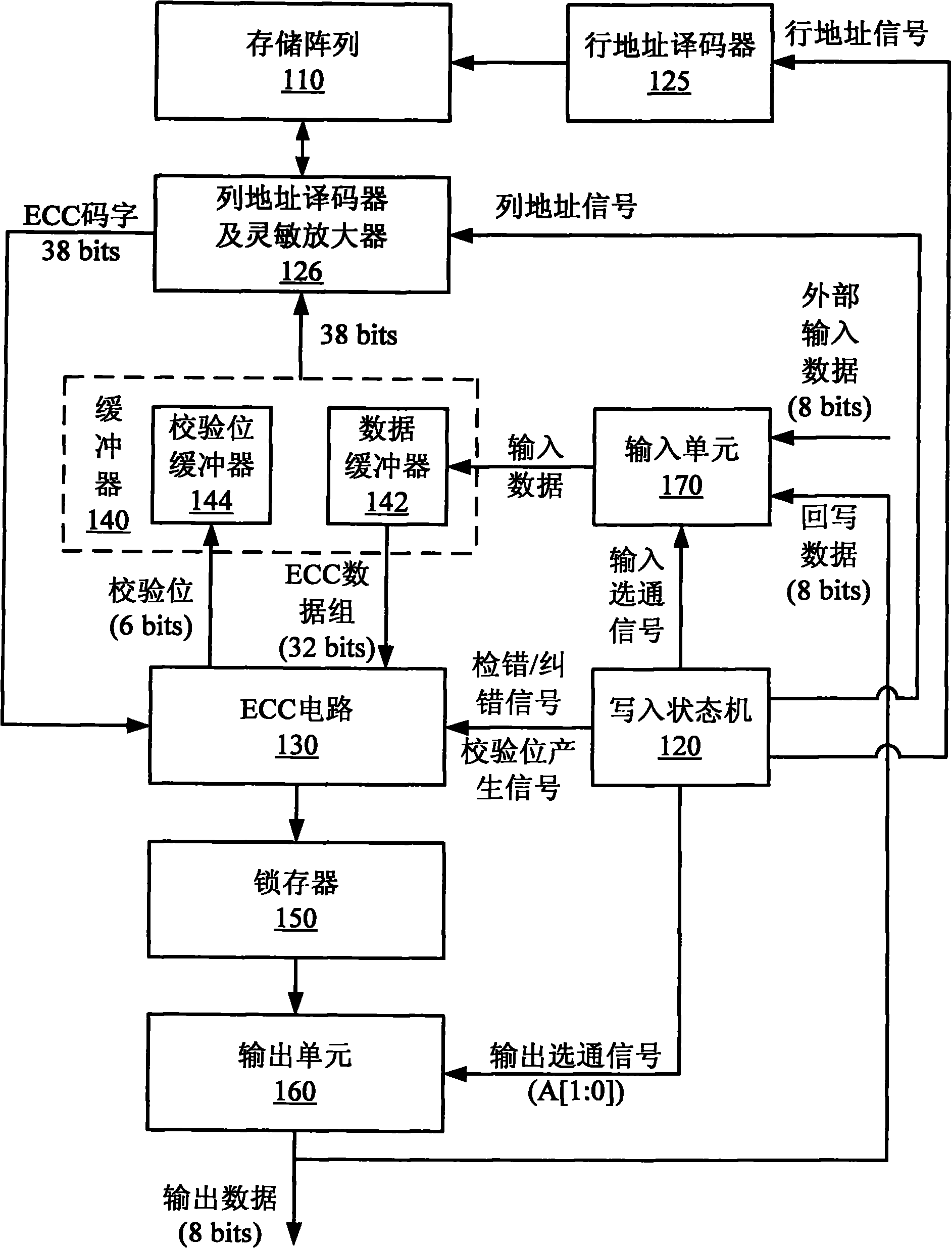

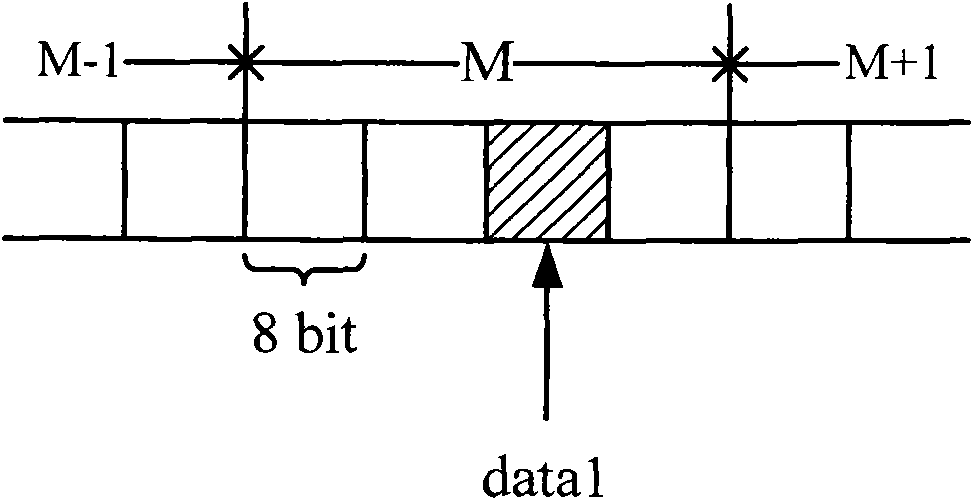

[0045] figure 1 It is a schematic composition diagram of an embodiment of the non-volatile memory of the present invention, and the external interface of the non-volatile memory transmits data in units of bytes. In this embodiment, the ECC code word is 38 bits, including an ECC data set (ECC data set) and check bits, wherein the ECC data set is 32 bits, and the check bits are 6 bits. With 8 bits as a byte (byte), the ECC data group has a total of 4 bytes (at least two bytes). Unless otherwise specified below, in the following embodiments of the present application, one ECC data group contains 4 bytes, and one byte contains 8 bits.

[0046] Such as figure 1As shown,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com