CMOS (Complementary Metal-Oxide-Semiconductor) inverter pair based method and circuit for designing high-speed chaotic oscillator

A design method, inverter technology, applied in power oscillators, electrical components, digital transmission systems, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with drawings and embodiments.

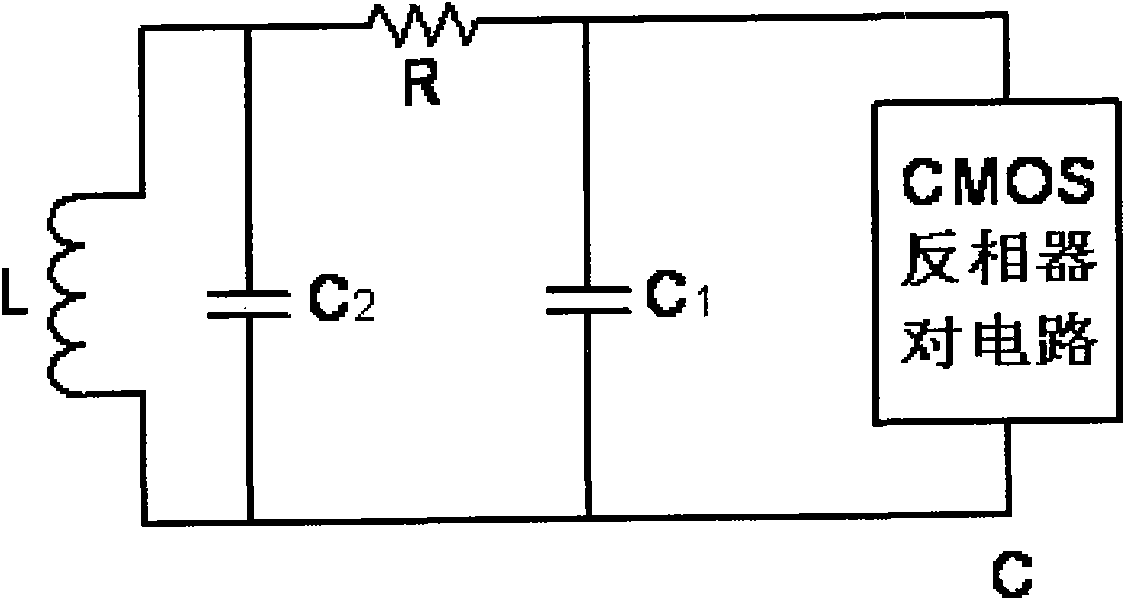

[0024] Such as figure 1 As shown, the chaotic oscillator of the present invention is based on the traditional Chua's circuit, and the negative resistance circuit formed by the CMOS inverter pair circuit is used to replace the negative resistance circuit based on the operational amplifier in the traditional Chua's circuit to generate faster chaotic oscillation .

[0025] Such as figure 1 Shown, the circuit structure of the present invention is: one end of inductance L and electric capacity C 2 One end of the resistor R is connected to one end of the resistor R, the other end of the resistor R and the capacitor C 1 One end of the CMOS inverter is connected to one end of the circuit, the other end of the inductor L, the capacitor C 2 the other end of the capacitor C 1 The other end of is connected with the other end of the CMOS inverter pair circuit.

[0026] On the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More