Patents

Literature

39 results about "Chua's circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

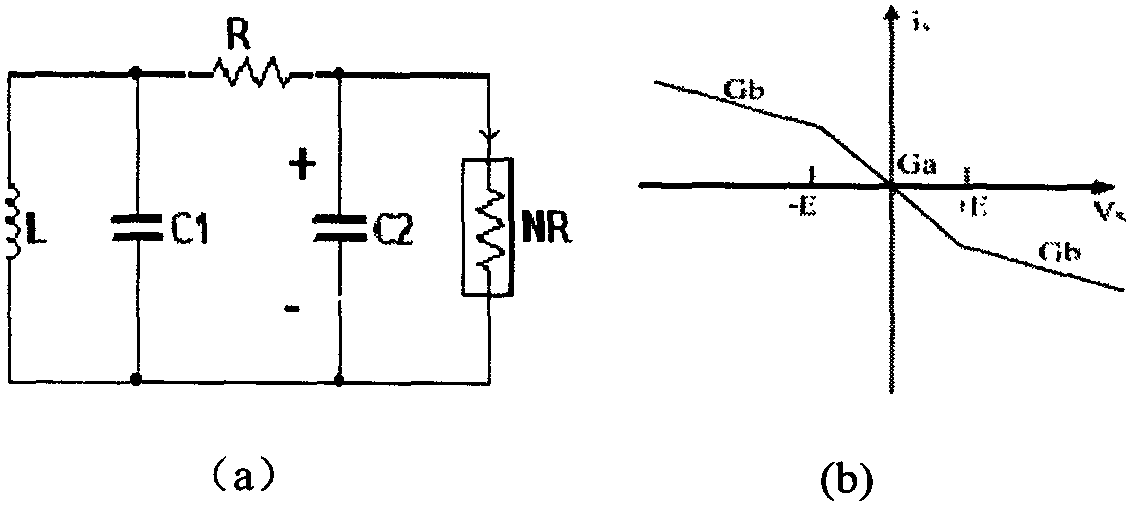

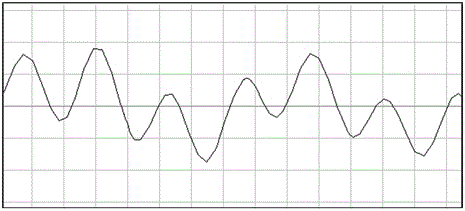

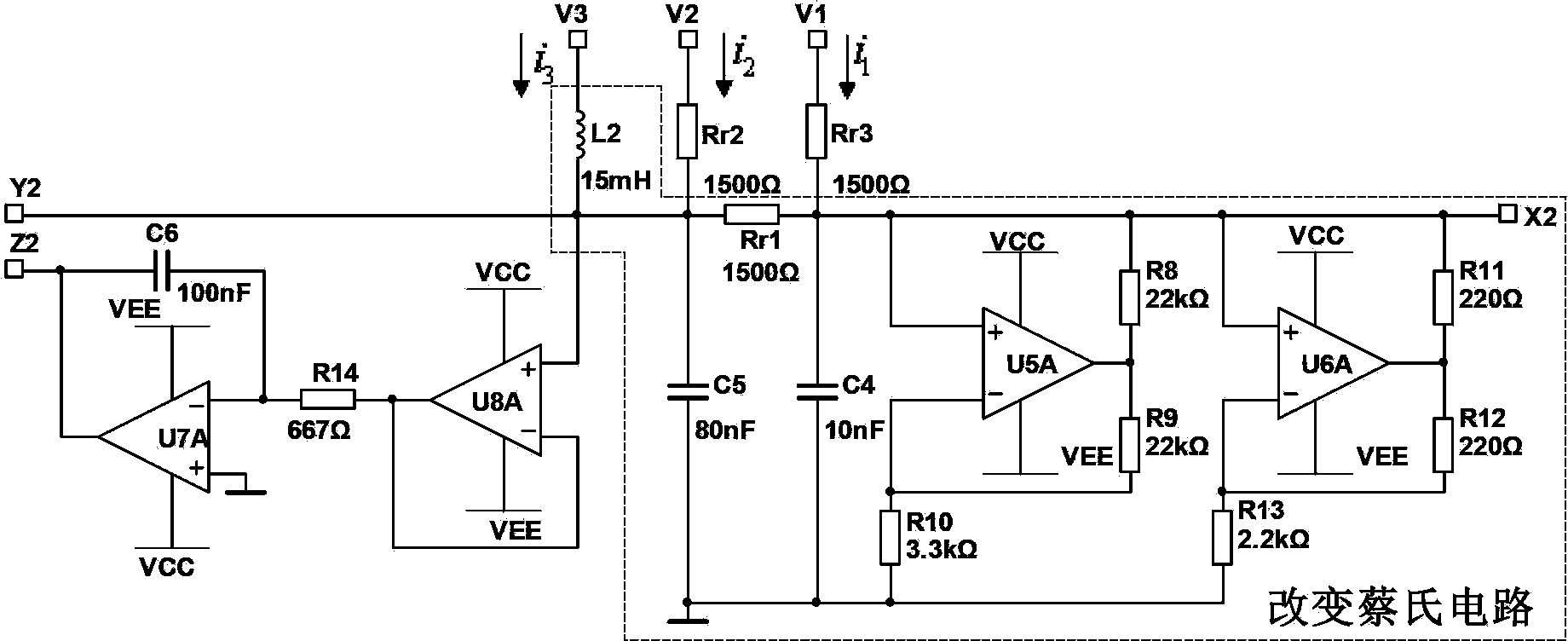

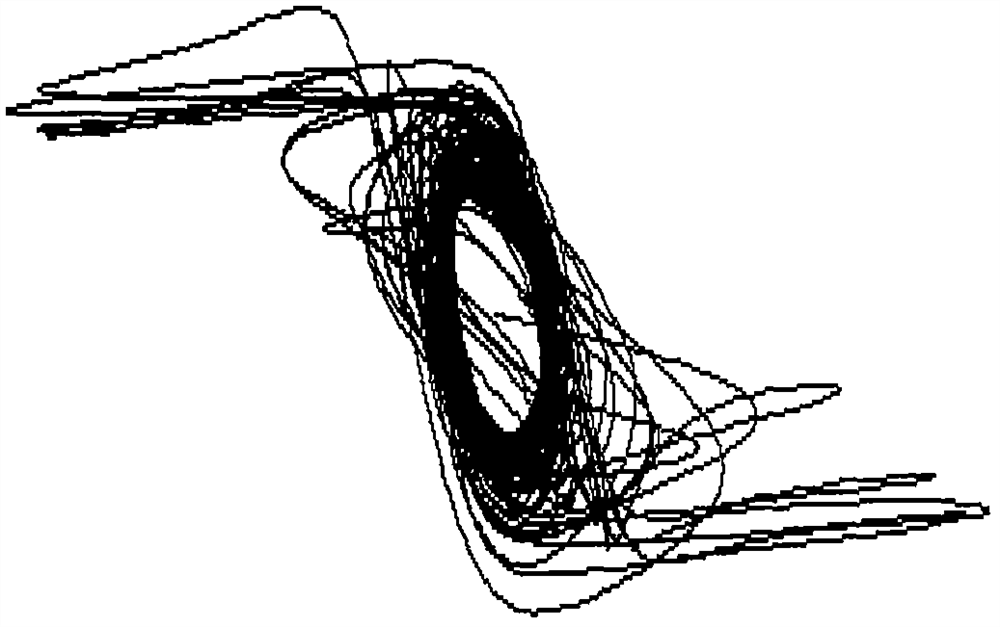

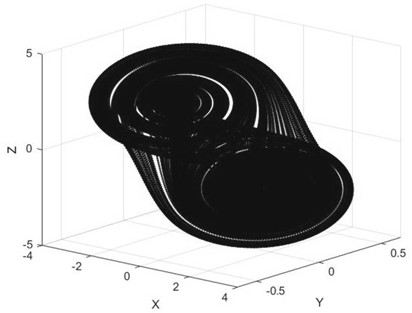

Chua's circuit (also known as a Chua circuit) is a simple electronic circuit that exhibits classic chaotic behavior. This means roughly that it is a "nonperiodic oscillator"; it produces an oscillating waveform that, unlike an ordinary electronic oscillator, never "repeats". It was invented in 1983 by Leon O. Chua, who was a visitor at Waseda University in Japan at that time. The ease of construction of the circuit has made it a ubiquitous real-world example of a chaotic system, leading some to declare it "a paradigm for chaos".

Programmable chaos generator and process for use thereof

InactiveUS6842745B2Modulated-carrier systemsElectric analogue storesSwitching signalSignal generator

A chaotic signal generator includes a set of elements connected together for generating chaotic signals. The connection scheme may correspond to the circuit generally referred to as Chua's circuit, particularly when implemented as a cellular neural network. Interposed in the connection scheme is at least one switch, such as a MOS transistor. Opening and closing of the switch causes variation in the chaotic dynamics of the generated signals. A command signal applied to the switch may correspond to a modulating signal for transmission on a channel, such as a high noise channel. The modulating signal may be a binary signal, and the command signal may be a switching signal having a frequency that increases or decreases depending on the logic level of the binary signal.

Owner:STMICROELECTRONICS SRL

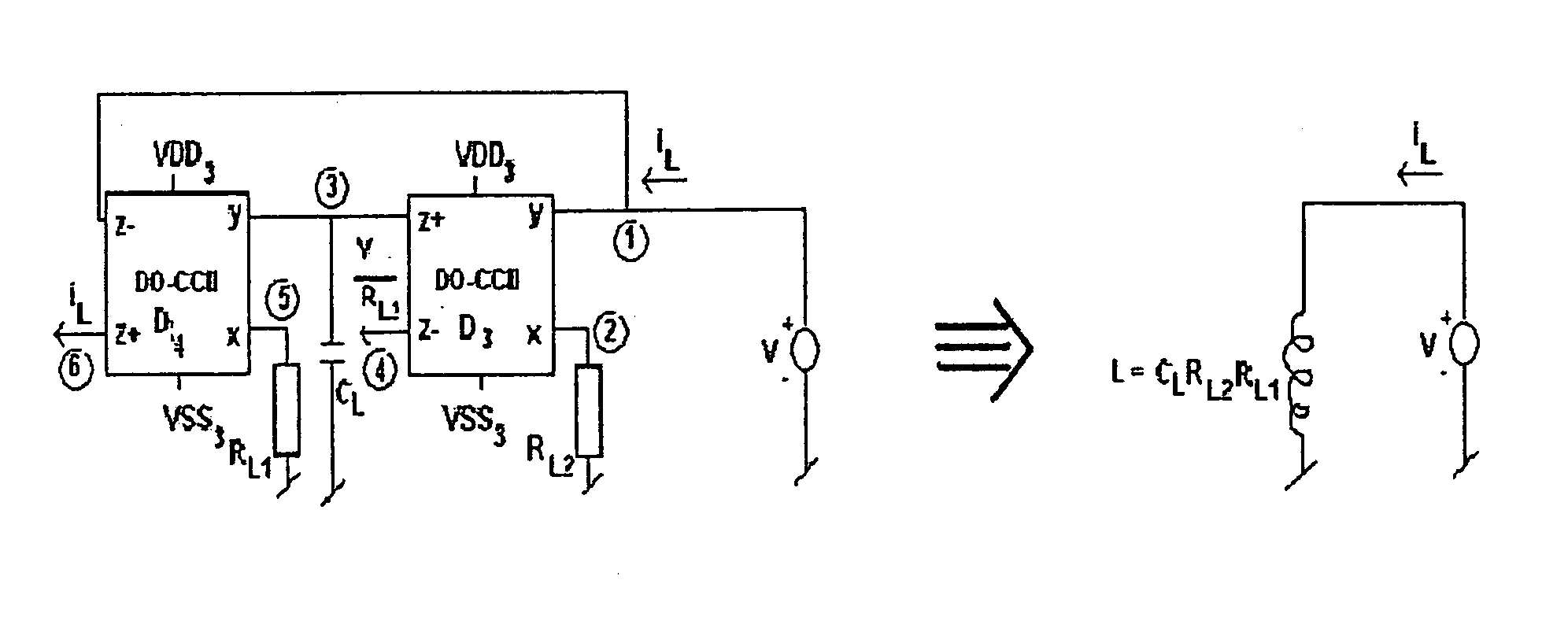

Chua's circuit and it's use in hyperchaotic circuit

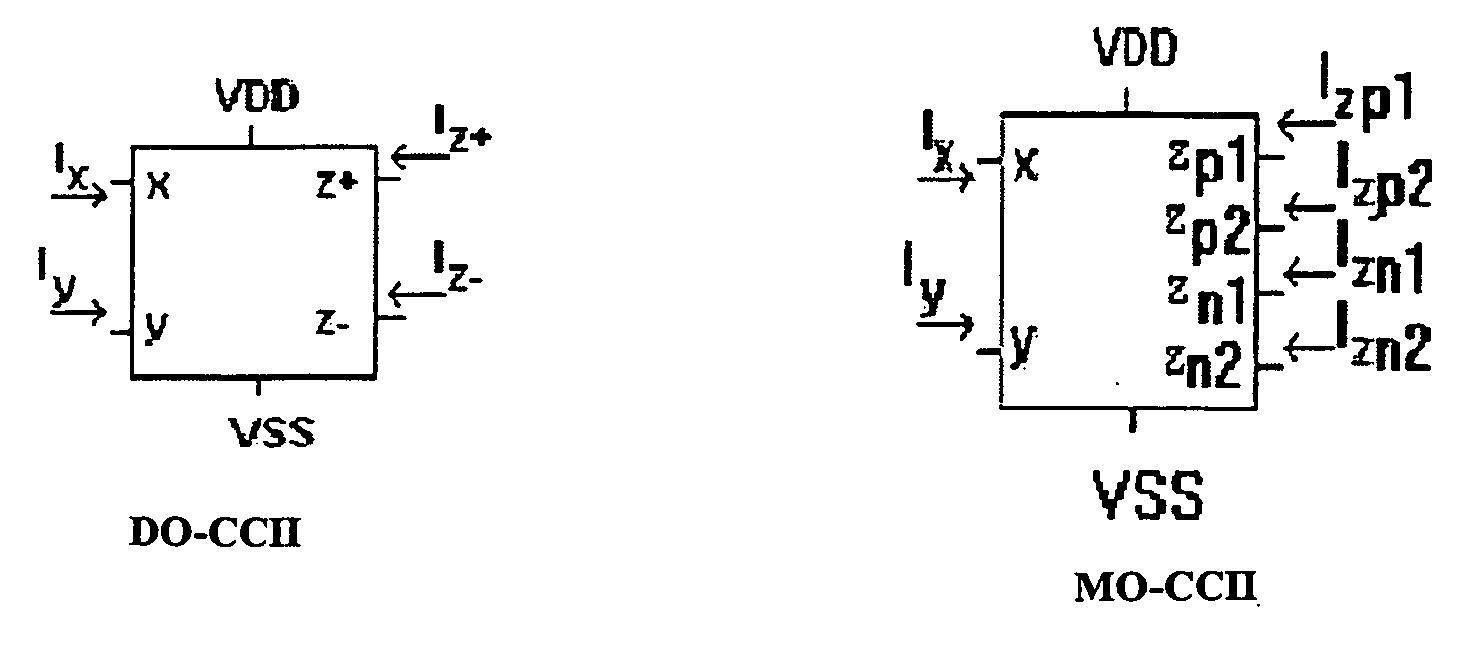

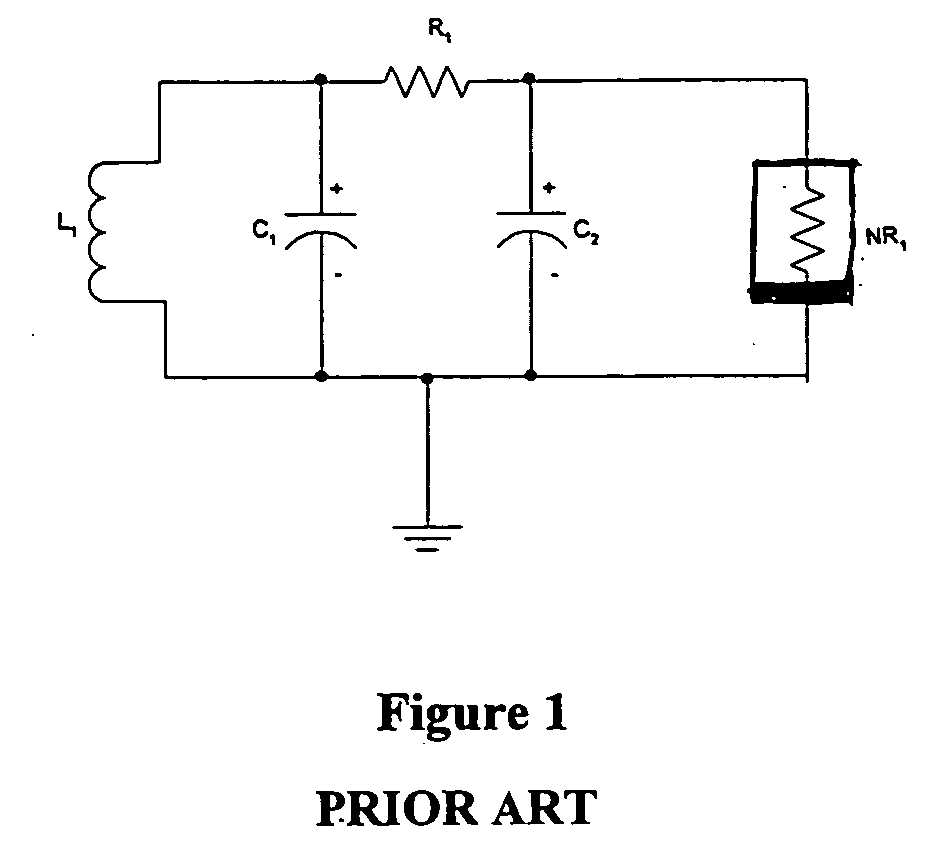

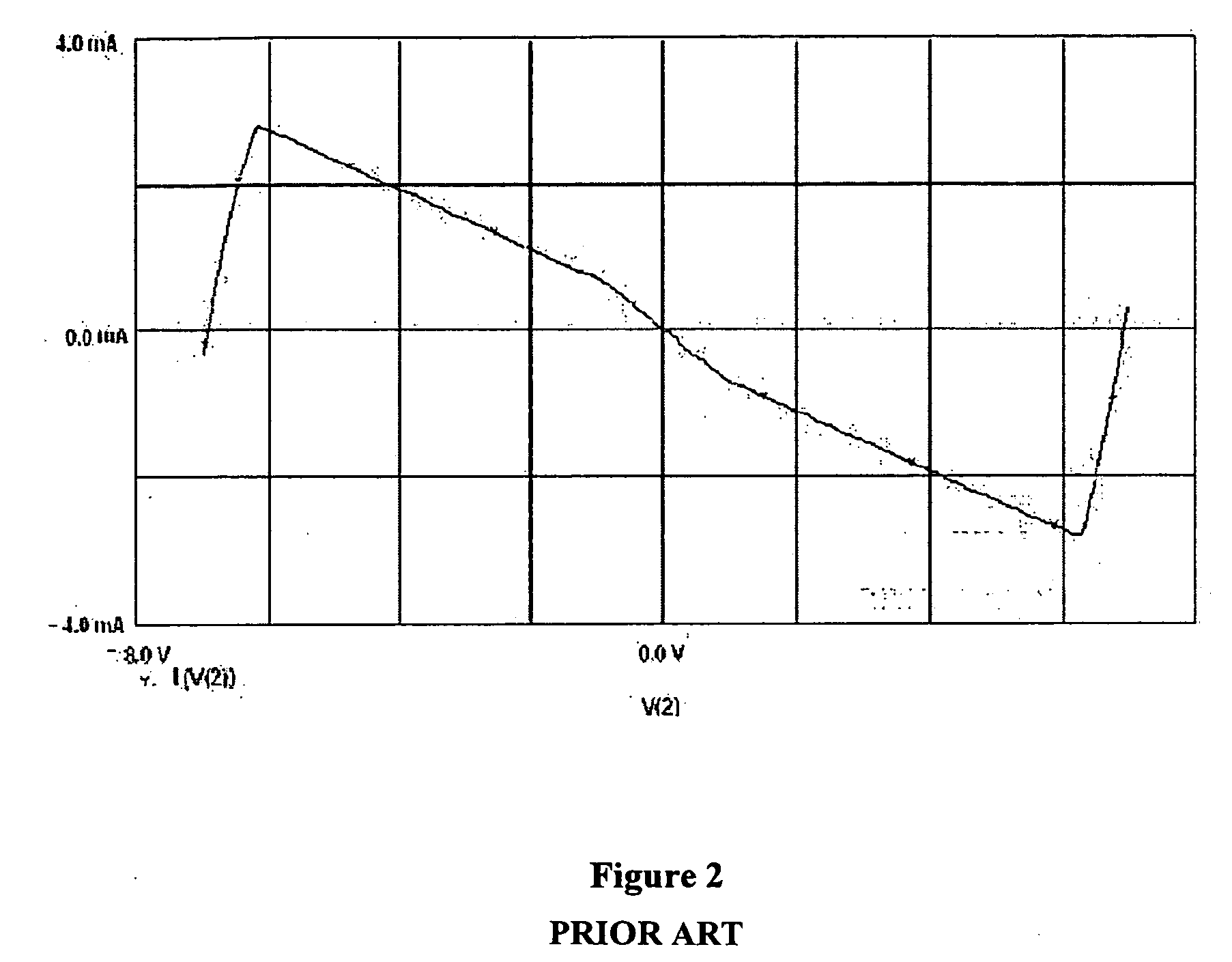

InactiveUS20050134409A1Minimal useNegative-feedback-circuit arrangementsNetwork simulating negative resistancesState variableEngineering

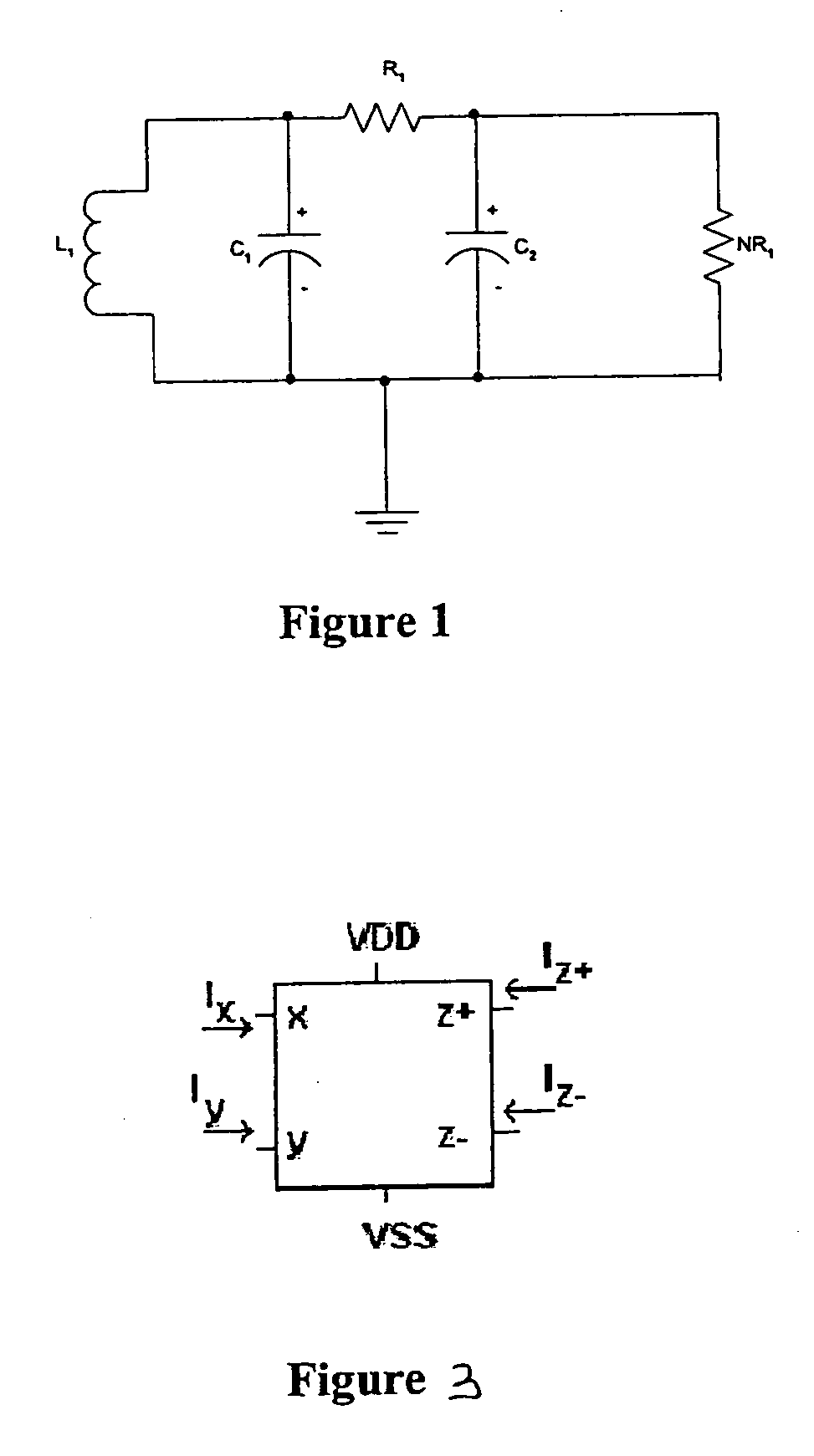

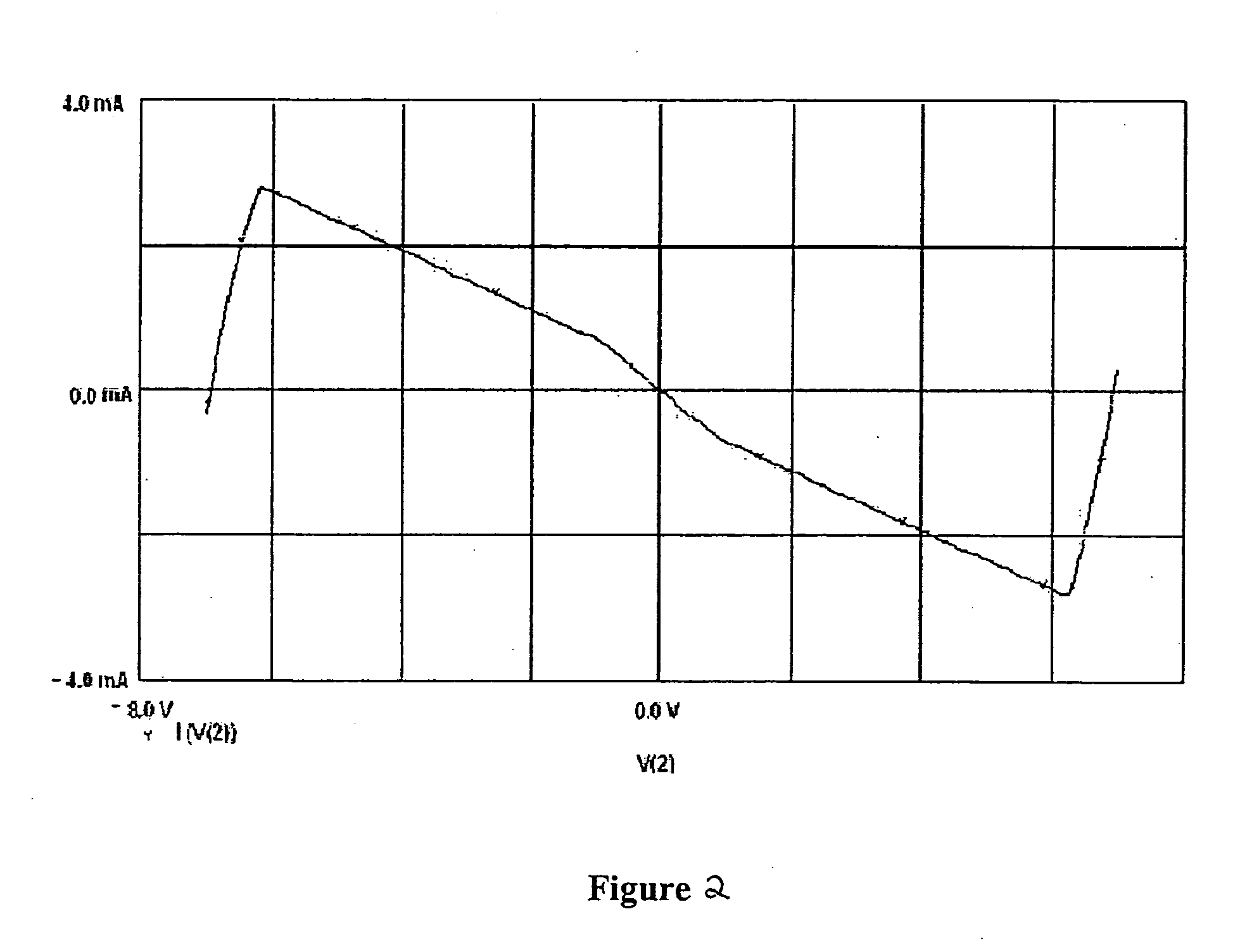

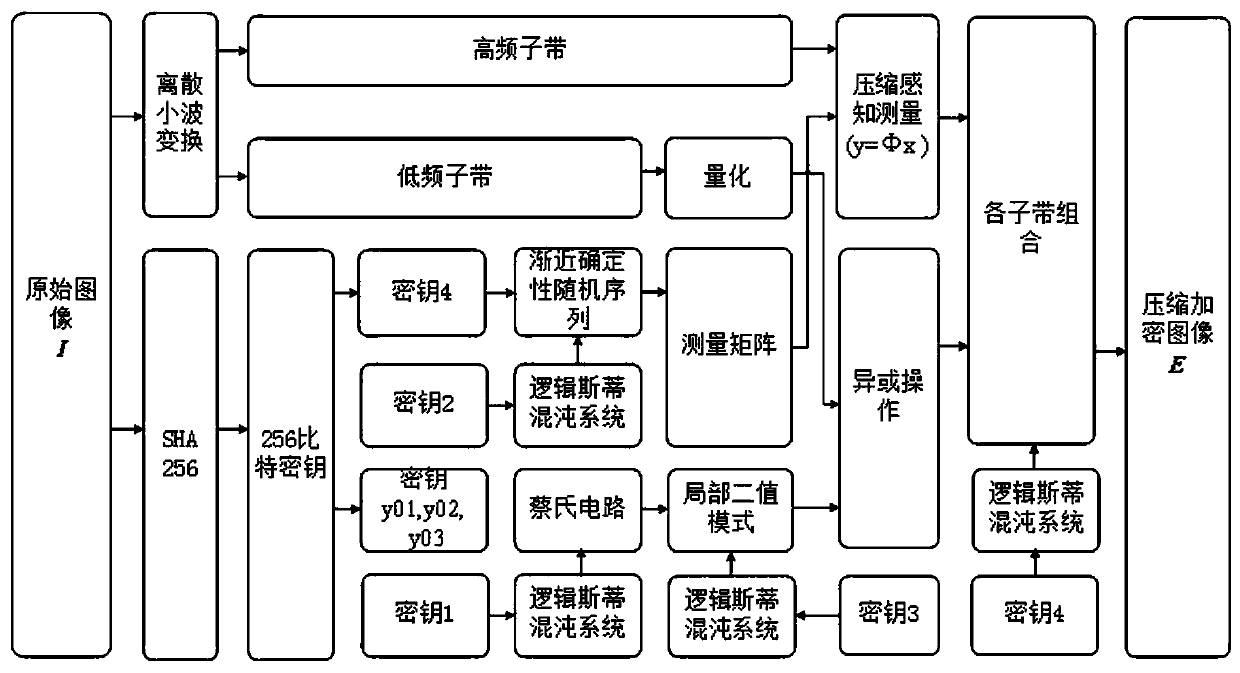

The present invention provides an improved Chua's circuit providing current mode operation, access to all state variables, minimum use of grounded passive elements, and freedom from passive component matching comprising a dual output current conveyer based inductor having one grounded terminal, a capacitor connected across the second terminal of said inductor, a resistor having one terminal connected to the second terminal of said inductor, the second terminal of said resistor connected to one terminal of a second capacitor the other end of which is grounded, and a pair of dual output current conveyers connected together to form a 2-terminal negative resistance having one terminal connected to ground and the second terminal connected to the second terminal of said resistance.

Owner:STMICROELECTRONICS PVT LTD

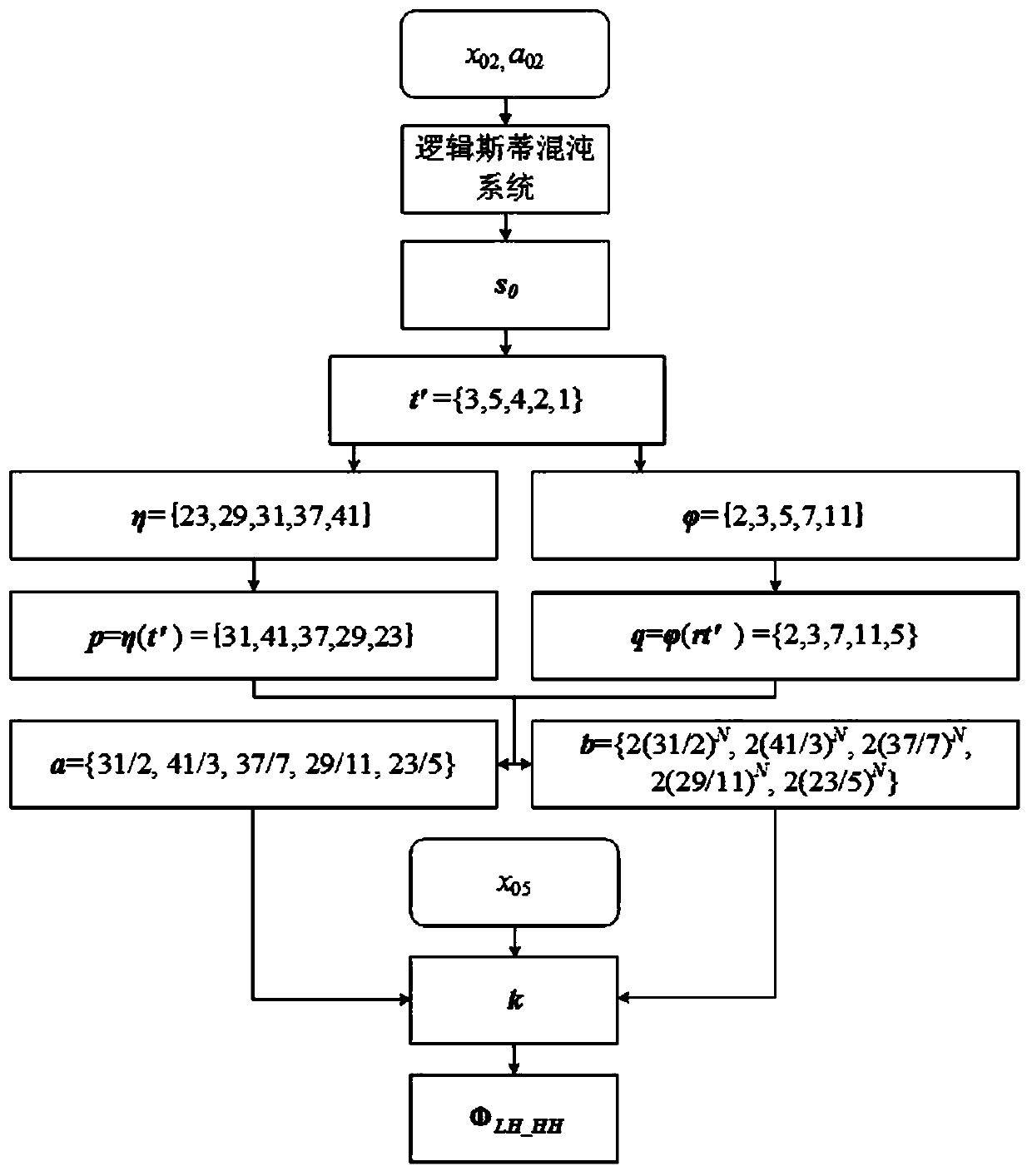

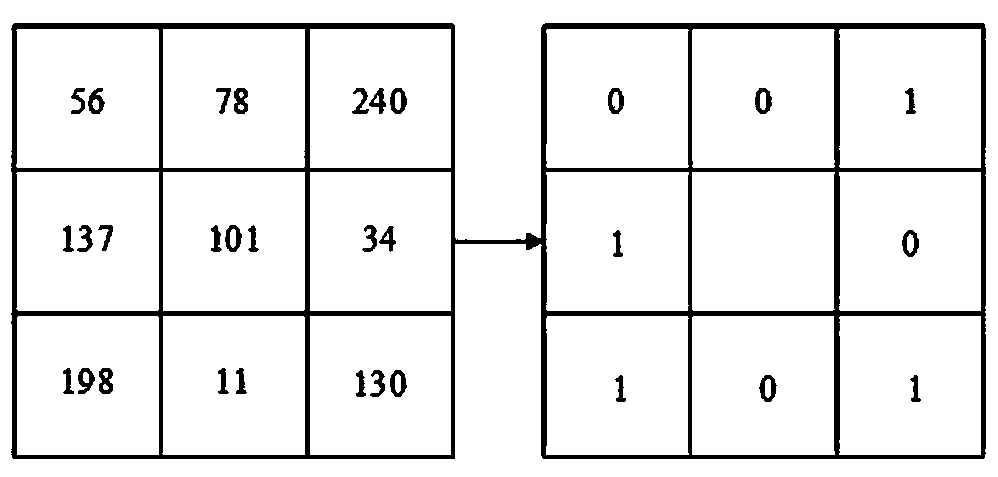

Image compressed encryption method based on compressed sensing and Chua's circuit

InactiveCN108235029AResistance to Differential AttacksRandomDigital video signal modificationPattern recognitionImage compression

The invention discloses an image compressed encryption method based on compressed sensing and a Chua's circuit. The method comprises the following steps of 1, generating a key related to plaintext according to an original image by using SHA-256; 2, performing iteration on initial values x02 and a02 to generate a chaos sequence t' and t'', and generating measurement matrixes FORMULA and FORMULA through performing iteration on t' and t''; 3, measuring sub-bands LH, HH and HL by different compression ratios; 4, quantizing to acquire an integer sequence z, and forming a matrix z'; 5, acquiring a diffusion matrix f'; 6, acquiring a matrix LL', and performing an XOR operation on the diffusion matrix f'; and 7, combining four sub-bands such as LL, LH, HL and HH, and scrambling the chaos sequencegenerated by x04 and a04 to acquire a final compressed encryption image E. According to the method the data transmission quantity can be reduced, the robustness of the image can also be enhanced, thesecurity is high, and particularly, the method is good in performance when being used for resisting shearing attacks and noise attacks.

Owner:GUANGXI NORMAL UNIV

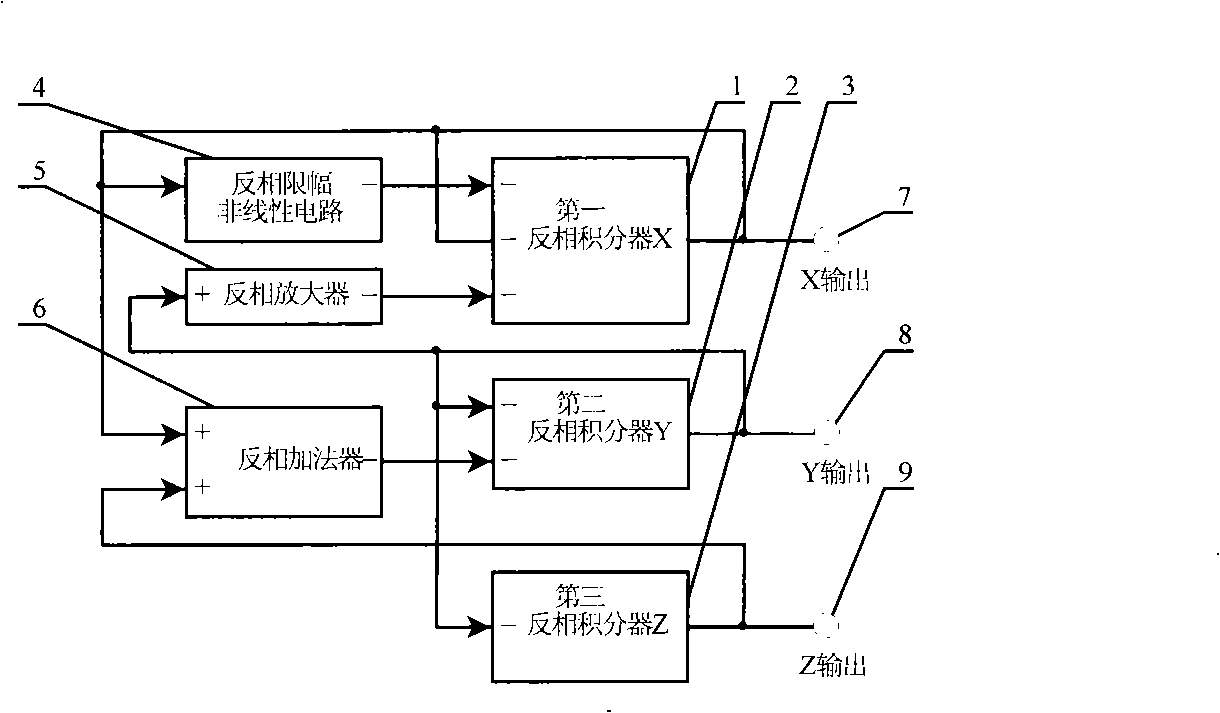

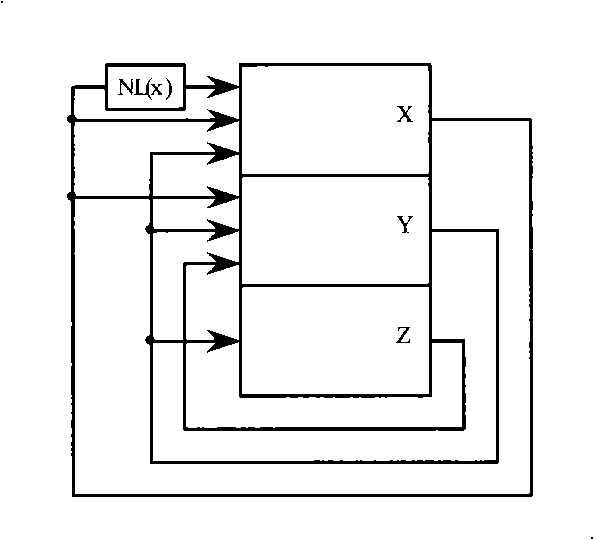

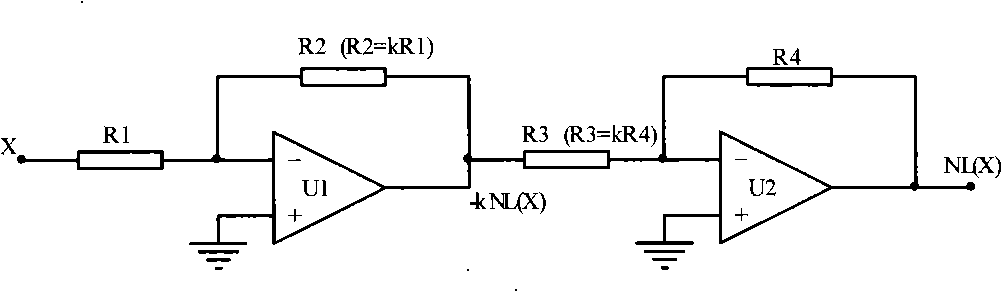

Non-inductor Chua's circuit

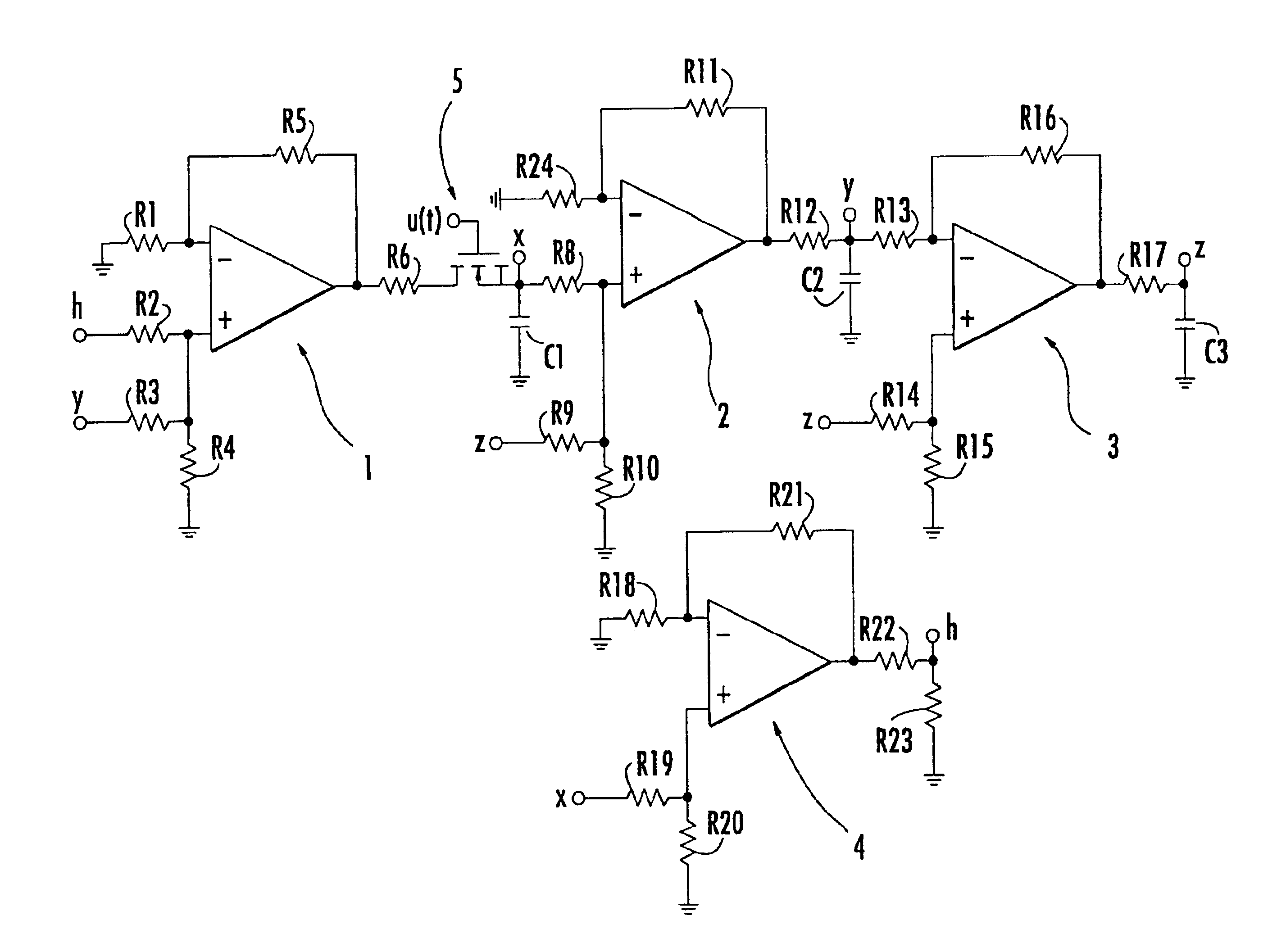

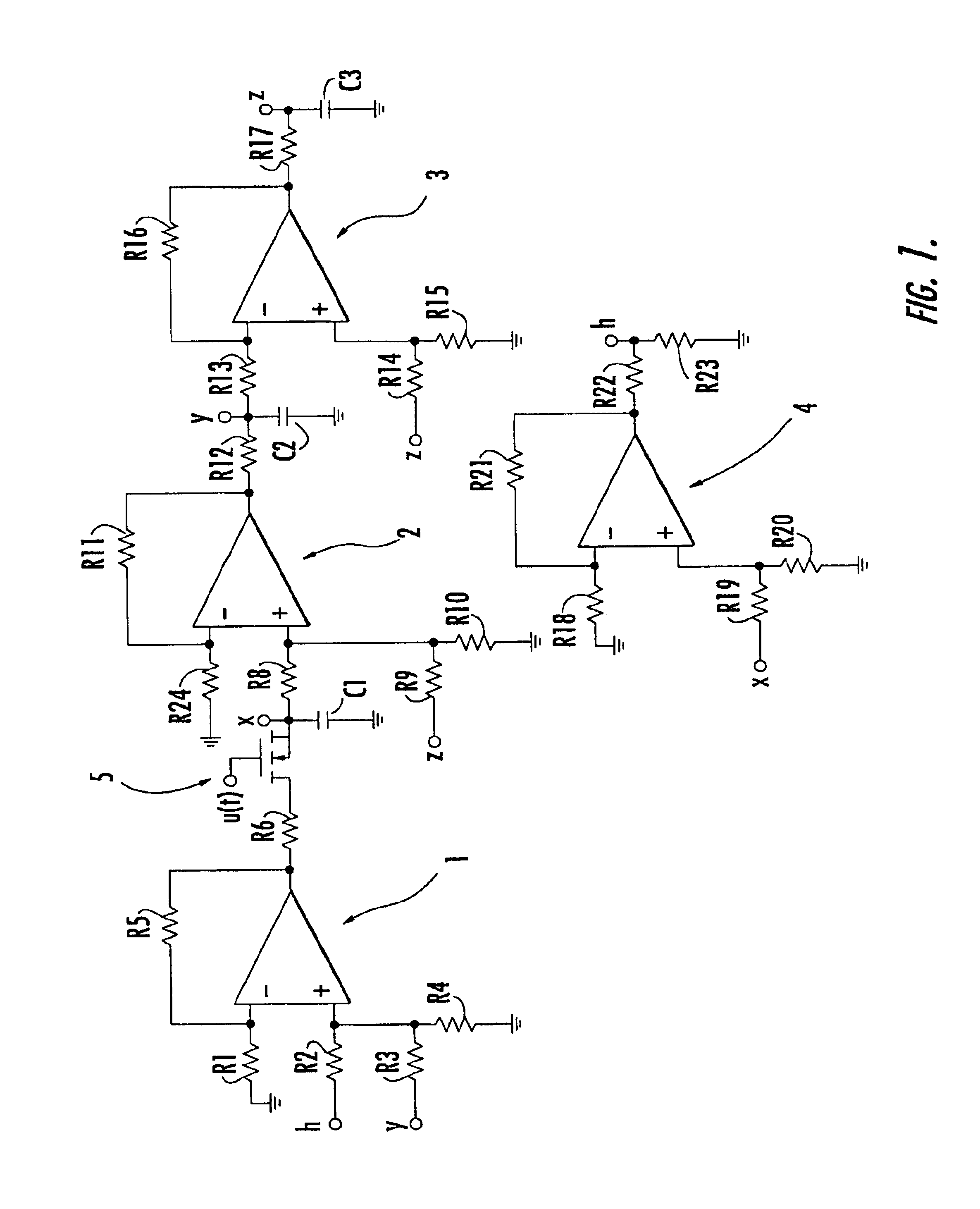

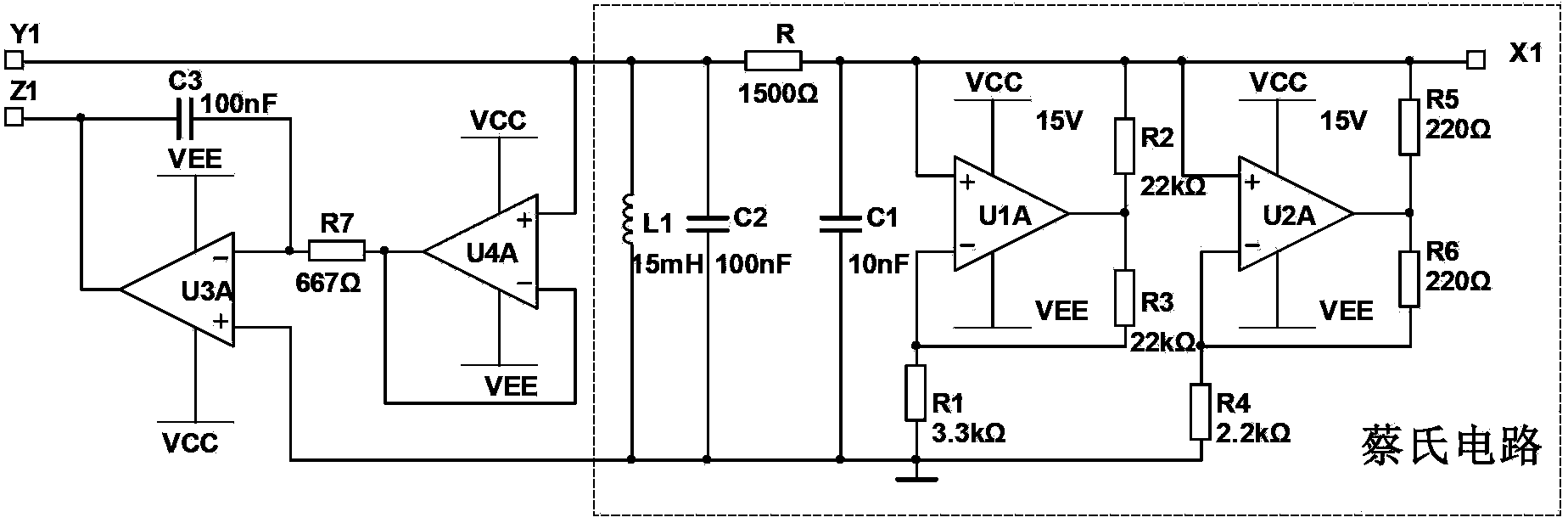

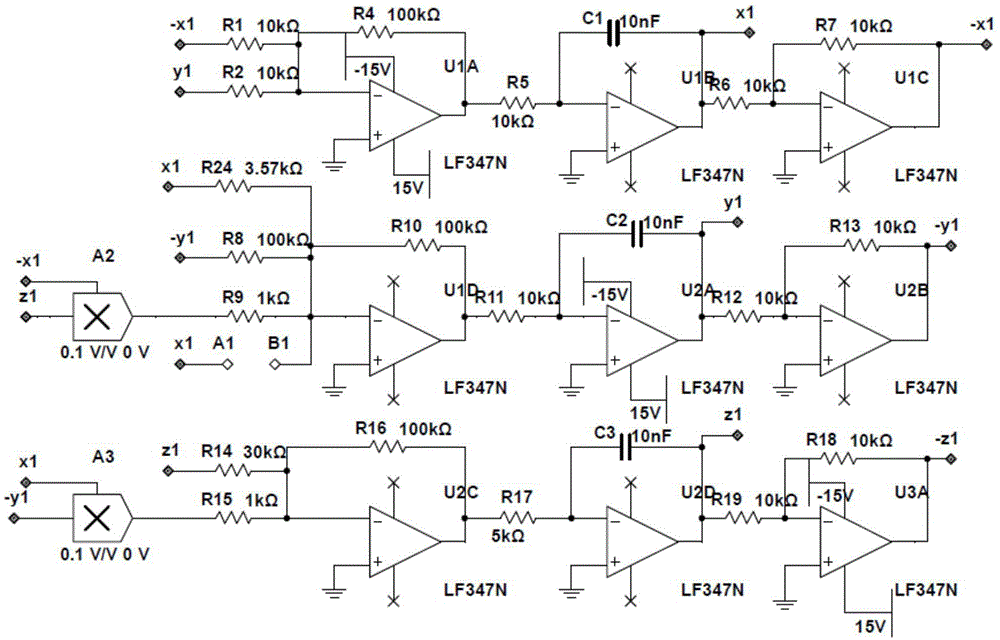

The invention discloses a noninductive Cai's circuit, comprising three anti-phase integrators, an anti-phase limiting nonlinear circuit, an anti-phase amplifier and an anti-phase adder. An output terminal X of a first anti-phase integrator is respectively connected with one input terminal itself, an input terminal of the anti-phase limiting nonlinear circuit and an input terminal of the anti-phase adder; an output terminal Y of a second anti-phase integrator is respectively connected with one input terminal itself, an input terminal of a third anti-phase integrator and the input terminal of the anti-phase amplifier; an output terminal Z of a third anti-phase integrator is connected with one input terminal of the anti-phase adder, and the output terminal of the anti-phase limiting nonlinear circuit is connected with one input terminal of the first anti-phase integrator, and the output terminal of the anti-phase amplifier is connected with one input terminal of the first anti-phase integrator, and the output terminal of the anti-phase adder is connected with one input terminal of the second anti-phase integrator. The noninductive Cai's circuit has simple structure, high accuracy and better stability, and can provide waveforms corresponding to each algebraic item of the mathematic expression of the Cai's circuit.

Owner:STATE GRID CORP OF CHINA +2

Chua's circuit and it's use in a hyperchaotic circuit

ActiveUS20050242906A1Minimal useNegative-feedback-circuit arrangementsNetwork simulating negative resistancesState variableEngineering

The present invention provides an improved Chua's circuit providing current mode operation, access to all state variables, minimum use of grounded passive elements, and freedom from passive component matching comprising a dual output current conveyer based inductor having one grounded terminal, a capacitor connected across the second terminal of said inductor, a resistor having one terminal connected to the second terminal of said inductor, the second terminal of said resistor connected to one terminal of a second capacitor the other end of which is grounded, and a pair of dual output current conveyers connected together to form a 2-terminal negative resistance having one terminal connected to ground and the second terminal connected to the second terminal of said resistance.

Owner:STMICROELECTRONICS PVT LTD

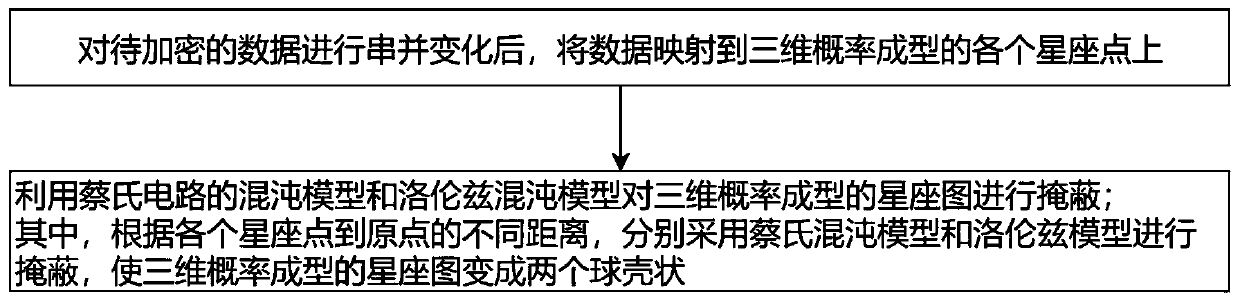

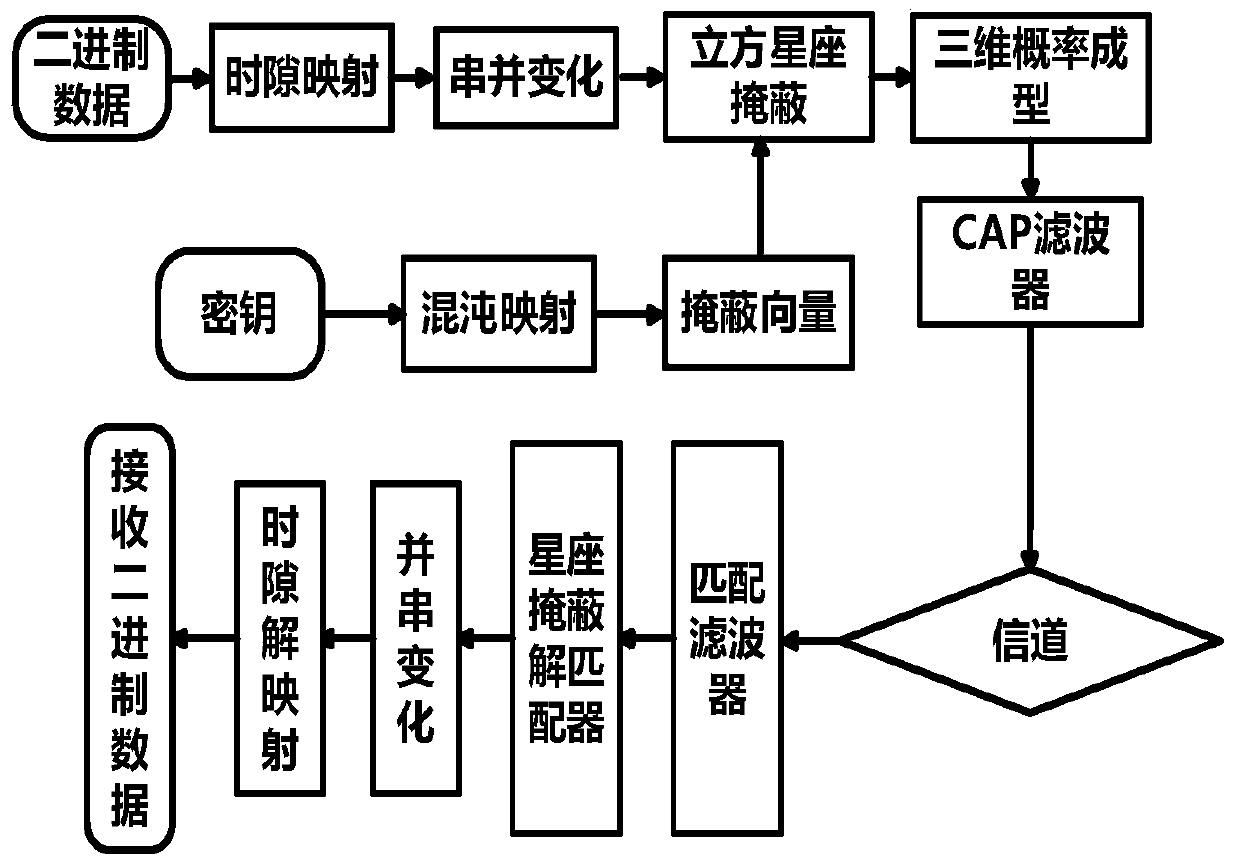

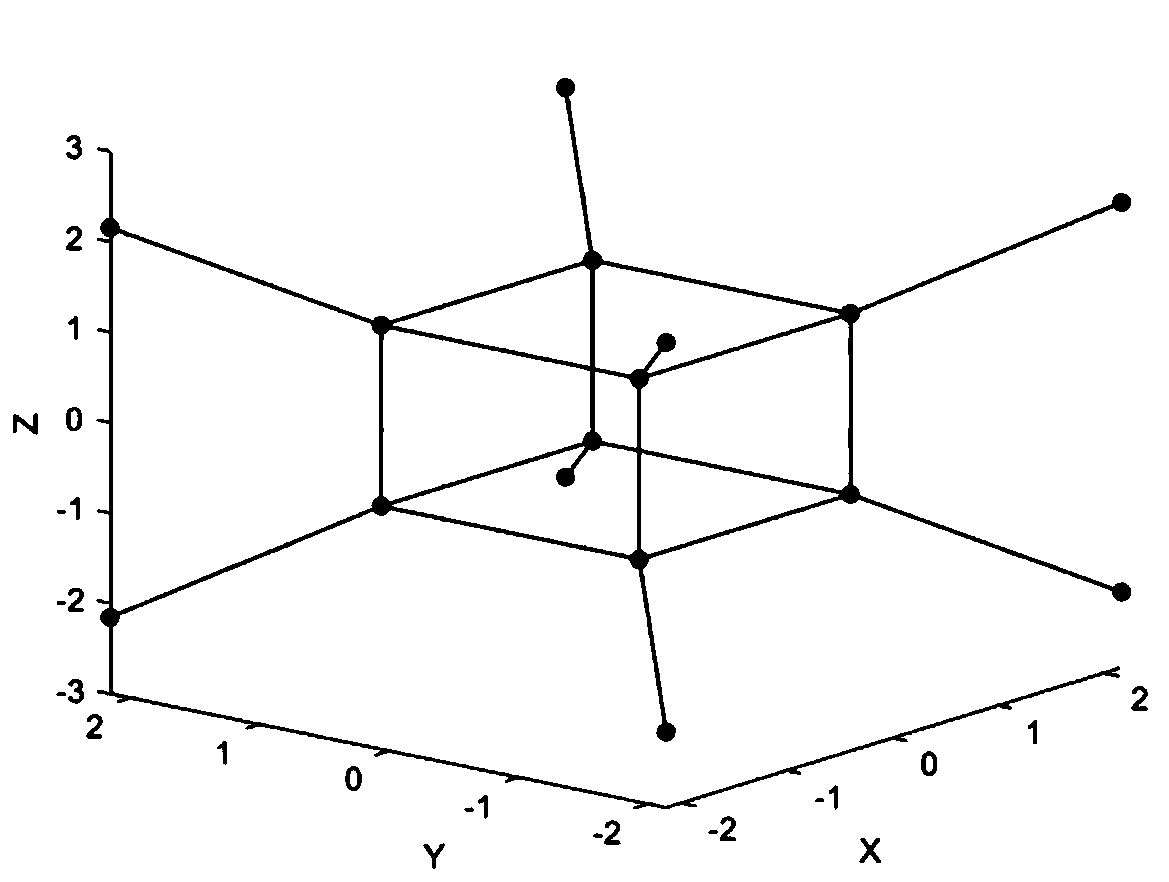

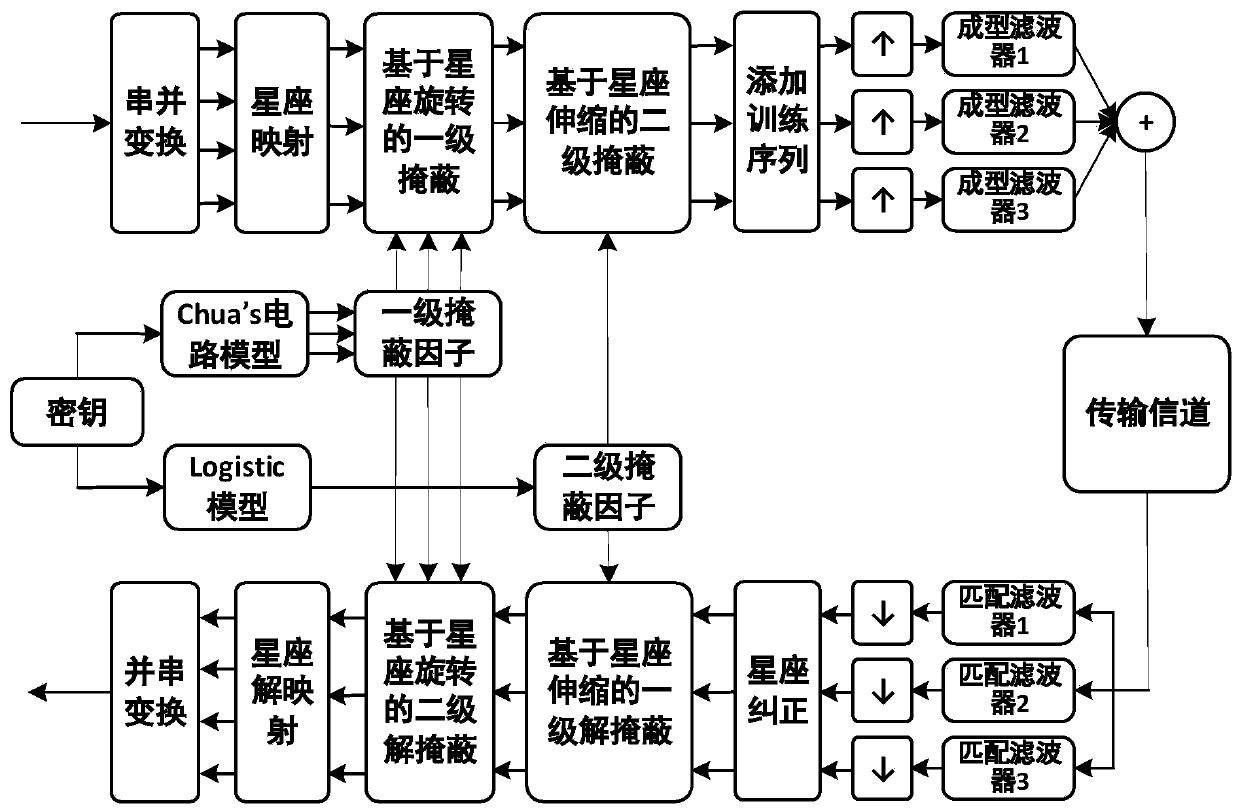

Chaotic encryption method and system based on three-dimensional probability forming

ActiveCN111245596ASuitable for transmissionReduce transmit powerFibre transmissionSecuring communication by chaotic signalsKey spaceAlgorithm

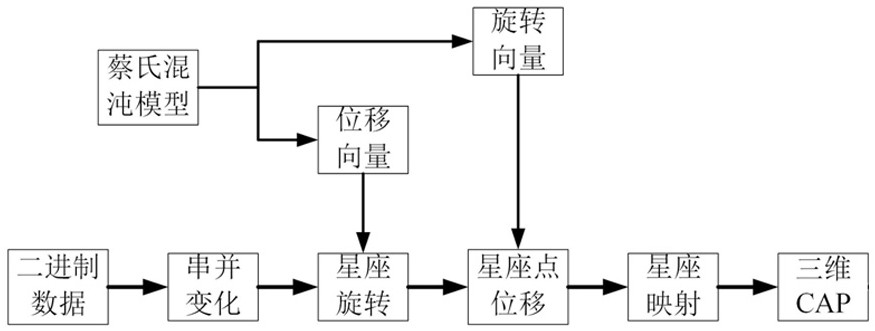

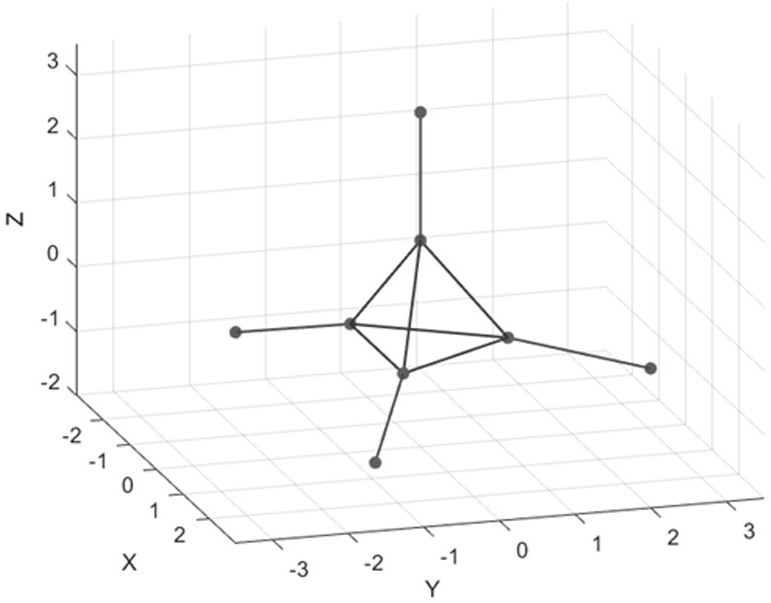

The invention discloses a chaotic encryption method based on three-dimensional probability forming, which comprises the following steps: after carrying out serial-parallel change on to-be-encrypted data, mapping the data to each constellation point of three-dimensional probability forming; and masking the constellation diagram of three-dimensional probability forming by utilizing a chaotic model of the Chua's circuit and a Lorentz chaotic model, wherein the Chua's chaotic model and the Lorentz model are respectively adopted for masking according to different distances from each constellation point to an original point, so that the constellation diagram of three-dimensional probability forming is changed into two spherical shells. According to the invention, after spherical three-dimensional probability forming, the transmitting power of the whole system can be greatly reduced, and a new carrier after probability forming has Gaussian energy distribution and is more suitable for transmission of an optical signal in an optical fiber channel; and the Chua's circuit model and the Lorentz model are used for chaotic mapping, compared with a traditional masking mode, the encryption effectis good, and larger key space and higher flexibility are provided.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

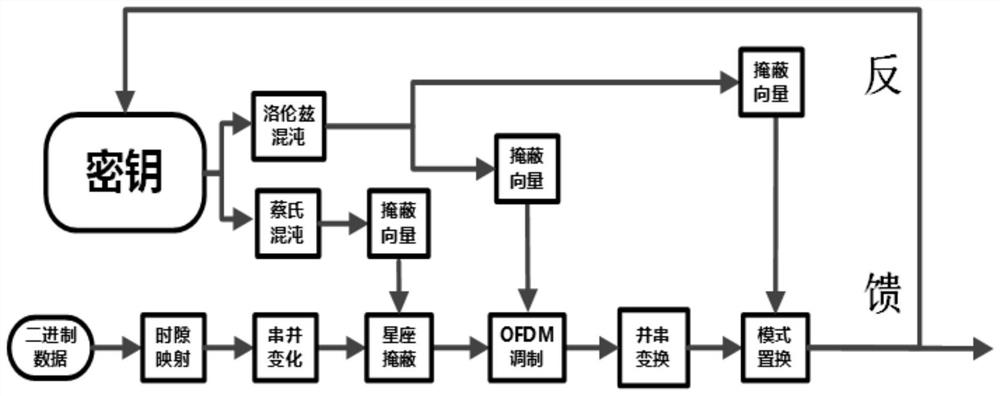

Security-level-controllable carrier, constellation and mode multi-chaos masking light transmission method

ActiveCN112054888ASecret level controllableLarge key spaceFree-space transmissionSecuring communication by chaotic signalsAlgorithmTheoretical computer science

The invention provides a security-level-controllable carrier, constellation and mode multi-chaos masking light transmission method, which comprises the following steps of: performing serial-parallel change on data, and mapping the data to each constellation point; masking the three-dimensional constellation diagram by using a Chua's chaotic model, so that the three-dimensional constellation pointsare converted into a sphere; then, the Lorentz model being used for masking the subcarrier and the orthogonal mode, meanwhile, parameters of the Lorentz model and the Chua's circuit model being modulated, and therefore security level controllability of chaotic encryption being achieved. At the receiving end, an original Chua's circuit and an original Lorentz model secret key are used for decrypting the chaotic constellation diagram. The signals decrpted by the receiving end are compared with the transmitting end, thus to calculate the system error ratio, thereby judging the system performance. By the control over the parameters a chaos model, encryption of one dimension or multiple dimensions can be conducted, thus security classification can be achieved. According to different conditions, high-security transmission is realized at the lowest encryption cost.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

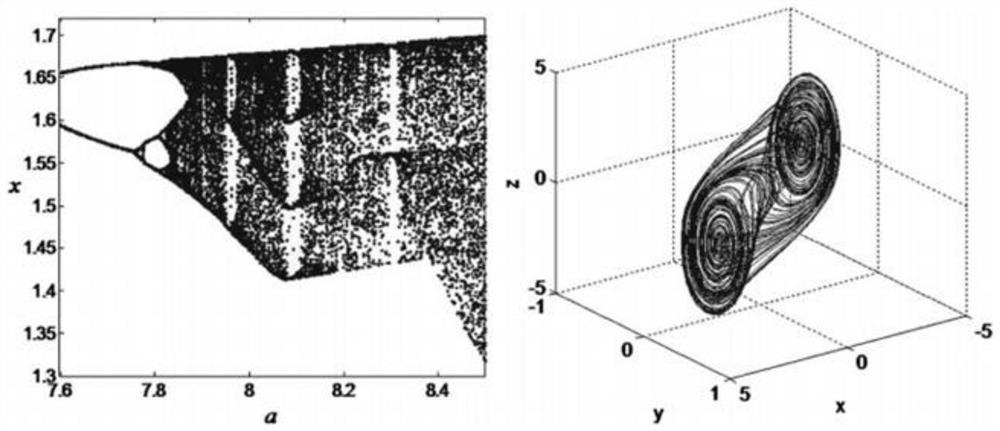

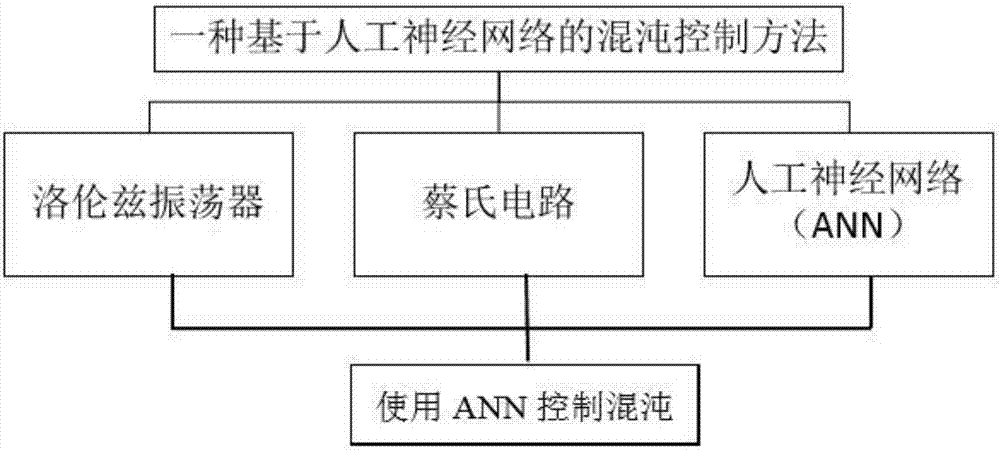

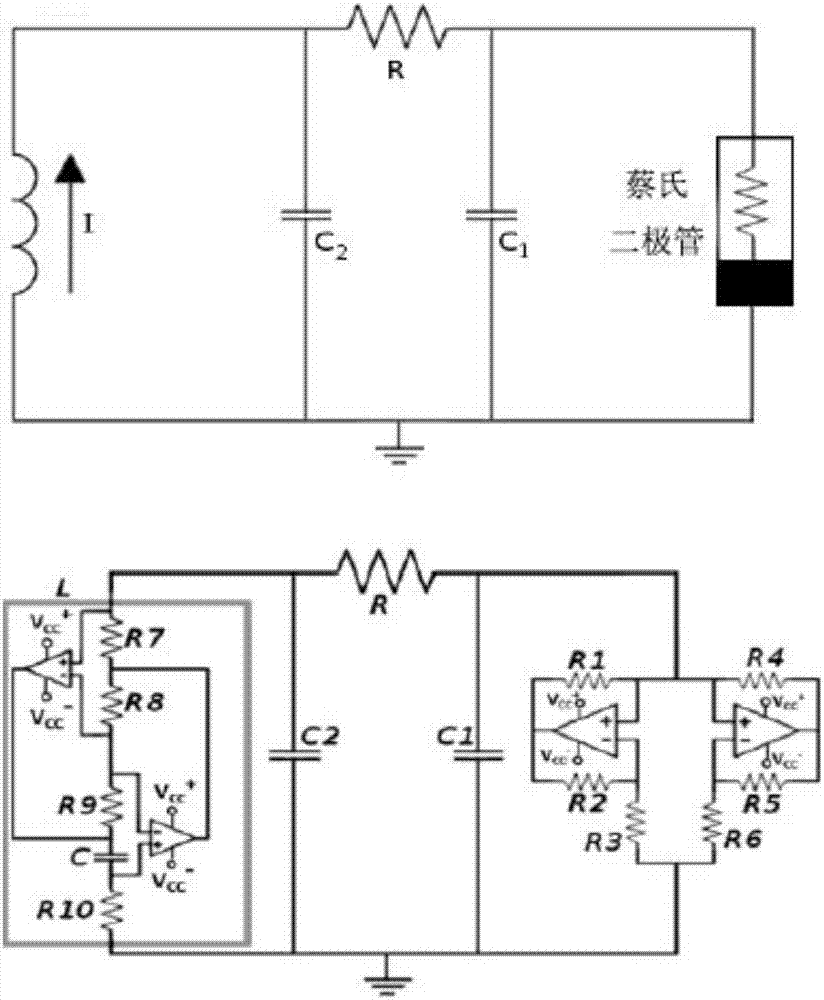

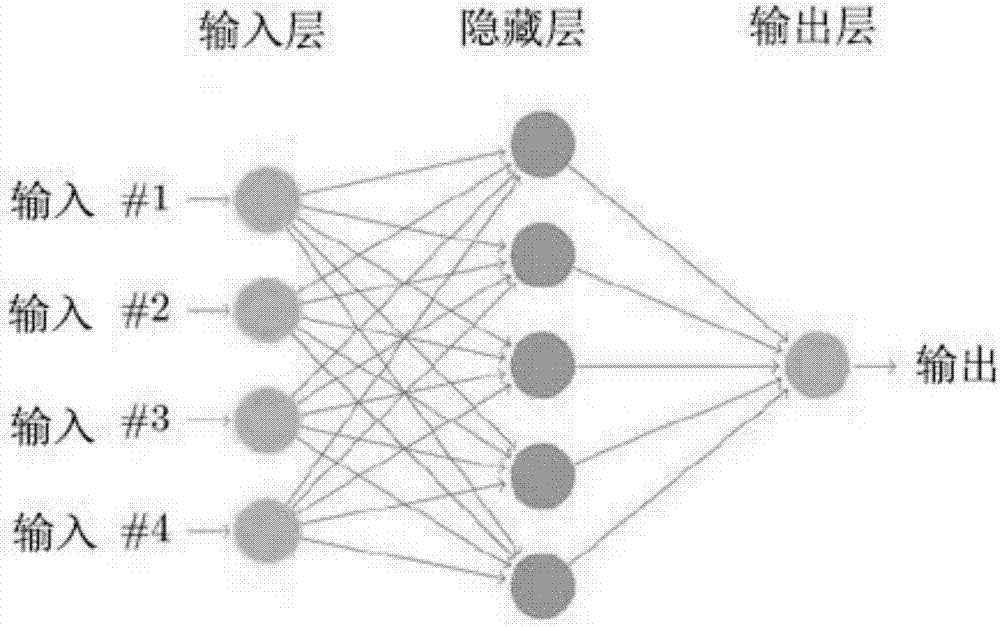

Chaotic control method based on artificial neural network

InactiveCN106875009ADesign optimisation/simulationCAD circuit designControl engineeringChaotic systems

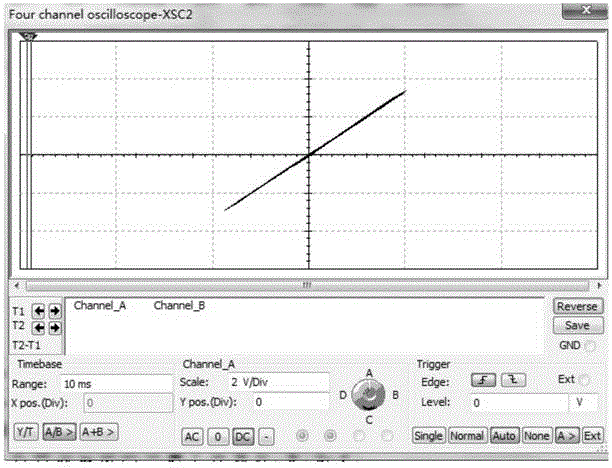

The invention provides a chaotic control method based on an artificial neural network. A Lorentz oscillator, a Chua circuit and the artificial neural network (ANN) are mainly included. The ANN is used to control chaos. A process is characterized in that the Chua circuit is constructed on a panel; output displayed on an oscilloscope is tested and acquired; a simulation analysis program is used to redraw an electronic circuit of each component of the ANN; output of an ANN circuit is connected to the Chua circuit, and one part of circuit output is fed back to the ANN; a weight is correspondingly adjusted; and through learning, the ANN adjusts a parameter of the Chua circuit and gives out required output. In the invention, the ANN is used to effectively control a chaotic system, the required output is acquired from the chaotic system, control stability is provided and automation is realized; the chaotic system is controlled so that functions in other applications can be realized.

Owner:SHENZHEN WEITESHI TECH

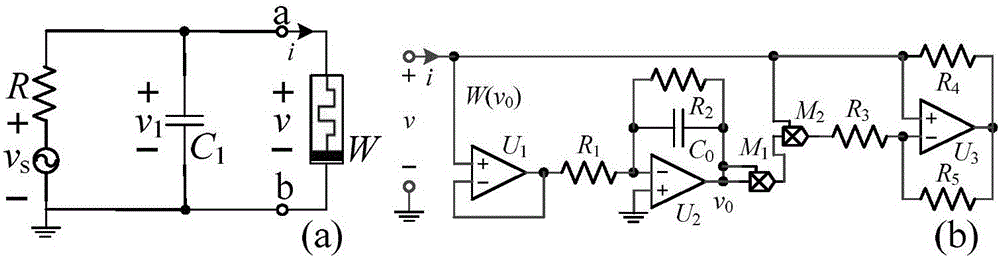

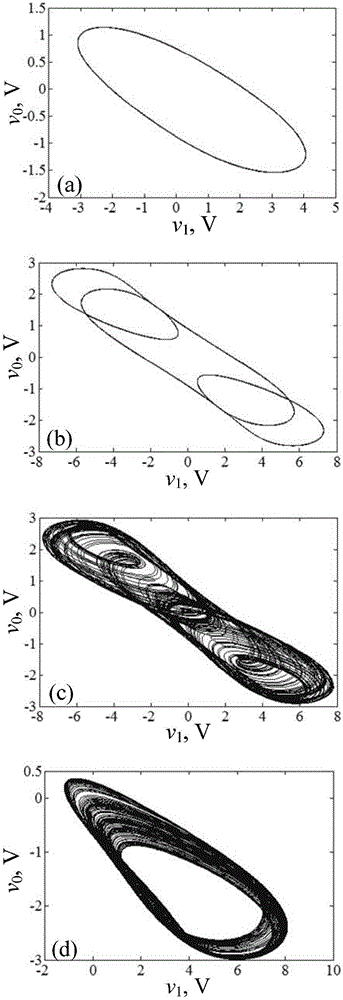

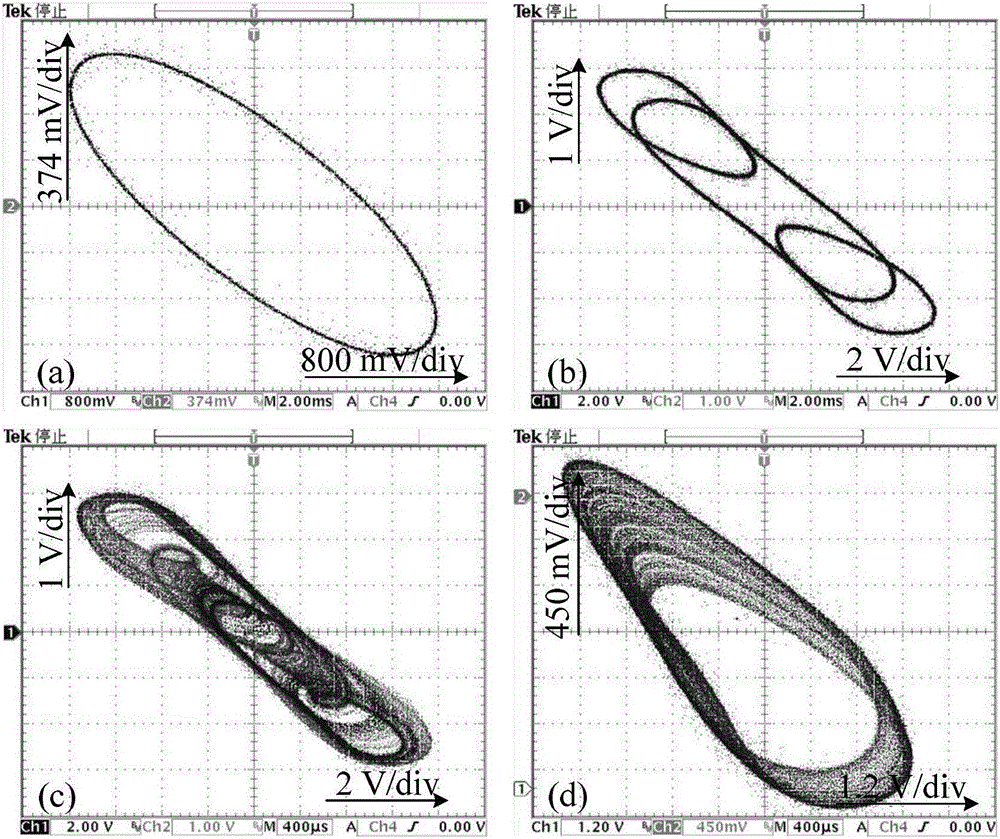

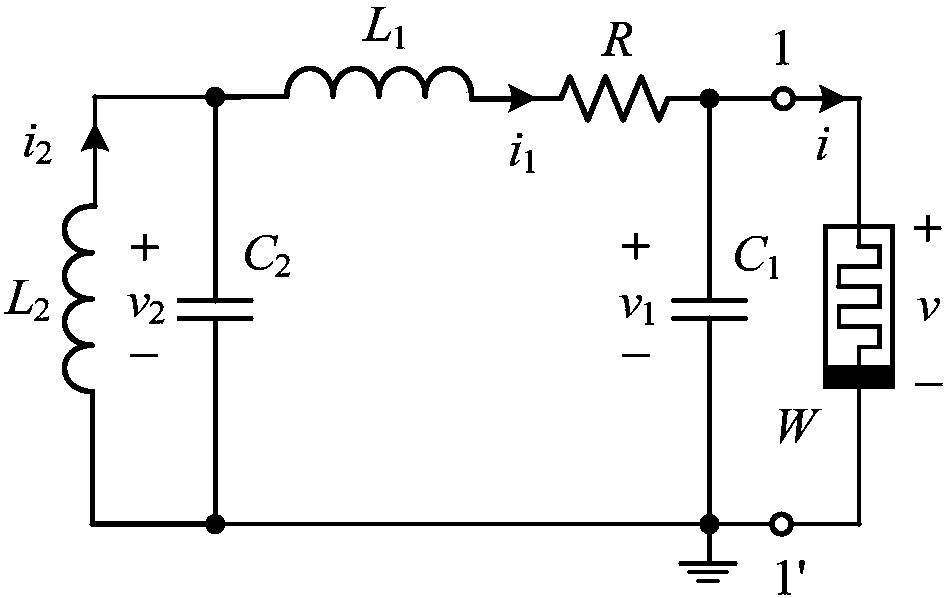

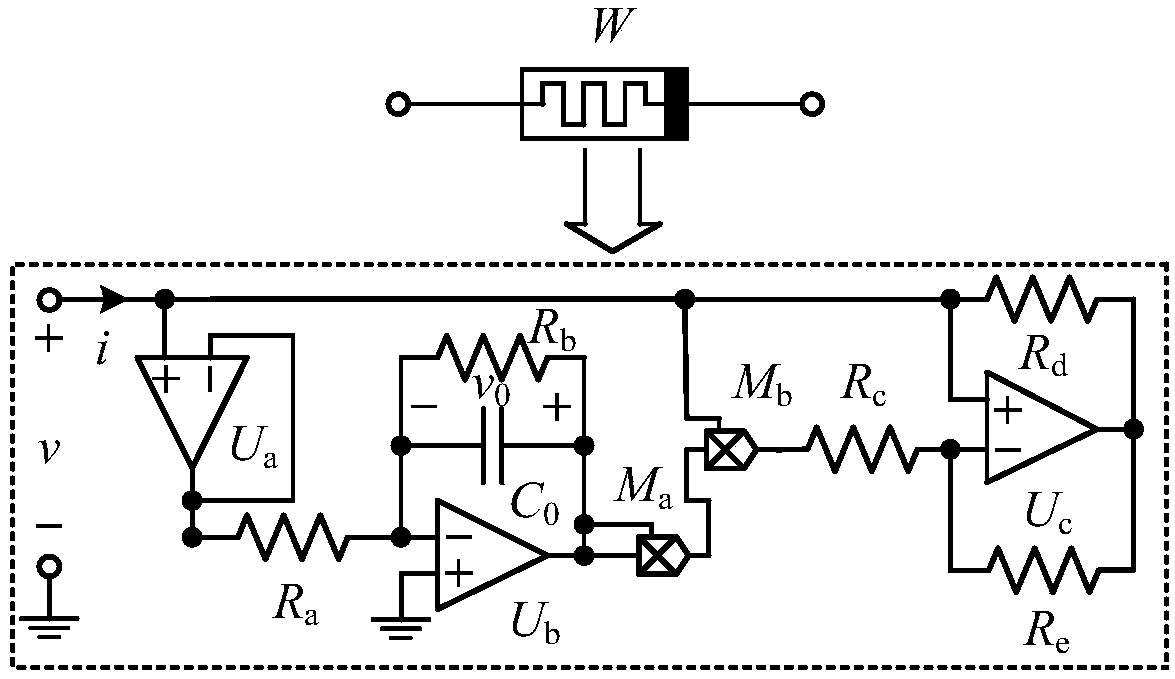

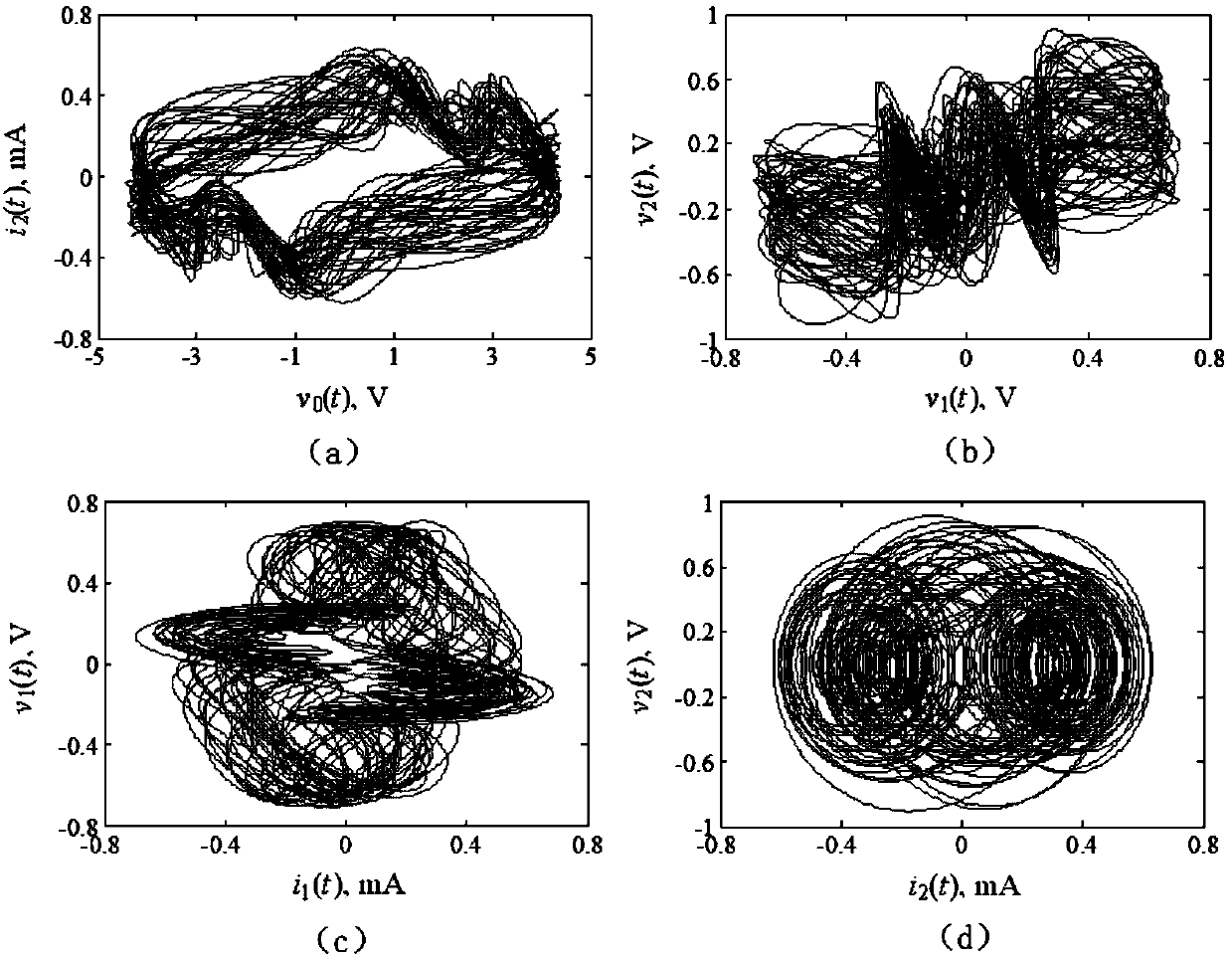

Simple second order non-autonomous memristor chaotic signal generator

InactiveCN106209345AImprove stabilitySignificant chaotic propertiesSecuring communication by chaotic signalsNonlinear phenomenaEngineering

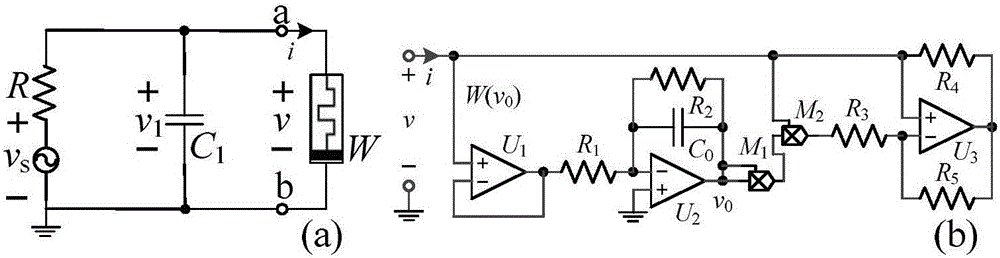

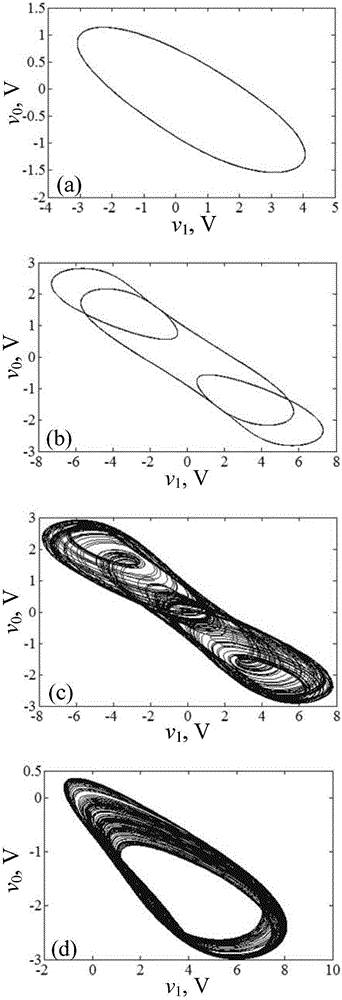

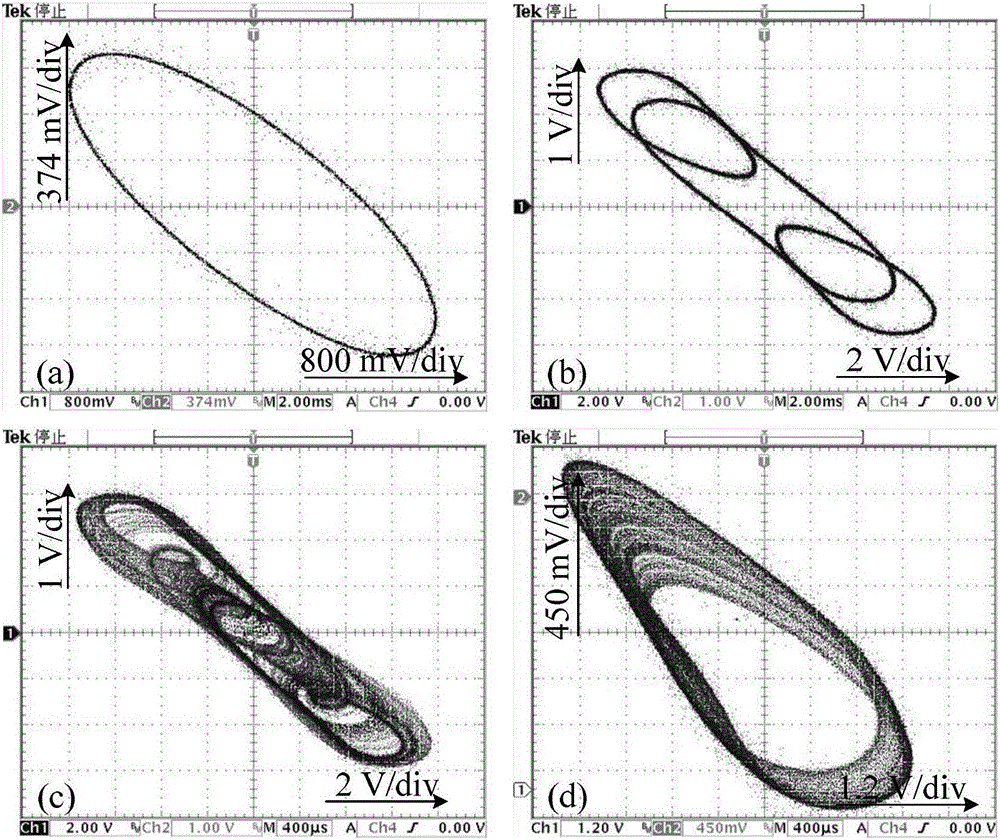

The invention discloses a simple second order non-autonomous memristor chaotic signal generator, consisting of a memristor driven by a standard sinusoidal voltage signal and a capacitor parallel circuit. The circuit only comprises two dynamic elements, namely a capacitor C1 and a memristor W. The essence of the simple second order non-autonomous memristor chaotic signal generator disclosed by the invention is to replace a passive LC oscillator in a memristor Chua's circuit by using the standard sinusoidal voltage signal to constitute a simple and novel chaotic signal generator, and a chaotic attractor, a periodic limit cycle and other complex phenomena can be generated by adjusting the parameters of the circuit. The circuit is simple in structure, strong in stability and significant in chaotic properties, and plays a relatively large promotion function to the application development of the memristor circuit.

Owner:CHANGZHOU UNIV

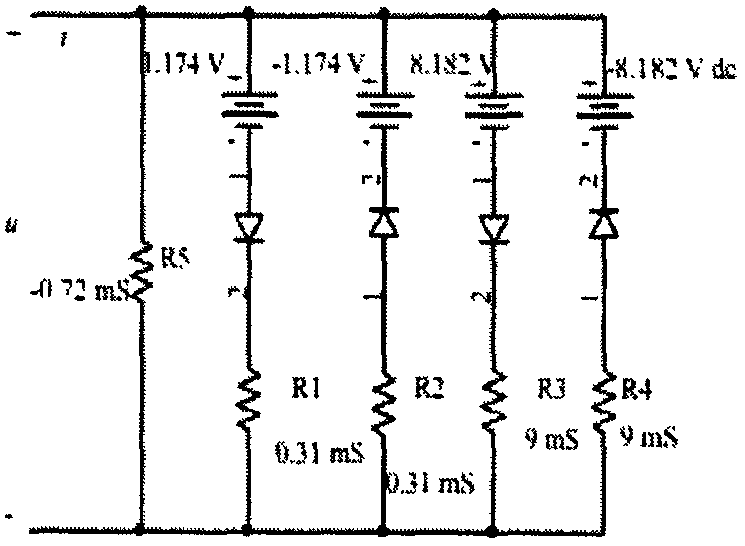

Negative resistance equivalence method for Chua's chaotic circuits

InactiveCN103236918ARealize the equivalent method of negative resistanceReduce voltageSecuring communicationSingle electronEngineering

The invention relates to a negative resistance equivalence method for Chua's chaotic circuits. The method includes: utilizing negative differential resistance (NDR) characteristics of a hybrid structure device (SETMOS (single electron transistor metal oxide semiconductor)) of an SET and an MOS to realize a nonlinear function of a chaotic circuit, and applying the nonlinear function to a Chua's circuit to replace negative resistance. Stimulation of the circuit shows that the method is effective, the circuit is easy to realize, output signals have wide dynamic range, and the method is expected to have wide application prospect and important application value in fields of radar, secret communication, electronic countermeasure and the like.

Owner:王少夫

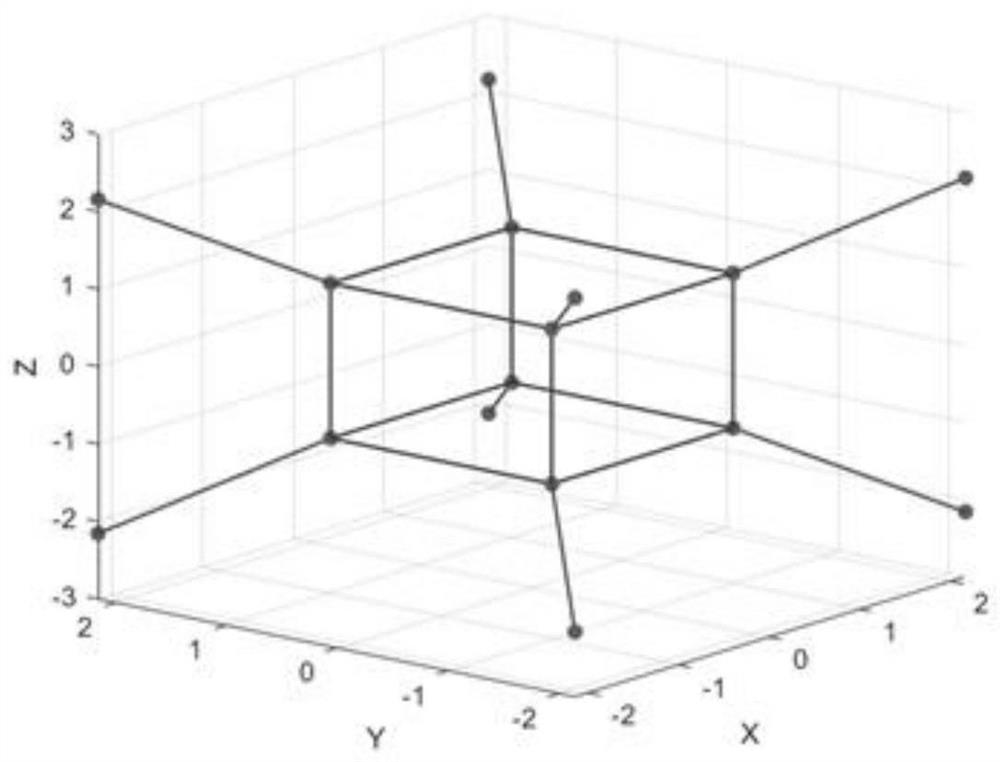

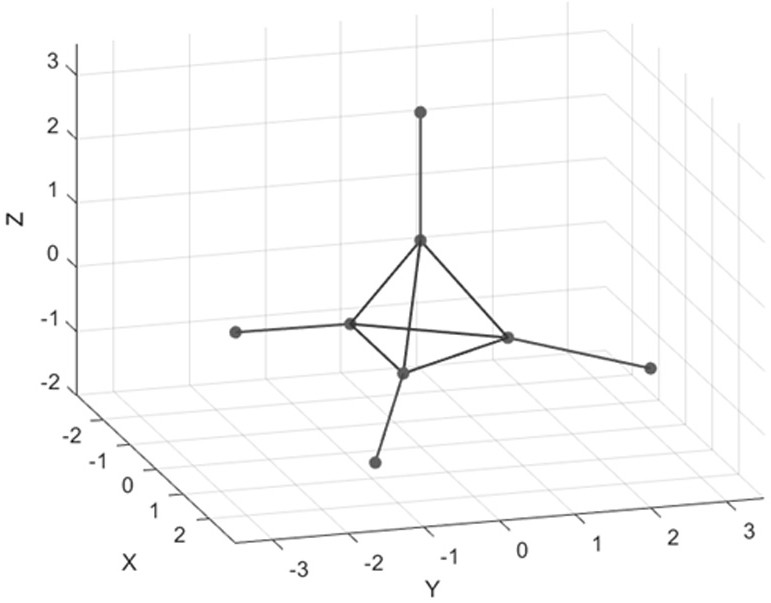

Safety light access method based on two-stage spherical constellation masking

ActiveCN111417038AImplement rotation encryptionImplement scalable encryptionMultiplex system selection arrangementsSecuring communication by chaotic signalsAlgorithmThree-dimensional space

The invention relates to a safety light access method based on two-stage spherical constellation masking, which comprises the following steps: taking a Chua's circuit model as a first chaotic model for generating a first-stage masking factor based on constellation rotation; taking the Logistic model as a second chaotic model for generating a secondary masking factor based on constellation scaling;applying the two levels of masking factors to three-dimensional CAP encryption modulation; three-dimensional CAP decryption demodulation. According to the method disclosed in the invention, the two chaotic models are combined to respectively realize multi-chaotic combined encryption on constellation rotation and amplitude transformation, and therefore the safety performance of the optical accesssystem can be more effectively improved. Meanwhile, constellation masking is three-dimensional constellation encryption in a three-dimensional space; compared with a two-dimensional constellation, three-dimensional constellation is advantageous in that dimension improvement enables encryption transformation to be more flexible, the safety performance of a physical layer after constellation encryption is greatly improved, the Euclidean distance between three-dimensional constellation points is larger, and the bit error rate performance of the system is improved.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

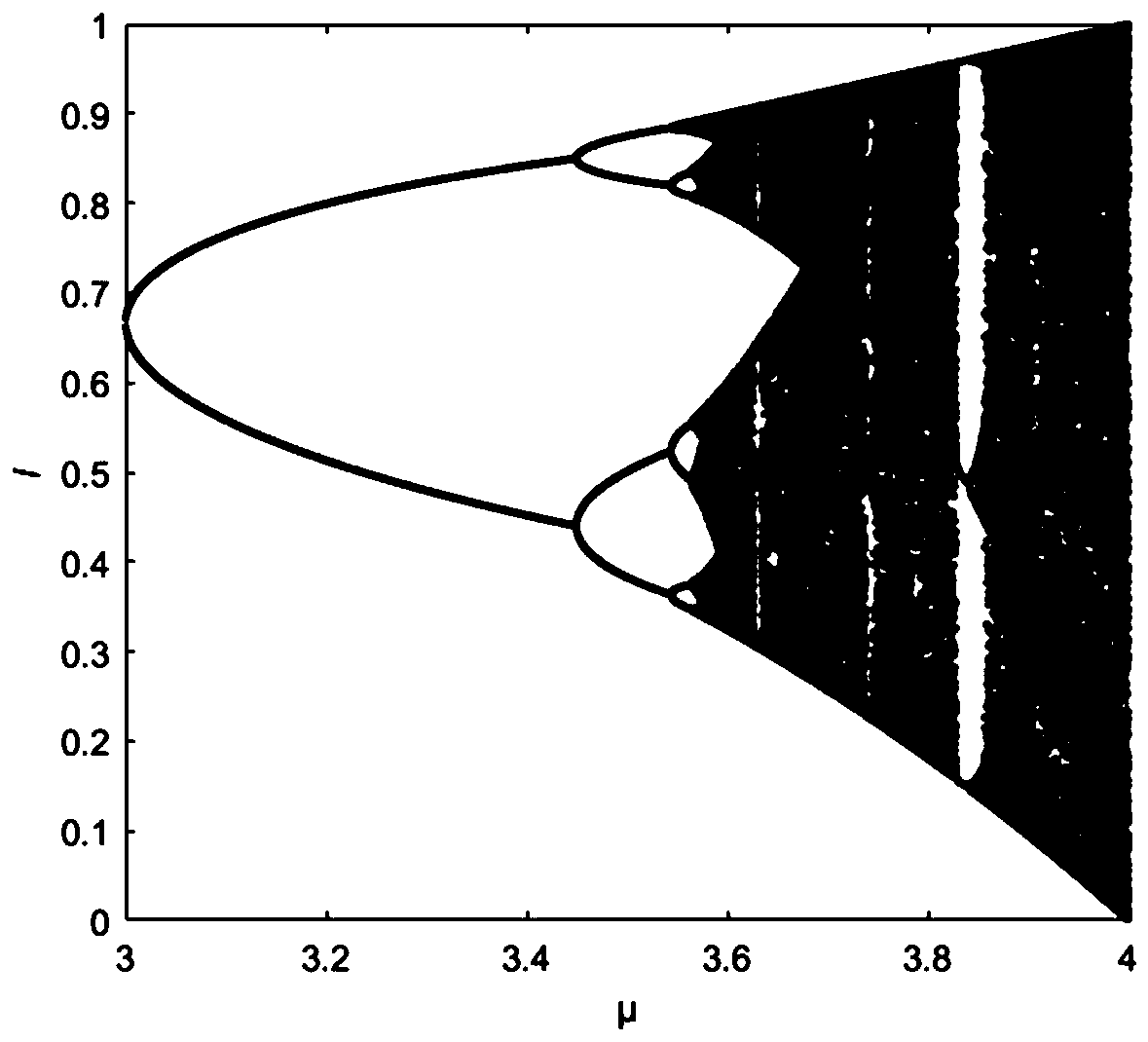

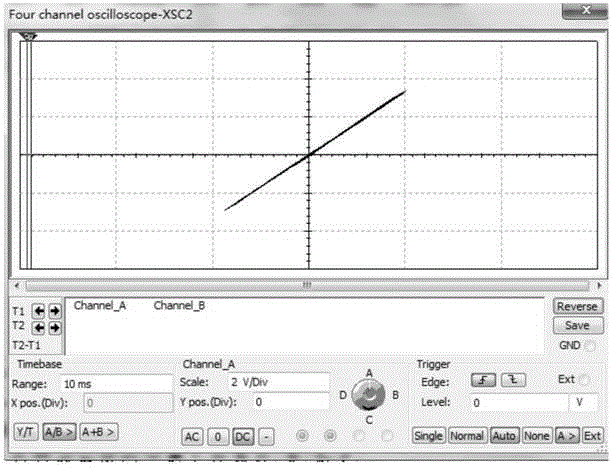

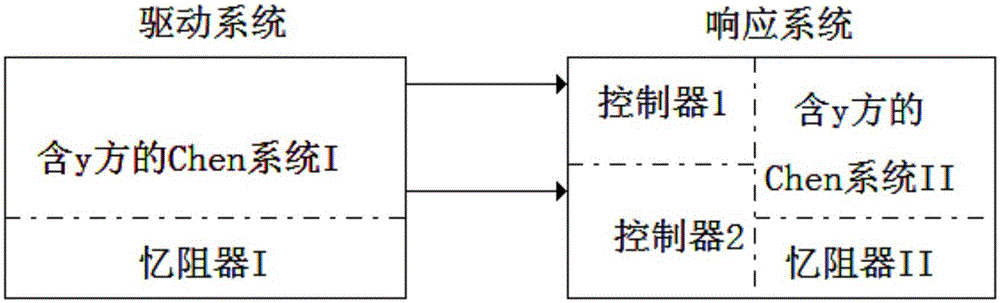

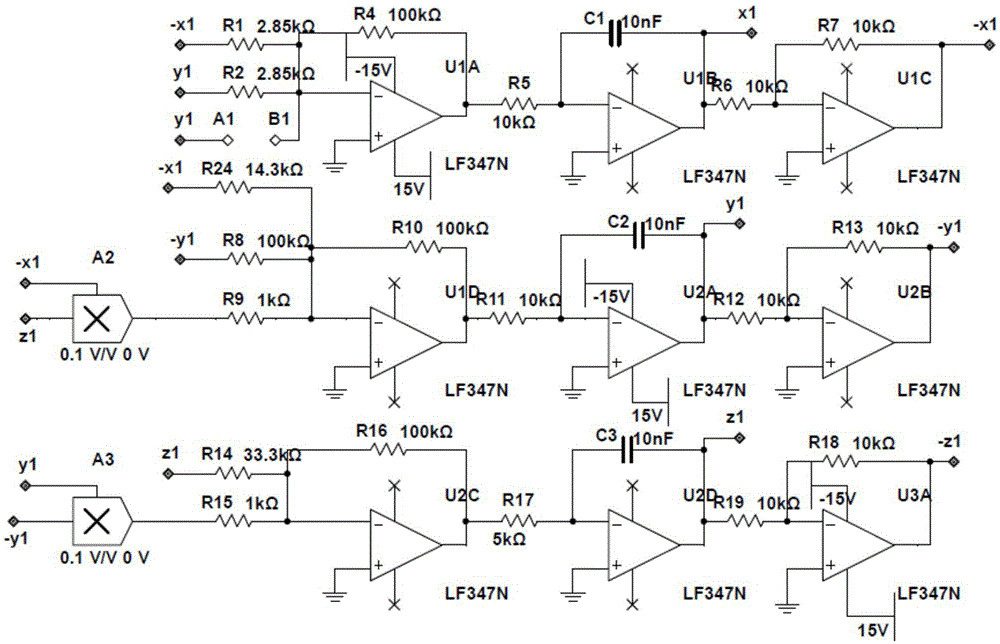

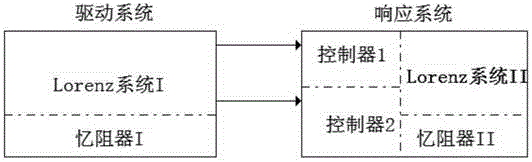

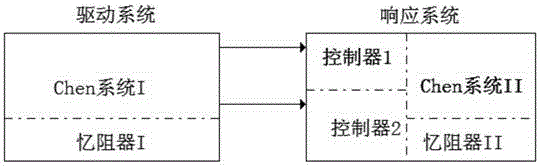

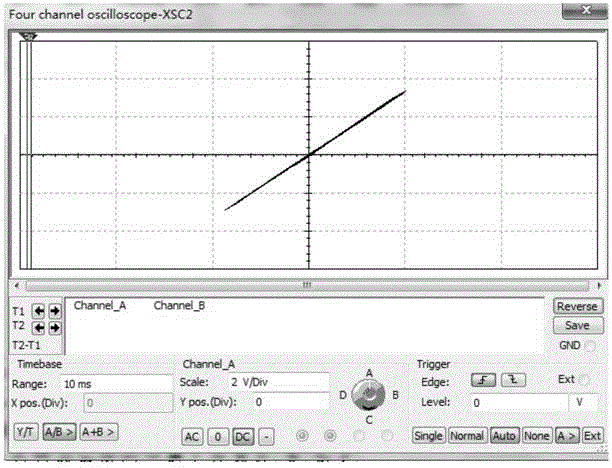

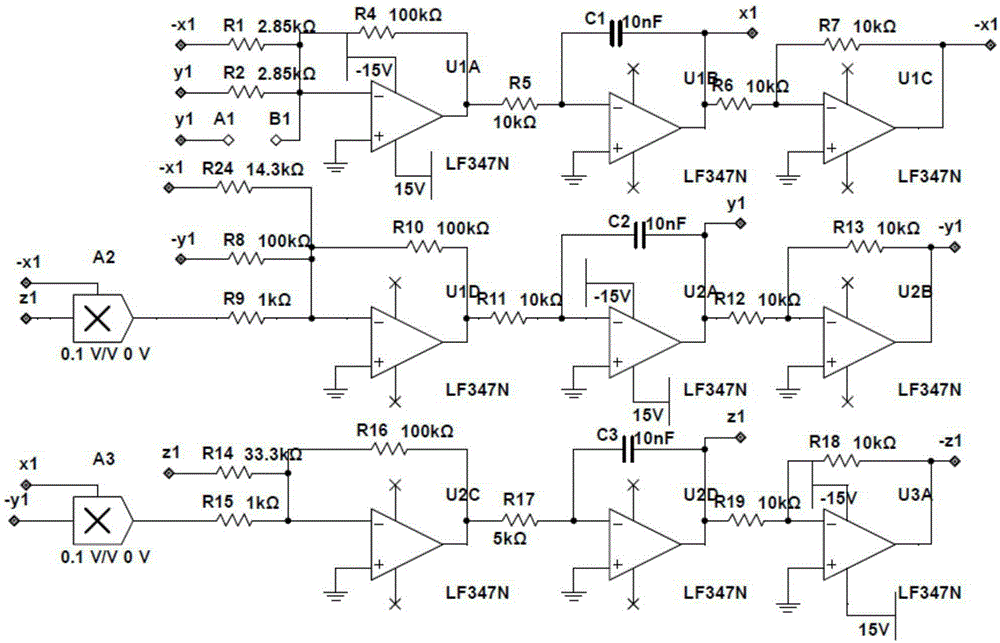

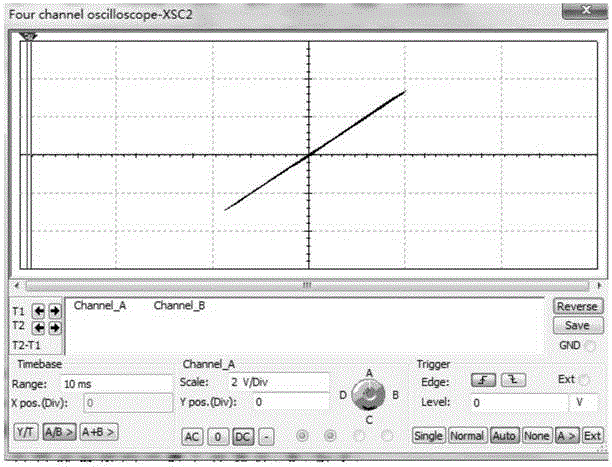

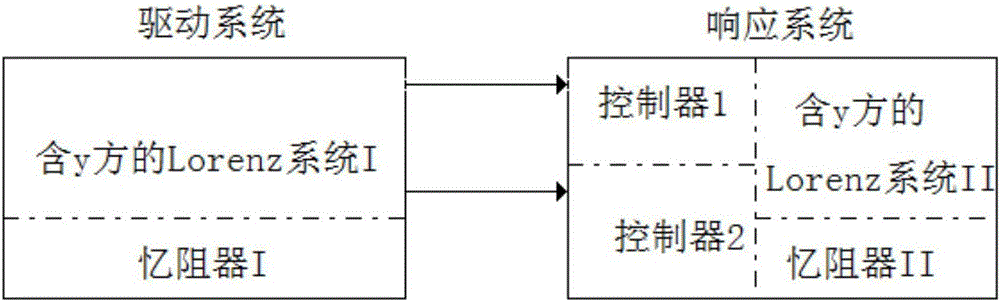

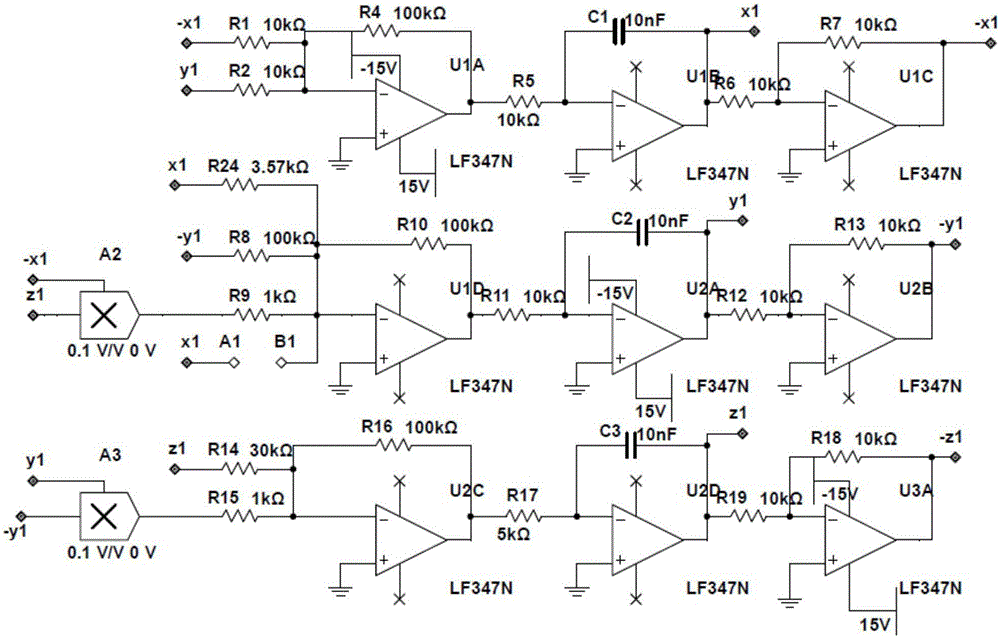

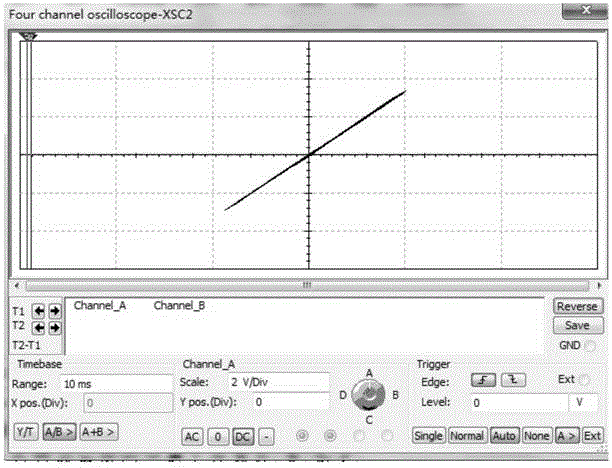

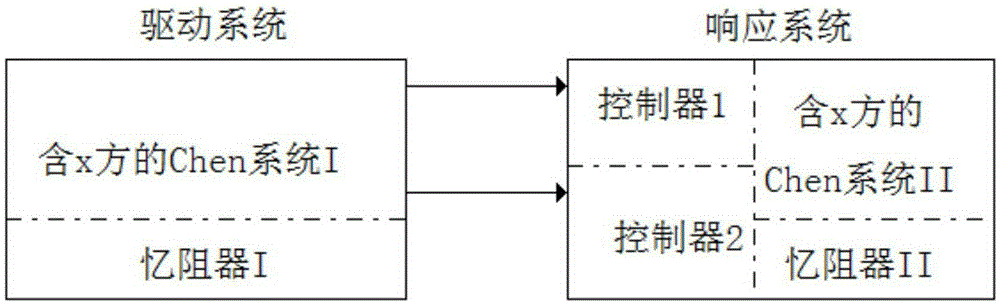

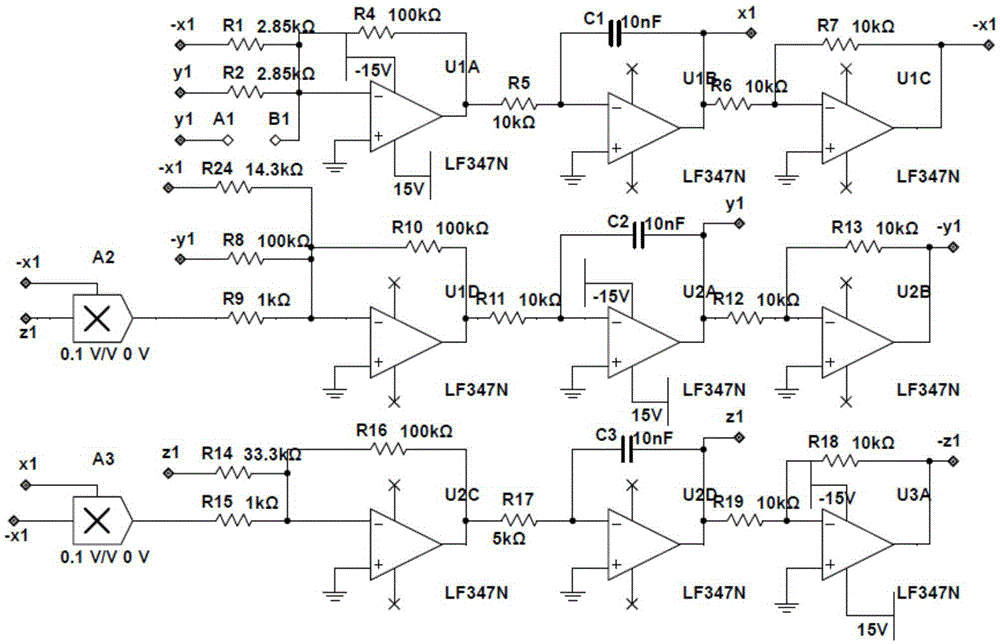

Adaptive synchronization method and adaptive synchronization circuit of y<2>-contained Chen hyper-chaotic system based on memristor

The present invention relates to a chaotic system synchronization method and a circuit, particularly to an adaptive synchronization method and adaptive synchronization circuit of y<2>-contained Chen hyper-chaotic system based on memristor. The memristor, served as a new physical component found by the HP labs in 2008, may take the place of the Chua's diode in the Chua's circuit to form the chaotic system, and also may be a component to be added into the three-dimensional chaotic systems, such as a Lorenz system, a Chen system and a Lorenz system, in order to form the hyper-chaotic system At present, the method and the circuit of serving the memristor as a component to form the choas or the hyper choas have come up, but the synchronization method of serving the memristor as a component to form the hyper-chaotic system has not yet come up, so that there is provided an inadequacy in the prior art. According to the invention, the y<2>-contained Chen hyper-chaotic system based on the memristor is put forward, and on this basis the adaptive synchronization method of y<2>-contained Chen hyper-chaotic system is provided.

Owner:王春梅

Simple second-order non-autonomous memristor chaotic signal generator

InactiveCN105827390AImprove stabilitySignificant chaotic propertiesDigital storageSecuring communication by chaotic signalsNonlinear phenomenaEngineering

Owner:CHANGZHOU UNIV

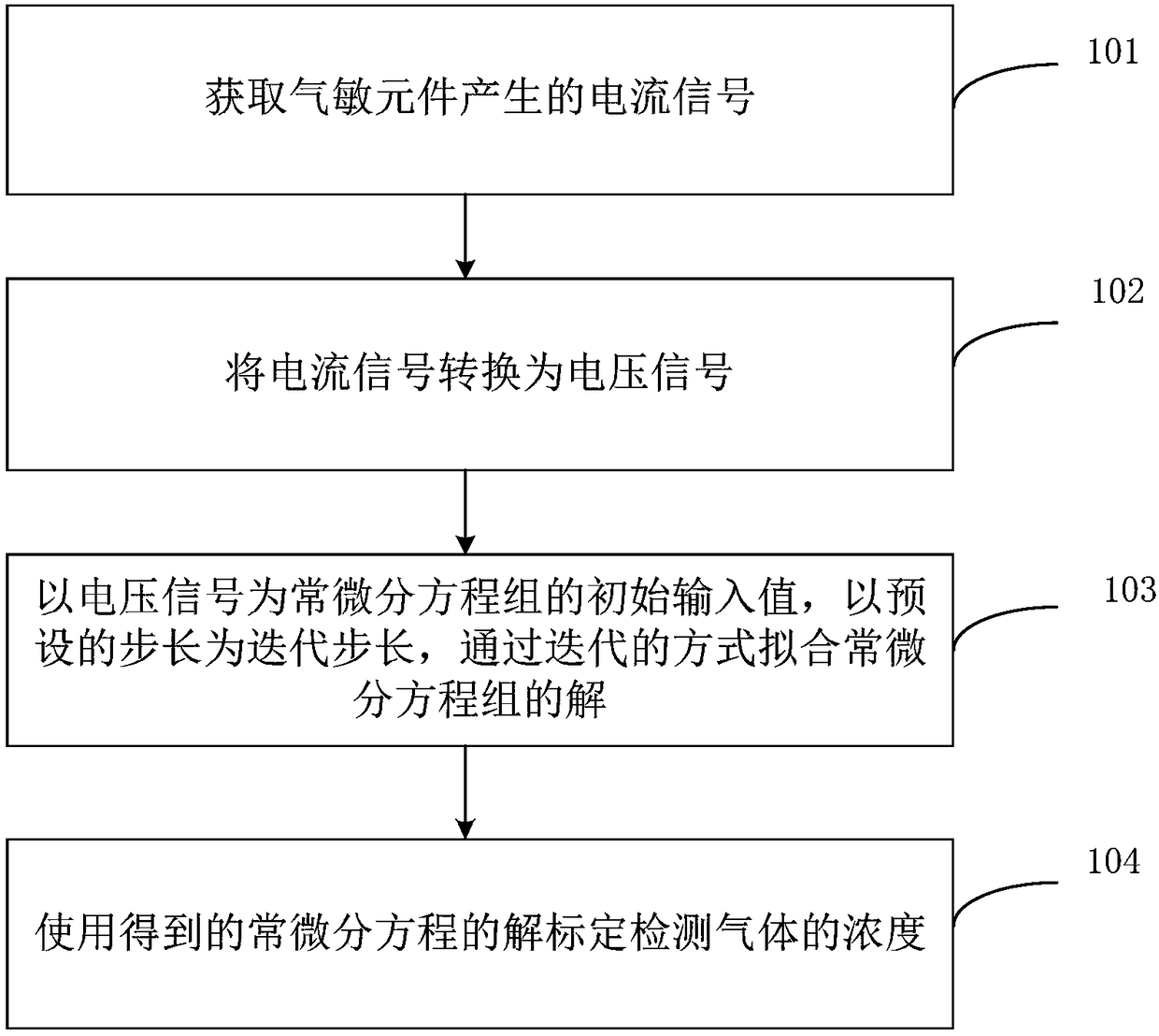

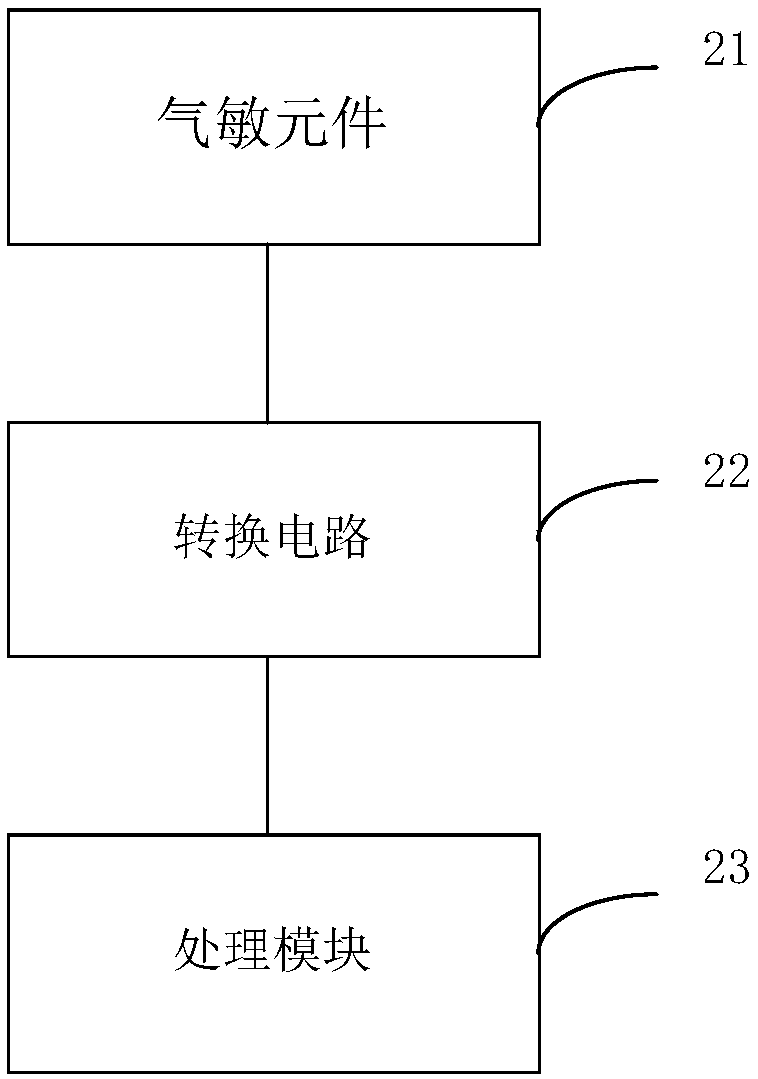

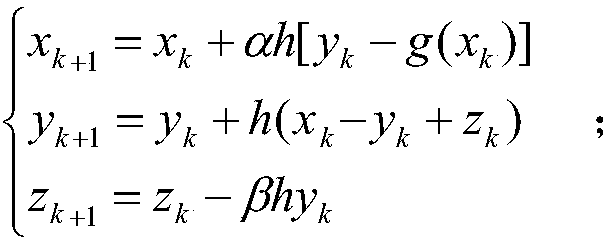

Gas concentration detection method and device

The invention discloses a gas concentration detection method and a gas concentration detection device which are used for solving the problem of relatively low gas concentration detection accuracy in arelated technology. The disclosed gas concentration detection method comprises the following steps: acquiring a current signal generated by a gas-sensitive element, wherein the current signal is generated when the gas-sensitive element adsorbs detection gas; converting the current signal into a voltage signal; with voltage signal as an initial input value of an ordinary differential equation setand a preset step length as an iteration step length, fitting a solution of the ordinary differential equation set in an iterative way, wherein the ordinary differential equation set is obtained by converting a Chua's circuit equation; calibrating the concentration of the detection gas by using the obtained solution of the ordinary differential equation set. Through the gas concentration detectionmethod and the gas concentration detection device, the gas concentration detection accuracy is improved.

Owner:GREE ELECTRIC APPLIANCES INC

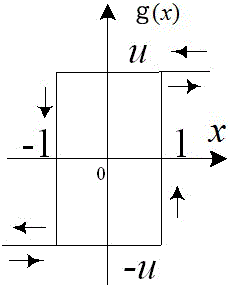

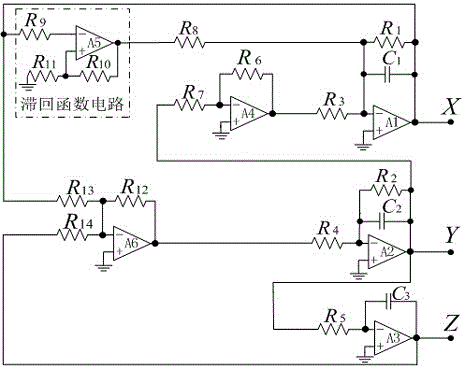

Chua's circuit realized based on hysteresis function

The invention relates to a Chua's circuit realized based on a hysteresis function. The Chua's circuit is composed of six operational amplifiers, fourteen resistors, and three capacitors. The operational amplifiers A1, A2, and A3 form an anti-phase integrator and the output terminals output chaotic signals X, Y, and Z; the operational amplifiers A4 and A6 form an inverting amplifier; and the operational amplifier A5 forms a hysteresis function circuit. When the circuit is in use, oscillograms of the X, Y, and Z can be observed on a common oscilloscope and X-Y, X-Z, and Y-Z phase graphs can be observed. The chaotic system of the Chua's circuit is enriched. The Chua's circuit is suitable for the chaotic science of the university, the experiment teaching and demonstration, science popularization, and experiment demonstration and the like. With the circuit, various chaotic wave forms, phase graphs, and chaotic development curves can be displayed. The circuit can be applied to the voice-analog-signal secret communication system widely.

Owner:HENAN VOCATIONAL COLLEGE OF APPLIED TECH +1

Chua's chaos system synchronization control circuit which is designed based on feedback current

InactiveCN103414548AThe design method is novel and effectiveSimple structureSecuring communicationSynchronous controlState variable

The invention discloses a Chua's chaos system synchronization control circuit which is designed based on feedback current, and the adding effect of a synchronous controller is analyzed from the perspective of the circuit. The synchronization control circuit comprises a driving system containing a lead-out variable, a synchronization controller and a response system. By using a feedback control principle, combined with the derivation process of a Chua's circuit dimensionless state equation, a feedback control circuit is designed, and combined with a voltage node part corresponding to a system state variable, the projection synchronization control of the Chua's circuit is realized through changing the feedback current in the circuit. According to the method, the module of the Chua's circuit is not needed, the essential structure of a chaos circuit is reserved, the design mode of the control circuit is novel and effective, the structure, assembly and use are simple, the control cost is low, and the circuit has an extensive application prospect and an application value in the field of chaos control.

Owner:NANJING NORMAL UNIVERSITY

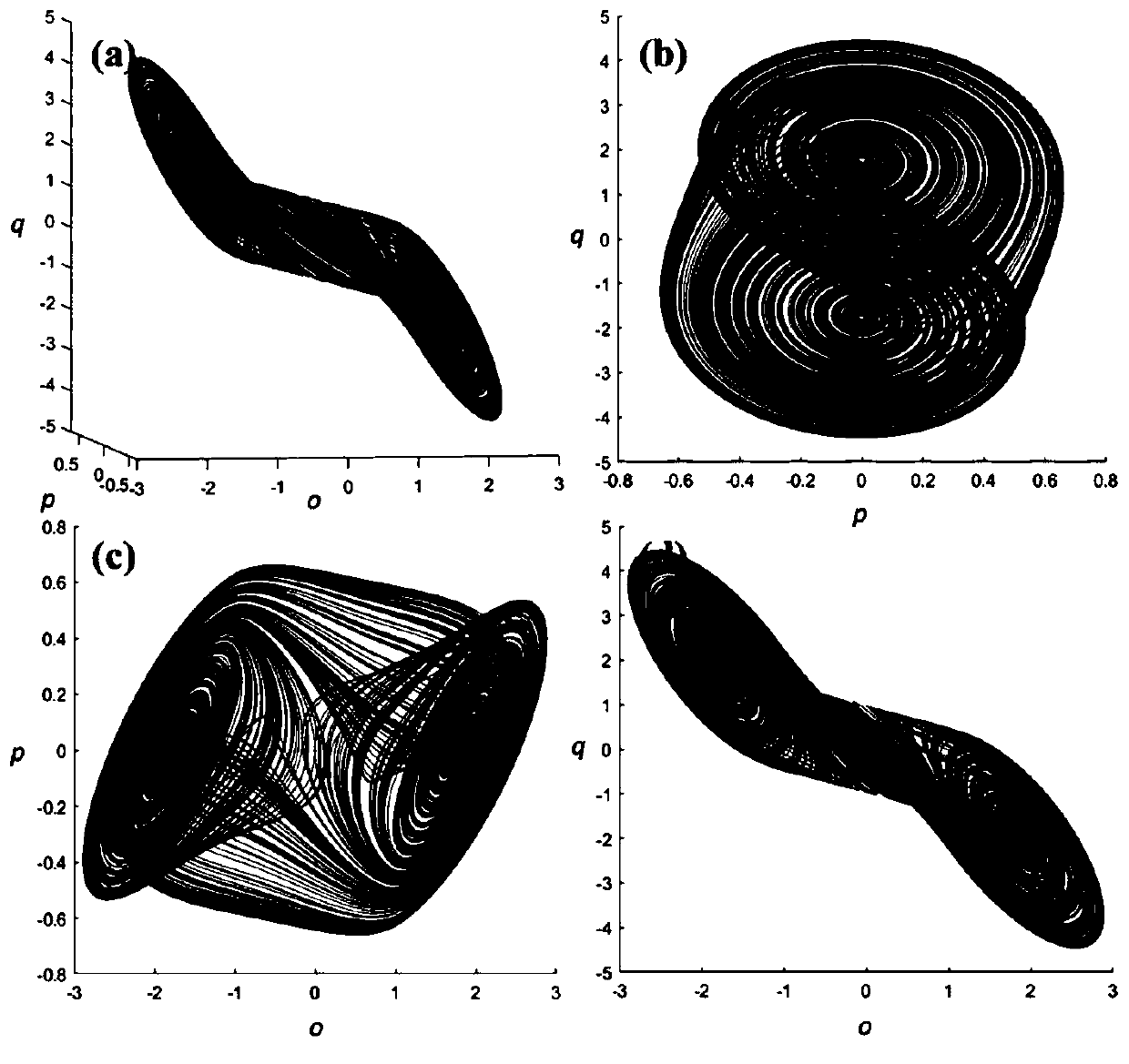

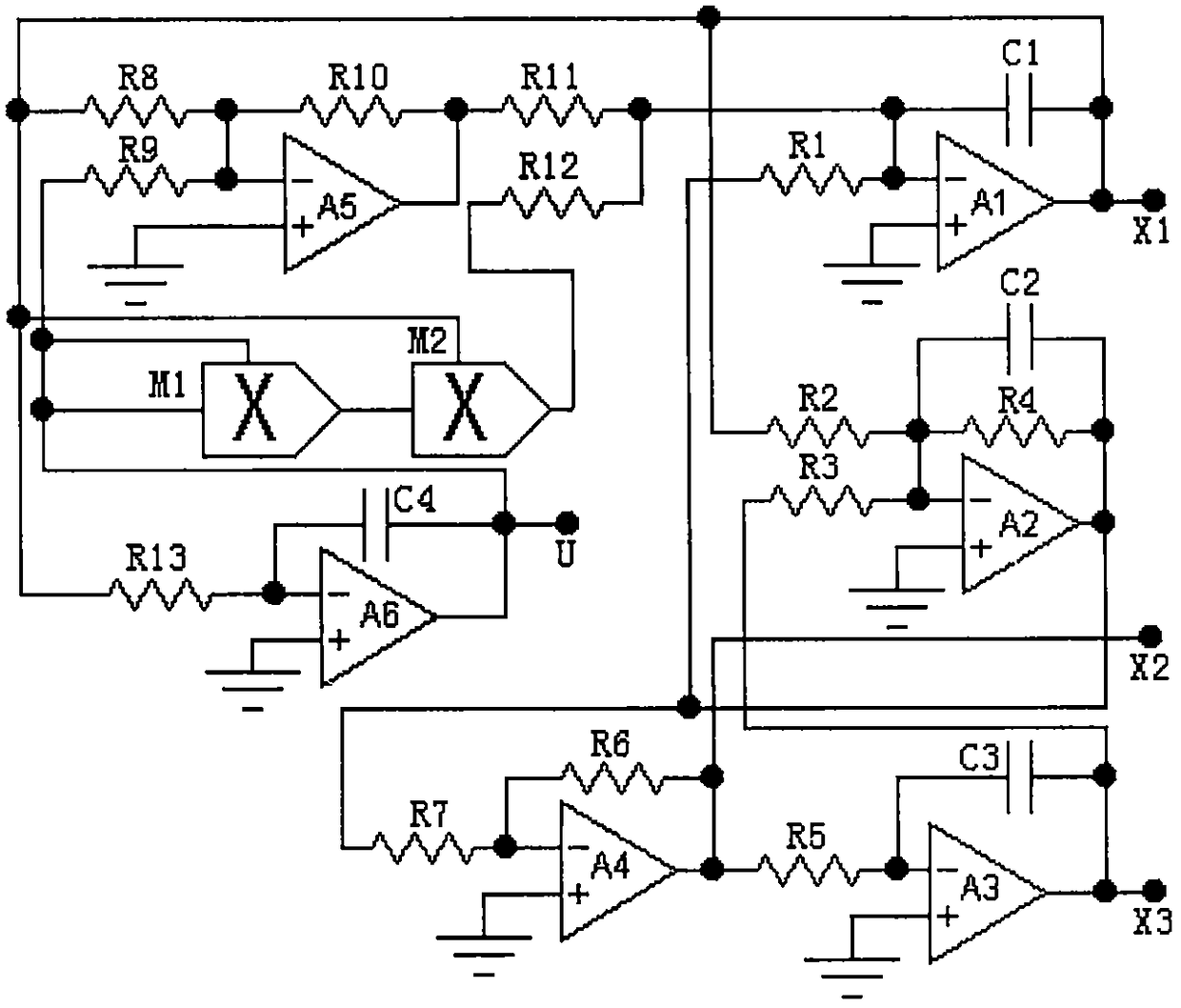

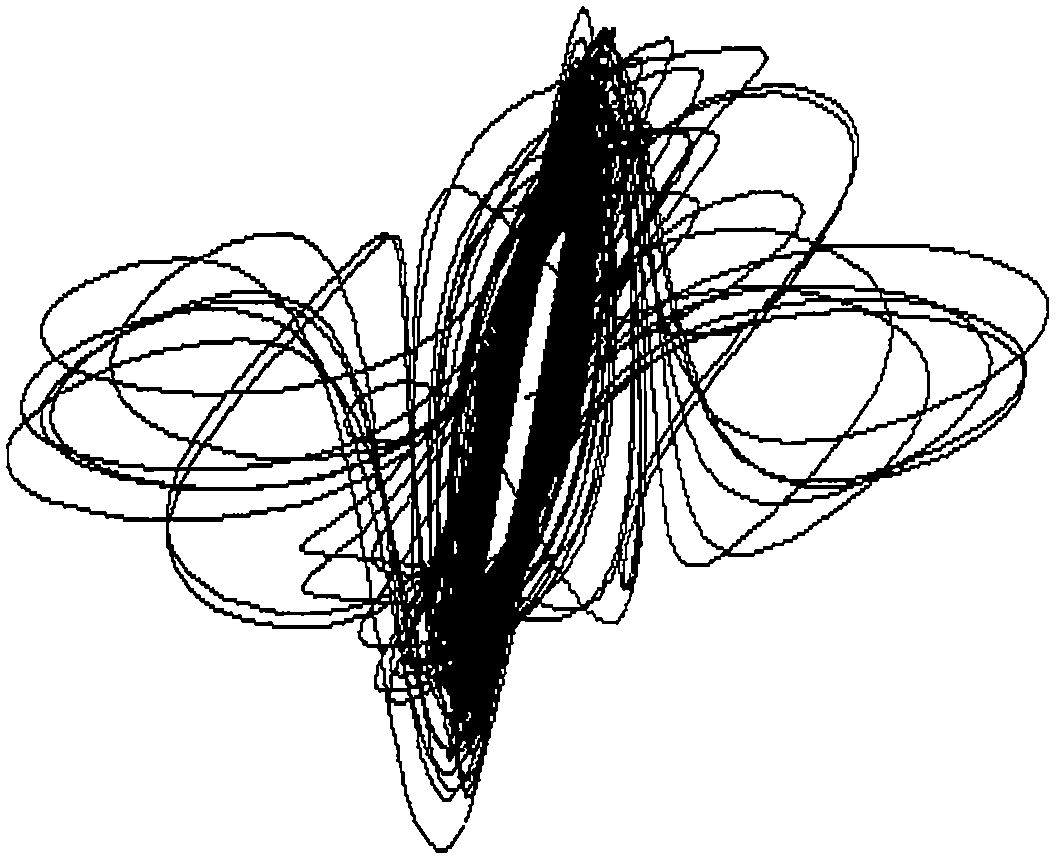

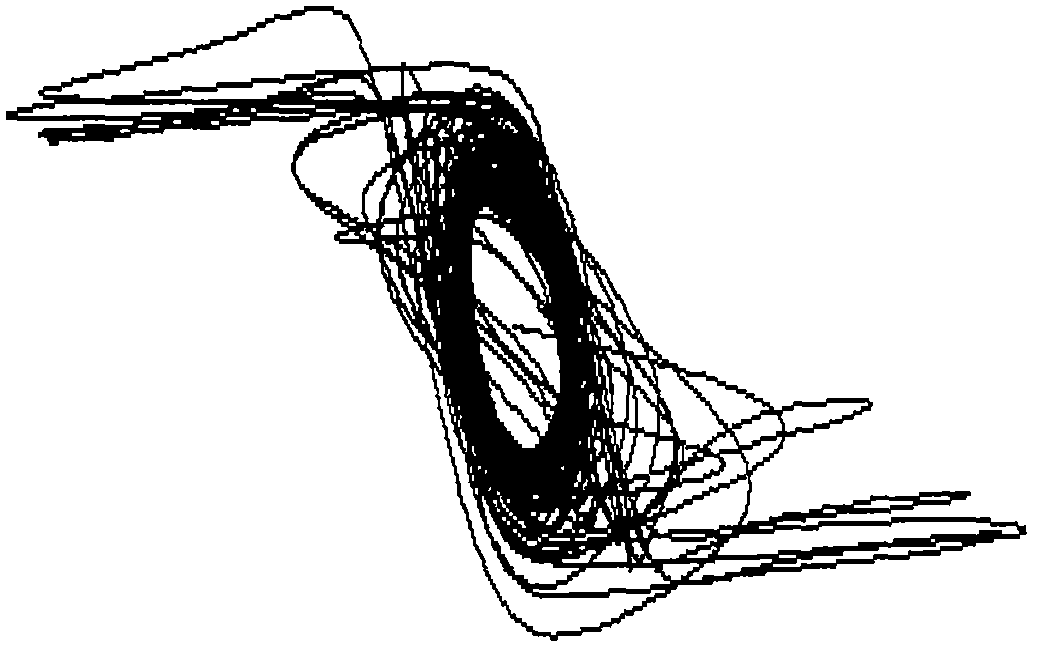

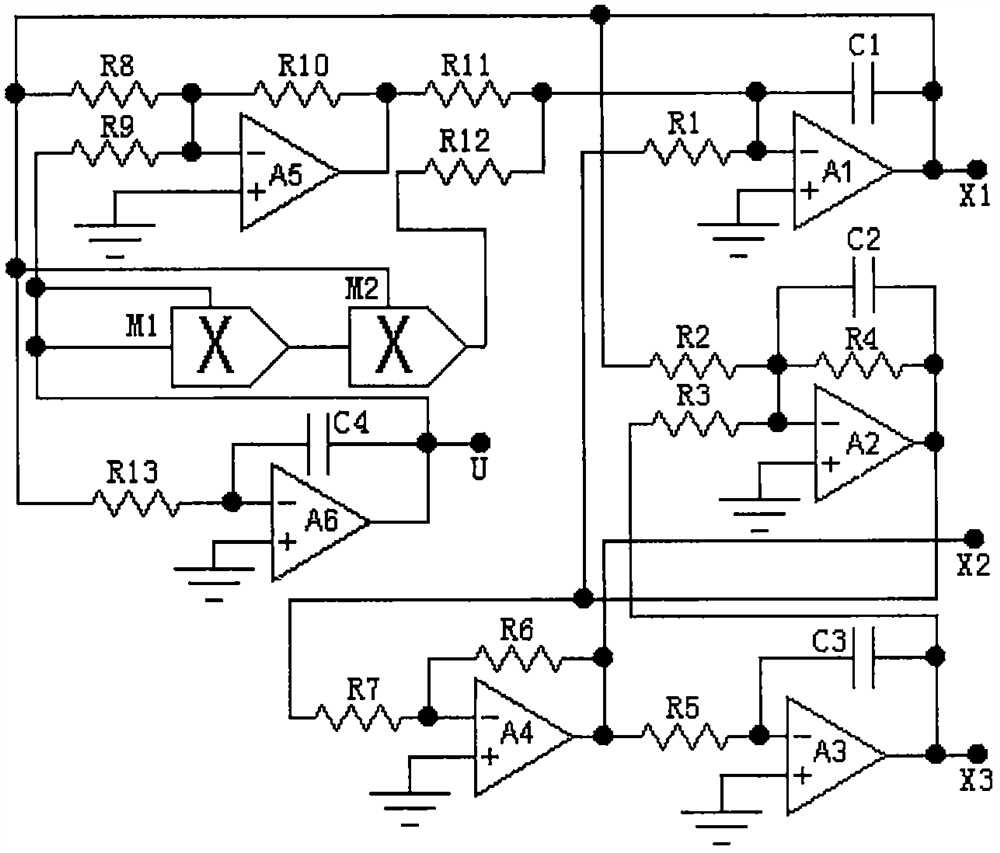

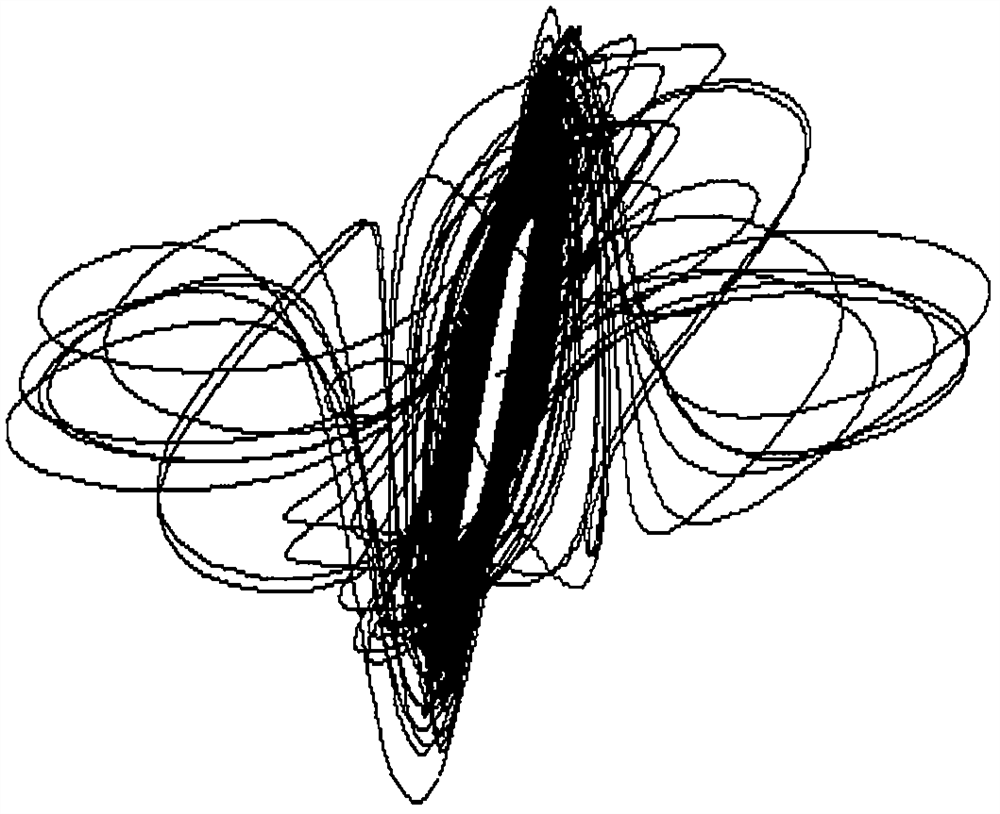

Memristor chaotic circuit based on Chua's circuit

The invention relates to a memristor chaotic circuit based on the Chua's circuit, which is characterized in that a first operational amplifier A1, a second operational amplifier A2 and a third operational amplifier A3 constitute a linear phase-reversing integrator, a fourth operational amplifier A4 constitutes a linear phase-reversing amplifier, and the output ends of the first operational amplifier A1, the fourth operational amplifier A4, the third operational amplifier A3 and a sixth operational amplifier A6 are respectively a chaotic signal output end X1, a chaotic signal output end X2, a chaotic signal output end X3 and a chaotic signal output end U; a phase-reversing integrator A1 is connected with a phase-reversing integrator A2, a phase-reversing integrator A6 and a second analog multiplier M2; the phase-reversing integrator A2 is connected with the first operational amplifier A2 and the fourth operational amplifier A4; the phase-reversing integrator A3 is connected with the phase-reversing integrator A2; the A1, A2, A3 and A4 constitute a third-order dynamic integrator circuit; and the A5, A6, M1 and M2 constitute a memristor circuit. Disclosed by the invention is a chaoticcircuit which can output various waveforms, phase diagrams and chaotic evolution curves of a memristor chaotic circuit based on the Chua's circuit and can form a chaotic secure communication system.

Owner:HEXI UNIV

Adaptive synchronization method and circuit for memristor-based Lorenz hyperchaotic system

The invention relates to chaotic system synchronization and a circuit, and especially relates to an adaptive synchronization method and circuit for a memristor-based Lorenz hyperchaotic system. As a newfound physical component in Hewlett-Packard Laboratories of 2008, the memristor can replace a Chua's diode in a Chua's circuit to form the chaotic system, and can also be added to three-dimensional chaotic systems as a component, such as a Lorenz system, a Chen system and a Lorenz system to form a hyperchaotic system; at present, the method and circuit of forming chaos or hyperchaos by taking the memristor as a component have been proposed, but a synchronization method for forming the hyperchaotic system by taking the memristor as a component has not been proposed yet and this is the disadvantage of the prior art; the invention provides a Lorenz hyperchaotic system by using the memristor, and the adaptive synchronization method of the chaotic system is provided on this basis.

Owner:胡春华

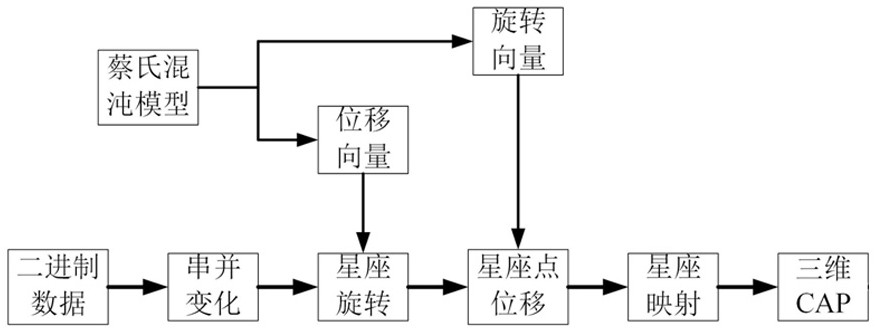

High-security transmission method based on three-dimensional constellation dual encryption

ActiveCN111865556AEncrypt twiceImprove securityMultiple keys/algorithms usageSecuring communication by chaotic signalsAlgorithmOriginal data

The invention discloses a high-security transmission method based on three-dimensional constellation dual encryption. The method comprises the following steps ofperforming serial-parallel conversion on binary data of a transmitting end,performing constellation mapping on the three-dimensional data to form constellation points,generating a constellation point displacement vector and a rotation vector by using a chaotic sequence of the Chua's chaotic model, and performing displacement transformation and rotation transformation on the three-dimensional constellation point,processing the encryptedthree-dimensional signal by utilizing three-dimensional carrier-free amplitude phase modulation, superposing the processed three-dimensional signal into a single-path signal, and transmitting the single-path signal in a channel,and demodulating the received signal at a receiving end to finally obtain original data. A Chua's circuit model is utilized to generate a chaotic sequence to perform displacement and rotation change on the position of a constellation point, so that twice encryption of a constellation diagram is realized, and the safety performance of the system is effectively improved;and the transmission capability of the system is effectively improved by utilizing the high gain index and the high anti-noise performance of the constellation.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

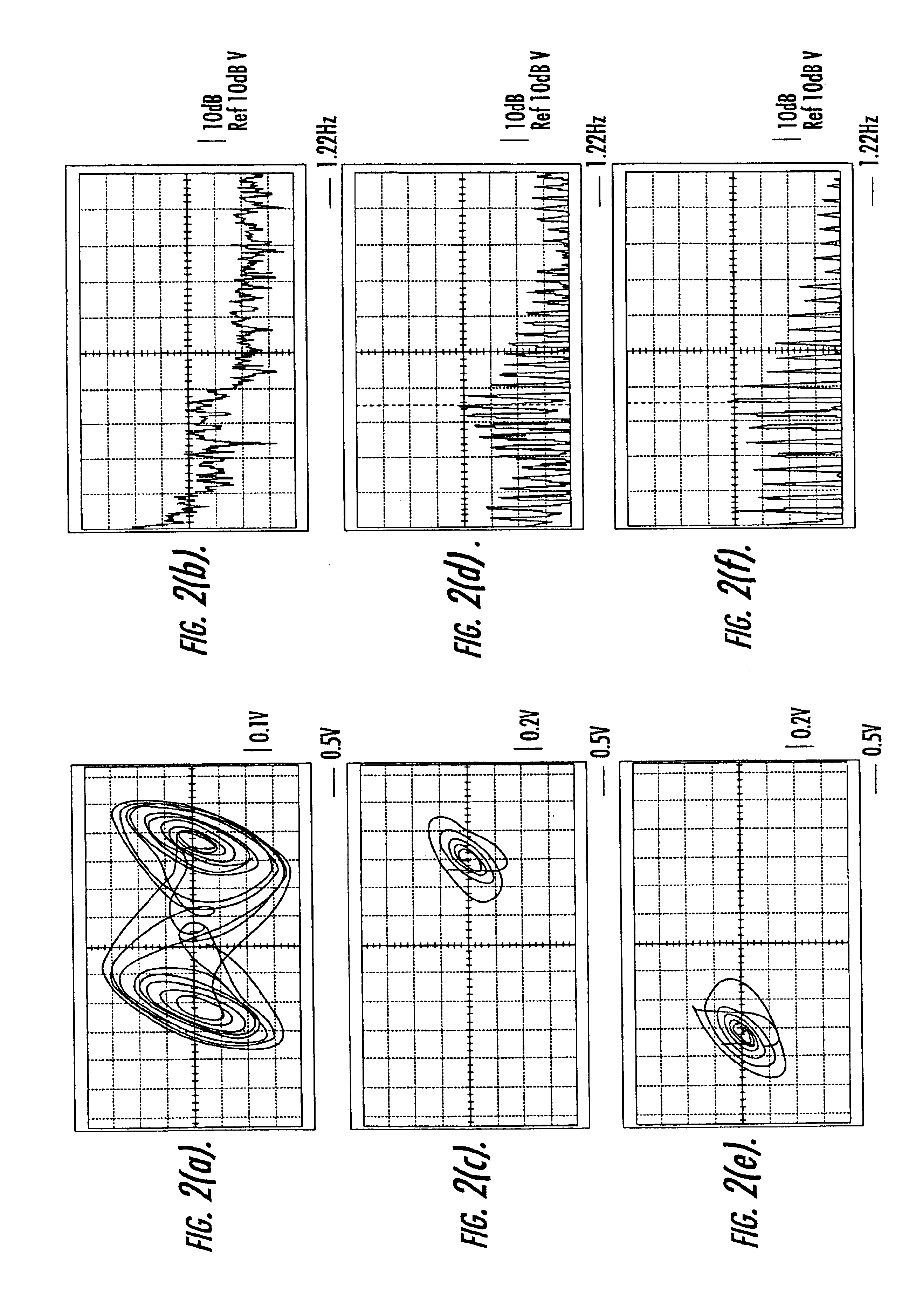

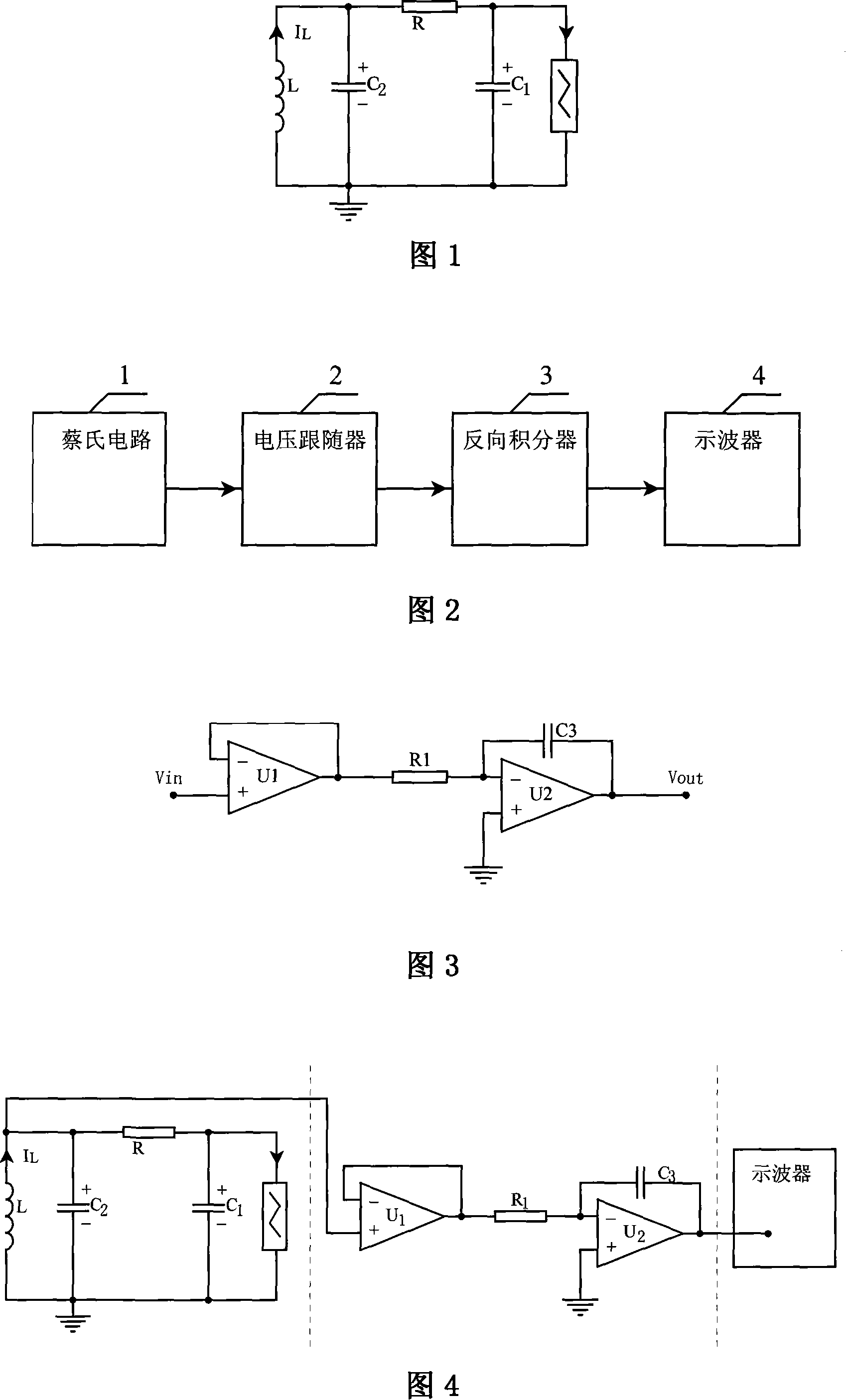

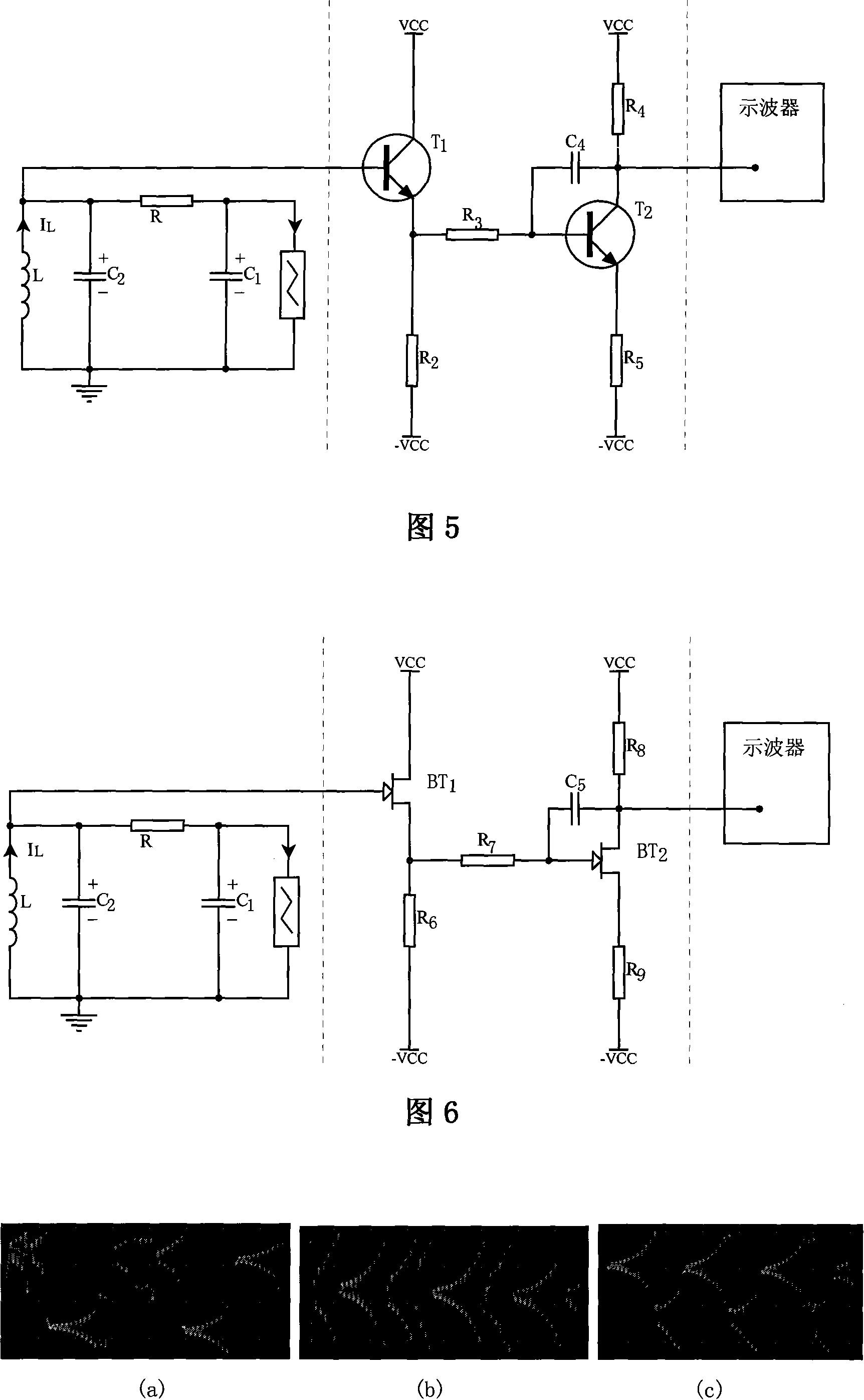

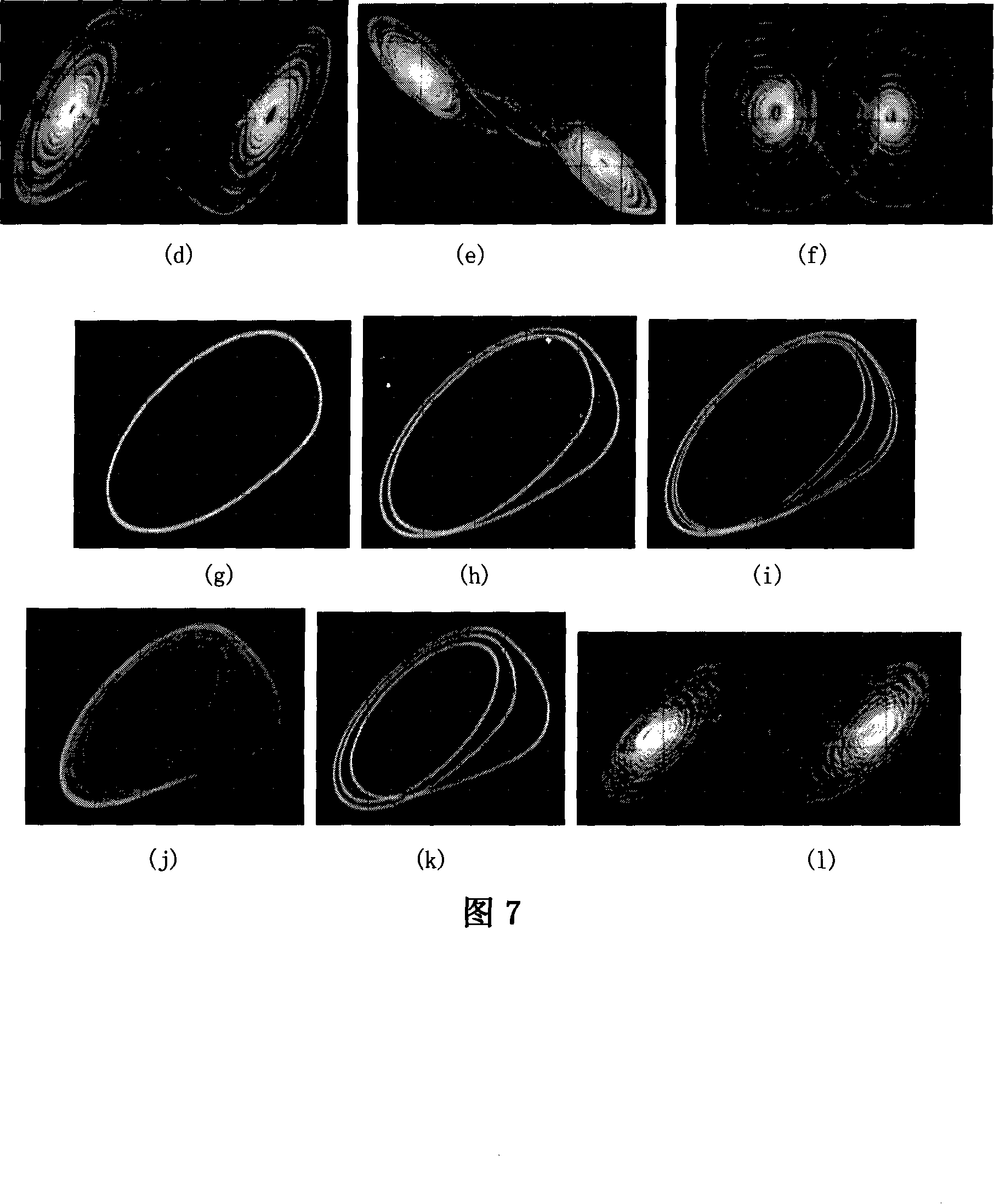

Cai's circuit inductor current oscilloscope display circuit

The utility model discloses an oscilloscope display circuit for the inductor current in Chua's circuit, which is characterized in that: the voltage relating to the current IL of the inductor L in the Chua's circuit (1) is reflected on the arm of the inductor L and is transferred to a reverse integrator (3) via a voltage follower (2) of the conversion circuit; the output voltage variable is proportional to the inductor current, thus the current-to-voltage conversion is realized and displayed on an oscilloscope (4). The utility model can directly measure and display the current flow of the Chua's circuit by an oscilloscope; the numbers of the three Chua's circuit waveforms which can be measured and displayed by the oscilloscope is enlarged from two to three, and the numbers of the three Chua's circuit phase diagrams also is enlarged to three compared with the original number two; thereby the oscilloscope is suitable for the debugging of the Chua's circuit and is more suitable for the teaching of the college chaos experiment and the demonstration of the science popularization chaos experiment in Chua's circuit.

Owner:张新国

Memristor-based Chen hyperchaotic system self-adaptive synchronization method and circuit

The invention relates to a chaotic system synchronization method and a circuit, and particularly relates to a memristor-based Chen hyperchaotic system self-adaptive synchronization method and a circuit. As a physical element which is newly discovered in a Hewlett-Packard laboratory in 2008, a Memristor can replace a Chua diode in a Chua circuit to form a chaotic system, and can be used as an element to be added into a three-dimensional chaotic system, such as a Lorenz system, a Chen system and a Lorenz system to form a hyperchaotic system. At present, the fact that the memristor is used as an element to form a chaotic or hyperchaotic method and circuit is proposed, but the fact that the memristor is used as an element to form a hyperchaotic system synchronization method is not proposed. For shortcomings in the prior art, according to the invention, the memristor is used to propose a Chen hyperchaotic system, and the self-adaptive synchronization method of the chaotic system is proposed on the basis.

Owner:王春梅

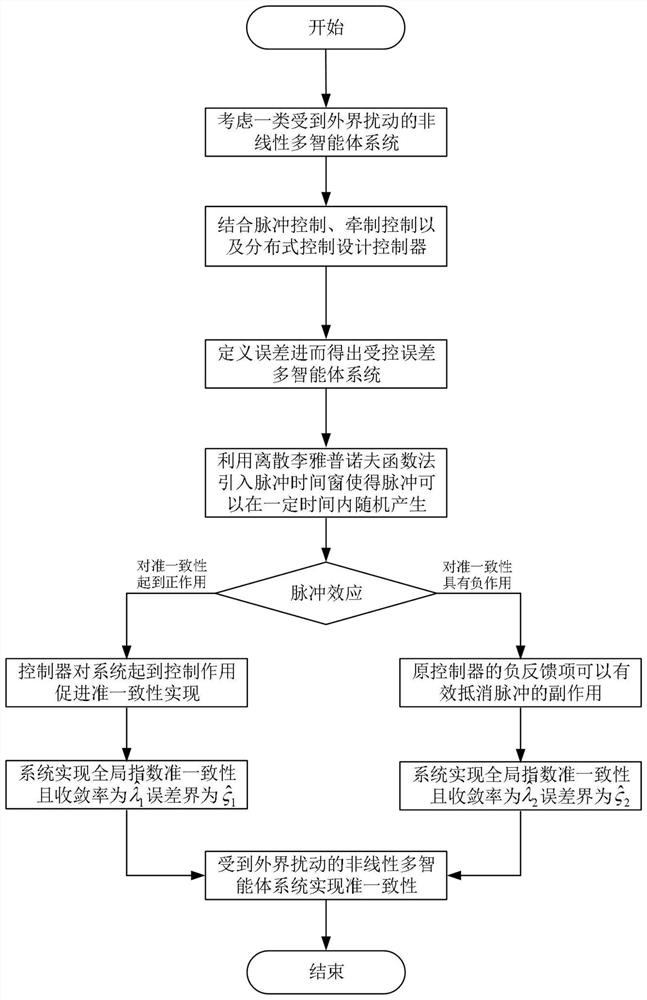

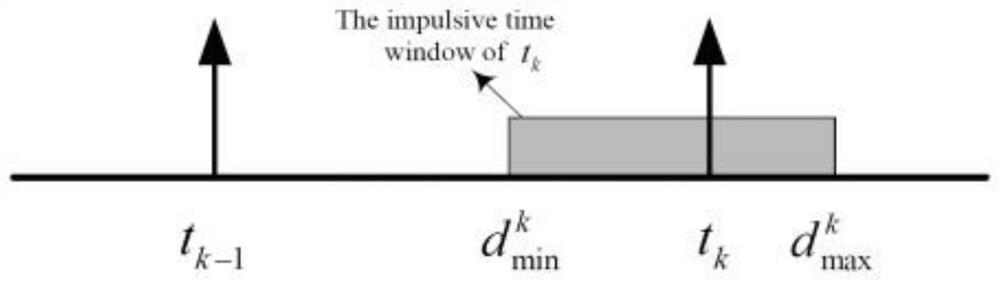

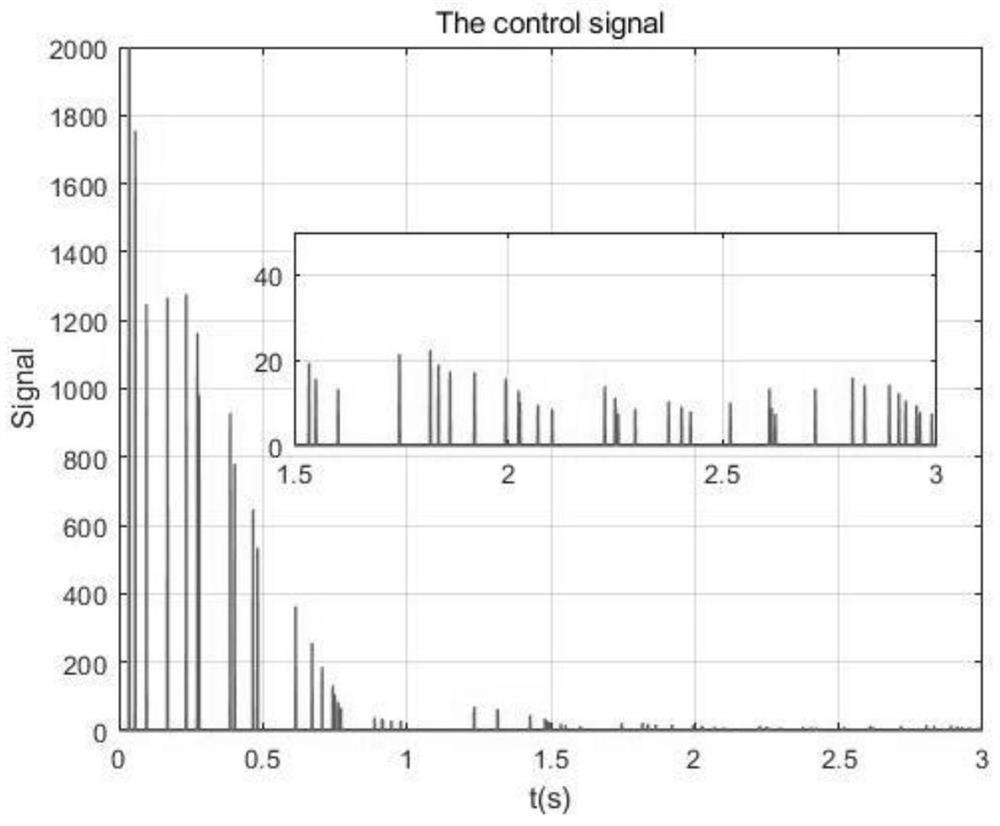

Pulse window-based disturbed nonlinear multi-agent quasi-consistency method and system

ActiveCN114721269AImprove fitnessReduce conservatismTotal factory controlAdaptive controlPulse controlAlgorithm

The invention discloses a disturbed nonlinear multi-agent quasi-consistency method based on a pulse window, and the method comprises the steps: building a nonlinear multi-agent system model with disturbance, introducing a pulse time window into a system through employing a discrete Lyapunov function method under the condition of considering a random pulse sequence, and achieving the quasi-consistency of a disturbed nonlinear multi-agent system. According to the influence of different pulse effects on the system global index quasi-consistency, a controller is designed by fully combining multiple control methods such as pulse control, containment control and distributed control, and full quasi-consistency discrimination conditions under different pulse effects are given by using methods such as parameter variation and pulse comparison principles. And accurately calculating a quasi-consistency convergence rate and an error boundary corresponding to the system. In addition, the Chua's circuit is used for carrying out numerical simulation so as to verify the effectiveness of the quasi-consistency method provided by the invention.

Owner:JIANGNAN UNIV

Self-adaptive synchronization method and circuit for Lorenz hyperchaotic system including y squaredbased on memristor

The invention relates to a synchronization method and circuit for a chaotic system, and in particular relates to a self-adaptive synchronization method and circuit for a Lorenz hyperchaotic system including y squared based on a memristor. The memristor is used as a physical component newly found in the hewlett-packard laboratory in 2008; the memristor not only can be used for replacing a chua's diode in a chua's circuit to form the chaotic system but also can be used as a component added into three-dimensional chaotic systems, such as a Lorenz system, a Chen system and the Lorenz system, so as to form the hyperchaotic system; currently, the chaotic or hyperchaotic method and circuit based on the memristor as one component are provided; but, the synchronization method of the hyperchaotic system based on the memristor as one component is still not provided, which is the deficiency in the prior art; the Lorenz hyperchaotic system including y squared is provided by utilizing the memristor; and the self-adaptive synchronization method of the chaotic system is provided on this basis.

Owner:胡春华

Adaptive synchronization method and circuit of memristor-based x-power-including Chen hyper-chaotic system

The invention relates to a chaotic system synchronization method and circuit, in particular to an adaptive synchronization method and circuit of a memristor-based x-power-including Chen hyper-chaotic system. As a physical element being newly discovered by the HP Labs in 2008, a memristor can construct a chaotic system instead of a Chua's diode in a Chua's circuit, and can be added into a three-dimensional chaotic system such as a Lorenz system, a Chen system and a Lorenz system as an element, thereby forming a hyper-chaotic system. At present, a method and a circuit for forming chaos or hyper-chaos by taking the memristor as an element are already put forward. However, a synchronization method for forming the hyper-chaos system by taking the memristor as an element is not put forward yet, which is a defect in the prior art. The invention provides the x-power-including Chen hyper-chaotic system by using the memristor, and provides the adaptive synchronization method of the chaotic system on the basis.

Owner:王春梅

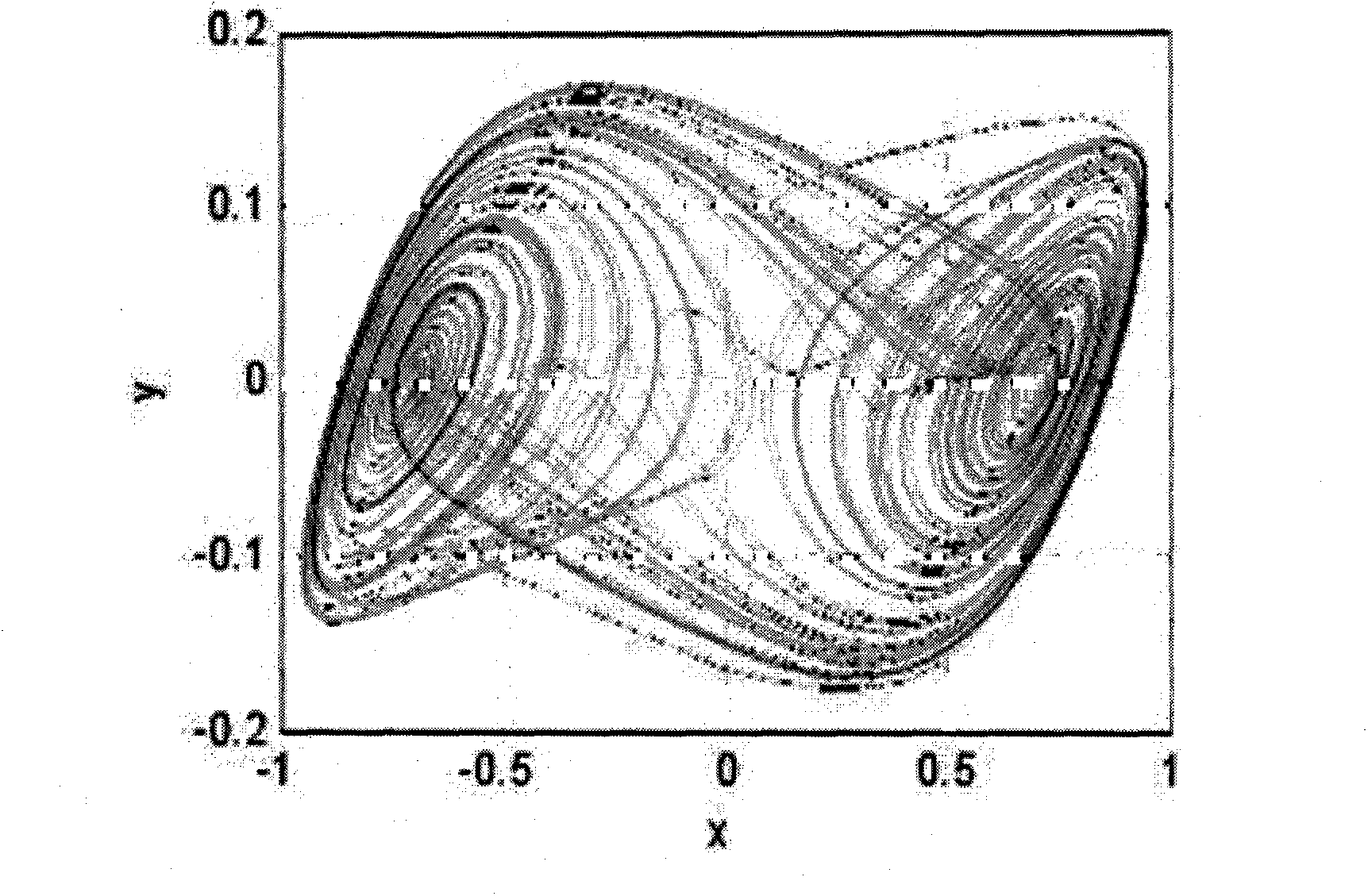

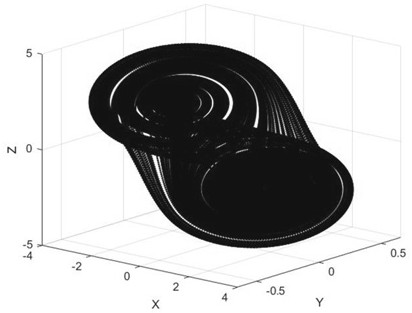

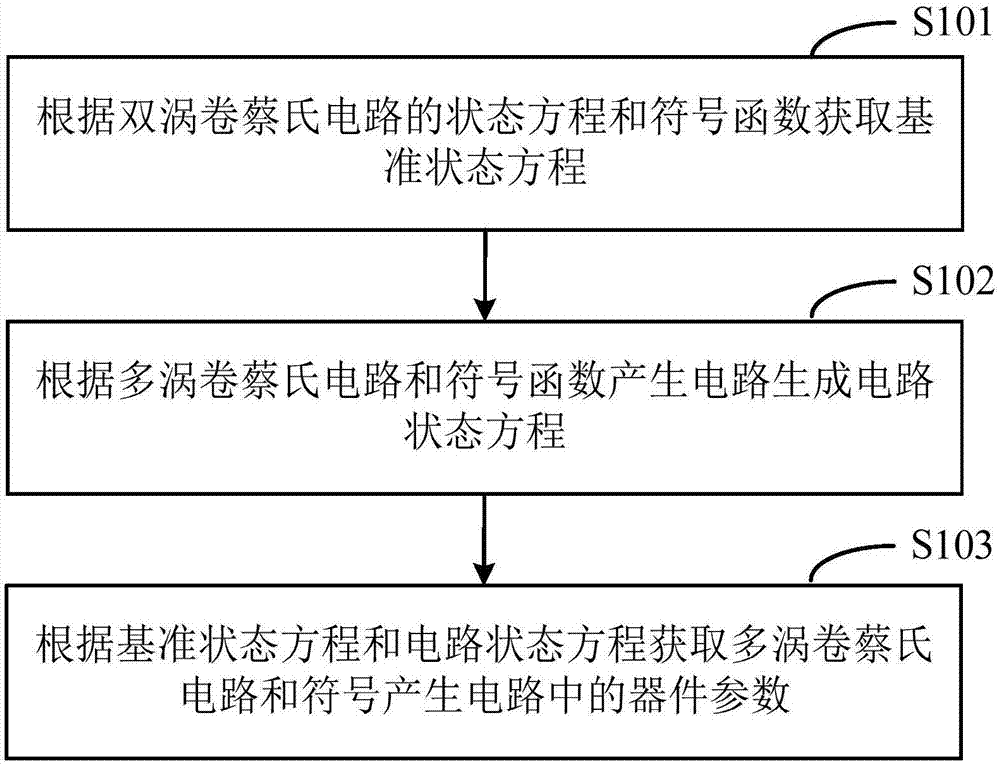

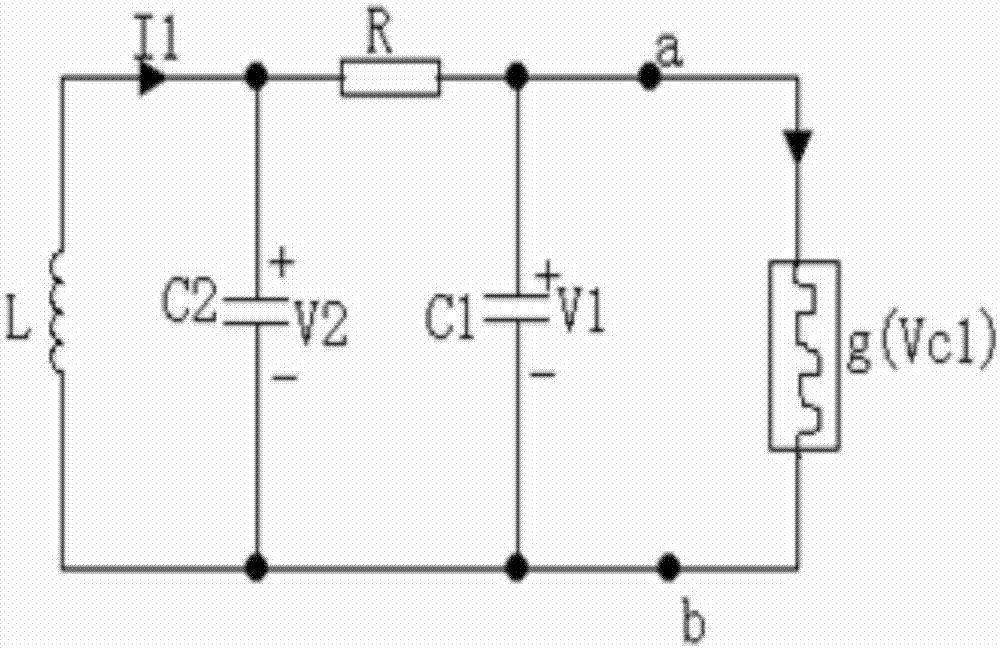

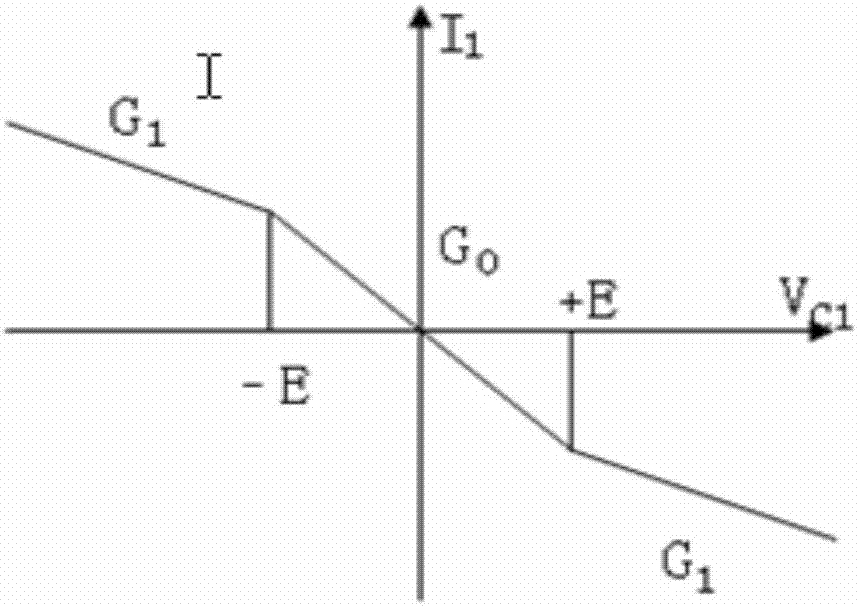

Design method of multi-scroll chaotic attractor circuit

ActiveCN107070631AEasy to debugSecuring communication by chaotic signalsMechanical engineeringNon linearite

The invention relates to the technical field of non-linear dynamics, and provides a design method of a multi-scroll chaotic attractor circuit. The design method comprises the following steps: acquiring a reference state equation according to a state equation of a double-scroll Chua's circuit and a symbol function; generating a circuit state equation according to a multi-scroll Chua's circuit and a symbol function generating circuit; and acquiring device parameters in the multi-scroll Chua's circuit and the symbol function generating circuit according to the reference state equation and the circuit state equation. Through adoption of the design method, the symbol function is introduced on the basis of an existing Chua's circuit, and a novel nonlinear chaos generation multi-scroll attractor system model is constructed. A system is stable and reliable, and easy to debug. 2n scrolls can be obtained by computer simulation, and a plurality of scrolls can be obtained in an actual hardware circuit.

Owner:SHENZHEN GRANDSUN ELECTRONICS

Five-order voltage-controlled memristor-based Chua's chaotic signal generator

PendingCN107819567AImprove stabilitySignificant chaotic characteristicsSecuring communication by chaotic signalsNonlinear phenomenaHemt circuits

The invention discloses a five-order voltage-controlled memristor-based Chua's chaotic signal generator. The chaotic signal generator is achieved by connecting an inductor in a coupling resistor branch circuit of a classic Chua's circuit in series and directly adopting a non-ideal voltage-controlled memristor to replace a non-linear resistor element-Chua's diode in the classic Chua's circuit. Thecircuit comprises the classic Chua's circuit and the non-ideal voltage-controlled memristor equivalent realization circuit. According to the five-order voltage-controlled memristor-based Chua's chaotic signal generator, complex non-linear phenomena such as chaotic attractors and periodic limit cycles can be generated by adjusting parameters of circuit elements, so that a novel chaotic signal generator is achieved; and generated chaotic signals are high in stability, have the significant chaotic characteristic and achieve a great pushing effect on development of a memristor-based chaotic circuit in practical engineering application.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Memristor chaotic circuit based on Chua's circuit

The invention relates to a memristor chaotic circuit based on the Chua's circuit, which is characterized in that a first operational amplifier A1, a second operational amplifier A2 and a third operational amplifier A3 constitute a linear phase-reversing integrator, a fourth operational amplifier A4 constitutes a linear phase-reversing amplifier, and the output ends of the first operational amplifier A1, the fourth operational amplifier A4, the third operational amplifier A3 and a sixth operational amplifier A6 are respectively a chaotic signal output end X1, a chaotic signal output end X2, a chaotic signal output end X3 and a chaotic signal output end U; a phase-reversing integrator A1 is connected with a phase-reversing integrator A2, a phase-reversing integrator A6 and a second analog multiplier M2; the phase-reversing integrator A2 is connected with the first operational amplifier A2 and the fourth operational amplifier A4; the phase-reversing integrator A3 is connected with the phase-reversing integrator A2; the A1, A2, A3 and A4 constitute a third-order dynamic integrator circuit; and the A5, A6, M1 and M2 constitute a memristor circuit. Disclosed by the invention is a chaoticcircuit which can output various waveforms, phase diagrams and chaotic evolution curves of a memristor chaotic circuit based on the Chua's circuit and can form a chaotic secure communication system.

Owner:HEXI UNIV

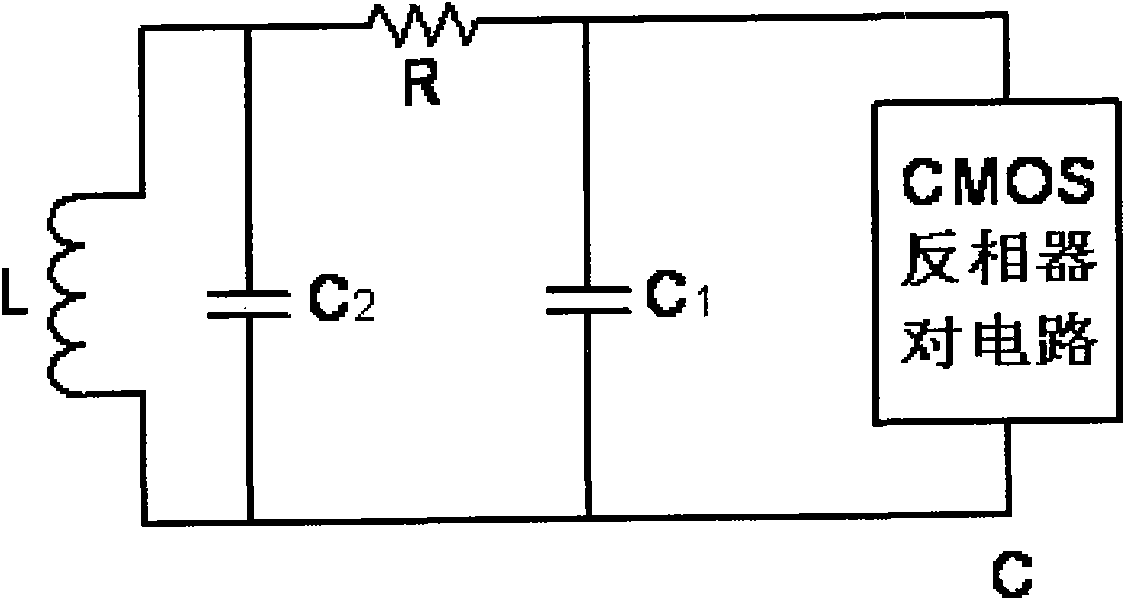

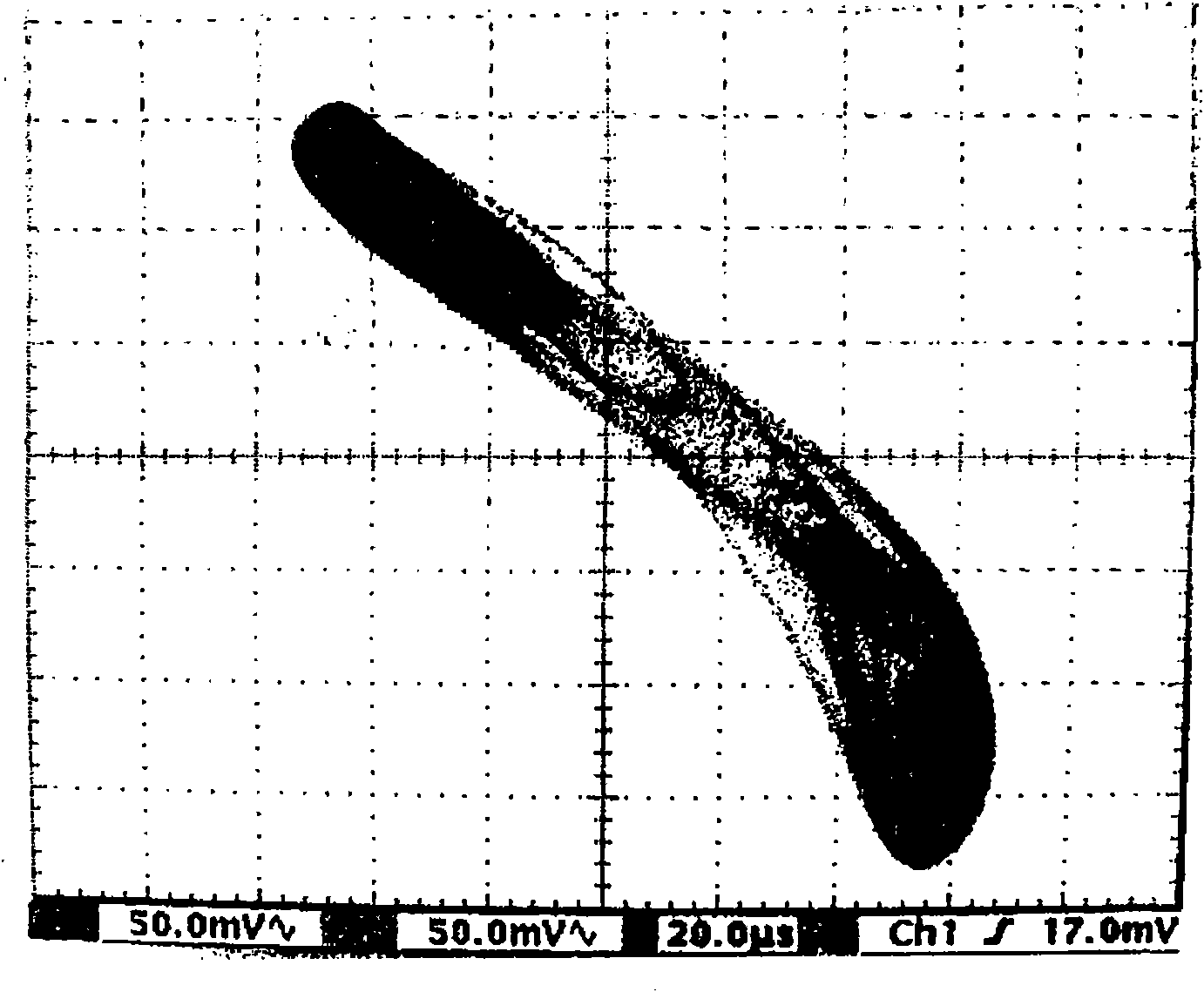

CMOS (Complementary Metal-Oxide-Semiconductor) inverter pair based method and circuit for designing high-speed chaotic oscillator

InactiveCN101964630BOvercome the disadvantage of lower operating frequencyEasy to manufactureOscillations generatorsSecuring communicationEngineeringP channel

Owner:ZHEJIANG UNIV

CMOS (Complementary Metal-Oxide-Semiconductor) inverter pair based method and circuit for designing high-speed chaotic oscillator

InactiveCN101964630AOvercome the disadvantage of lower operating frequencyEasy to manufactureOscillations generatorsSecuring communicationP channelOperating frequency

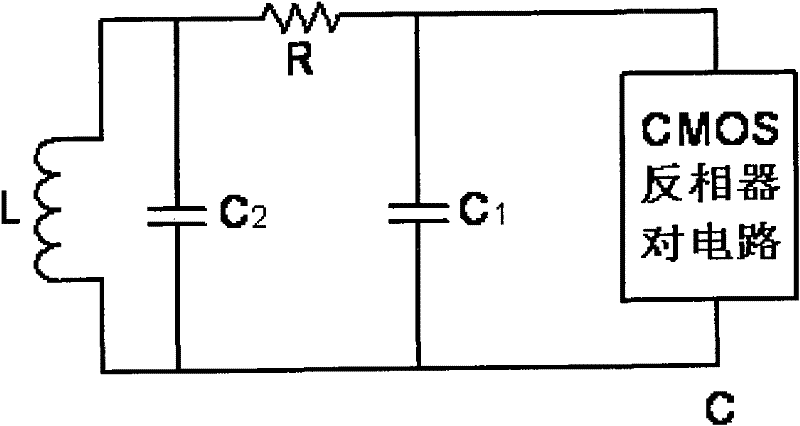

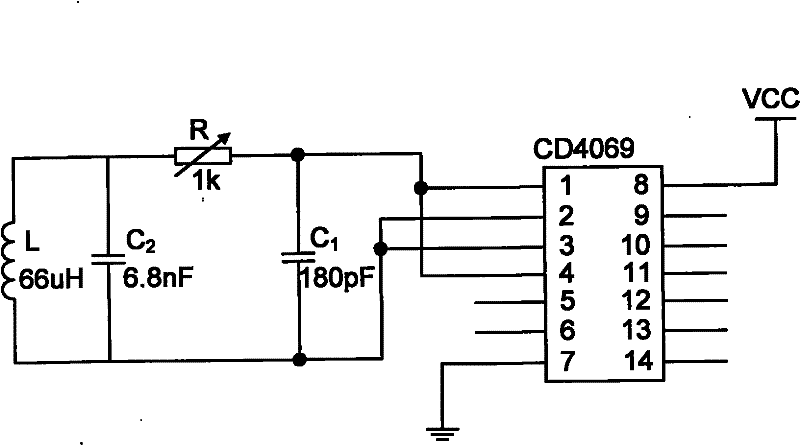

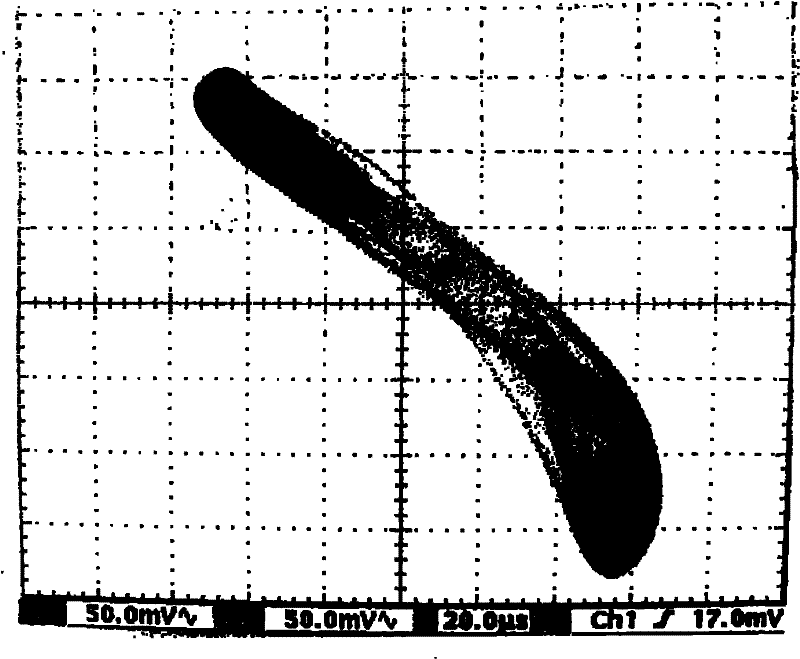

The invention discloses a CMOS (Complementary Metal-Oxide-Semiconductor) inverter pair based method and a circuit for designing a high-speed chaotic oscillator. In the invention, a negative resistance circuit consisting of a CMOS inverter pair is used for replacing a negative resistance circuit based on an operational amplifier in a Chua's circuit to generate chaotic oscillation; a CMOS inverter circuit consists of a chip CD4069 or consists of two PMOS (P-channel Metal Oxide Semiconductor) tubes and two NMOS (N-channel metal oxide semiconductor) tubes, inherits the characteristics of the traditional Chua's circuit and is used for generating chaotic oscillation signals; and when a CMOS inverter pair is used, i.e. two reversely connected inverters are used as a negative resistance circuit of an oscillator, the defect of lower working frequency of the traditional Chua's circuit can be overcome, and the inverter pair can work with a higher frequency, so that high-speed chaotic oscillation can be generated, and the working frequency reaches / MHz. The circuit can be designed and realized by using discrete devices, and the chip of the high-speed chaotic oscillator can be designed and realized by using a standard CMOS process, thus the circuit is beneficial to the manufacture and the production of chaotic signal sources in a large scale with low cost.

Owner:ZHEJIANG UNIV

A High Security Transmission Method Based on Double Encryption of Three-Dimensional Constellation

ActiveCN111865556BEncrypt twiceImprove securityMultiple keys/algorithms usageSecuring communication by chaotic signalsOriginal dataSecure transmission

The invention discloses a high-security transmission method based on double encryption of three-dimensional constellations, which comprises the following steps: performing serial-to-parallel conversion on the binary data at the transmitting end; performing constellation mapping on the three-dimensional data to form constellation points; using Cai's chaotic model The chaotic sequence generates the displacement vector and rotation vector of the constellation point, and performs displacement transformation and rotation transformation on the three-dimensional constellation point; uses three-dimensional carrier-free amplitude phase modulation to process the encrypted three-dimensional signal, and superimposes the processed three-dimensional signal into a single-channel signal. Enter the channel transmission; demodulate the received signal at the receiving end, and finally obtain the original data. The invention utilizes the Chua's circuit model to generate a chaotic sequence to change the position of the constellation point by displacement and rotation, realizes two encryptions of the constellation diagram, and effectively improves the security performance of the system; utilizes the high gain index and high anti-noise performance of the constellation to effectively improve the system transmission capacity.

Owner:NANJING UNIV OF INFORMATION SCI & TECH