Novel adiabatic logic gating circuit

A logic gate circuit and adiabatic technology, applied in the field of logic gate circuits, can solve problems such as energy consumption, achieve ultra-low power consumption and reduce circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

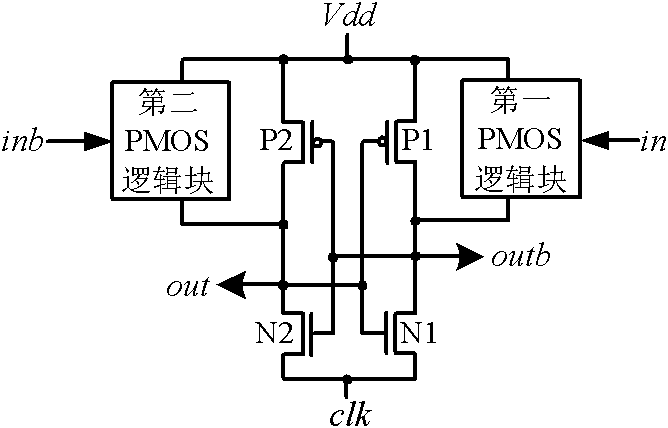

[0030] Embodiment 1: A novel adiabatic logic basic gate buffer (or inverter) circuit, comprising a first PMOS transistor P1, a second PMOS transistor P2, a first NMOS transistor N1 and a second NMOS transistor N2, the first PMOS transistor The source of P1 and the drain of the second PMOS transistor P2 are connected to the positive power supply terminal Vdd in parallel, the source of the first NMOS transistor N1 and the drain of the second NMOS transistor N2 are connected in parallel to the clock signal terminal clk, and the first PMOS transistor The drain of P1 is connected to the drain of the first NMOS transistor N1 and connected to the negative output signal terminal outb, the source of the second PMOS transistor P2 is connected to the source of the second NMOS transistor N2 and connected to the positive output signal terminal out, The gate of the first PMOS transistor P1 and the gate of the first NMOS transistor N1 are connected in parallel to the positive output signal te...

Embodiment 2

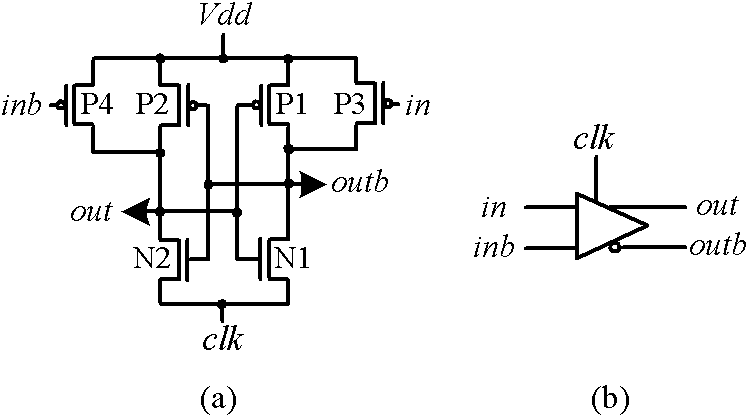

[0031] Embodiment 2: A novel adiabatic logic AND gate circuit, comprising a first PMOS transistor P1, a second PMOS transistor P2, a first NMOS transistor N1 and a second NMOS transistor N2, the source of the first PMOS transistor P1 and the second PMOS transistor The drain of the transistor P2 is connected to the positive power supply terminal Vdd in parallel, the source of the first NMOS transistor N1 and the drain of the second NMOS transistor N2 are connected to the clock signal terminal clk in parallel, and the drain of the first PMOS transistor P1 is connected to the first NMOS The drain of the transistor N1 is connected to the negative output signal terminal outb at the same time, the source of the second PMOS transistor P2 is connected to the source of the second NMOS transistor N2 and connected to the positive output signal terminal out, and the gate of the first PMOS transistor P1 The gate of the first NMOS transistor N1 is connected to the positive output signal term...

Embodiment 3

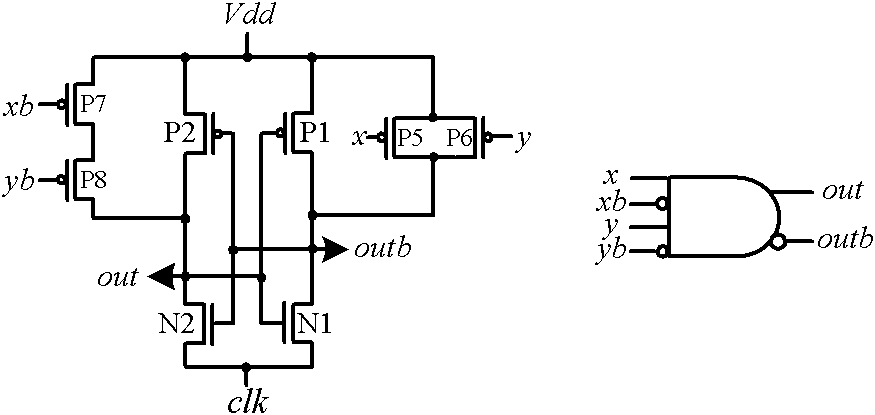

[0032] Embodiment 3: A novel adiabatic logic OR gate circuit, comprising a first PMOS transistor P1, a second PMOS transistor P2, a first NMOS transistor N1 and a second NMOS transistor N2, the source of the first PMOS transistor P1 and the second PMOS transistor The drain of the transistor P2 is connected to the positive power supply terminal Vdd in parallel, the source of the first NMOS transistor N1 and the drain of the second NMOS transistor N2 are connected to the clock signal terminal clk in parallel, and the drain of the first PMOS transistor P1 is connected to the first NMOS The drain of the transistor N1 is connected to the negative output signal terminal outb at the same time, the source of the second PMOS transistor P2 is connected to the source of the second NMOS transistor N2 and connected to the positive output signal terminal out, and the gate of the first PMOS transistor P1 The gate of the first NMOS transistor N1 is connected to the positive output signal termi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More