Silicon on insulator (SOI) wafer and formation method thereof

A technology of wafers and single crystal silicon wafers, which is applied in the field of SOI wafers and their formation, can solve the problems of reducing the insulation performance of the insulating layer, damage to the lattice of single crystal silicon wafers, and high production costs, and achieve simple process, high quality, and low production costs. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

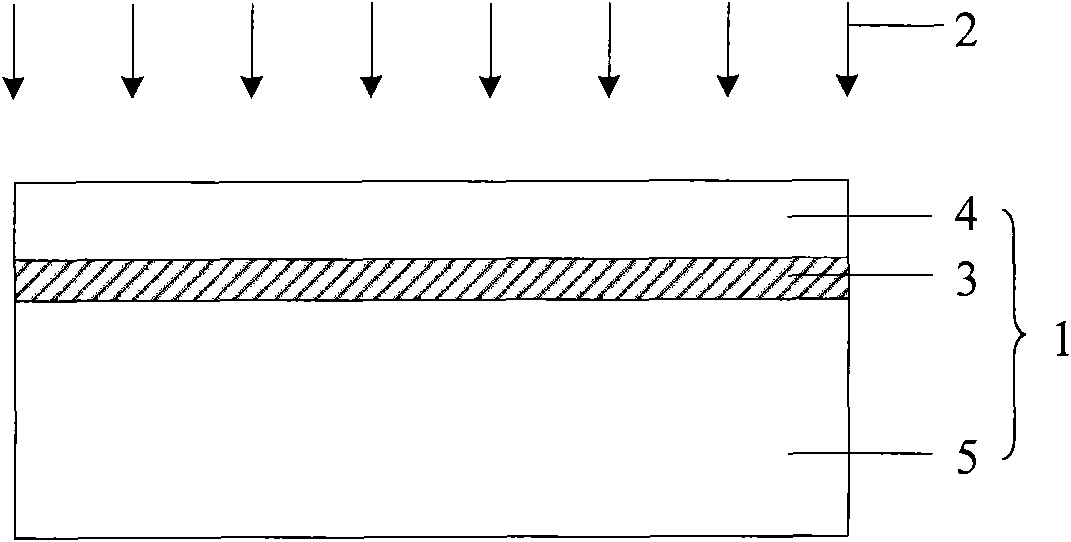

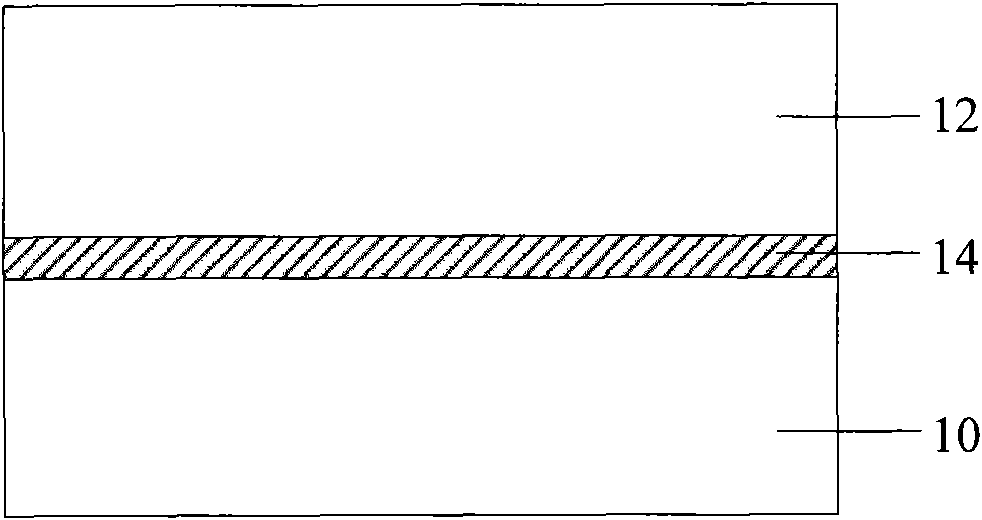

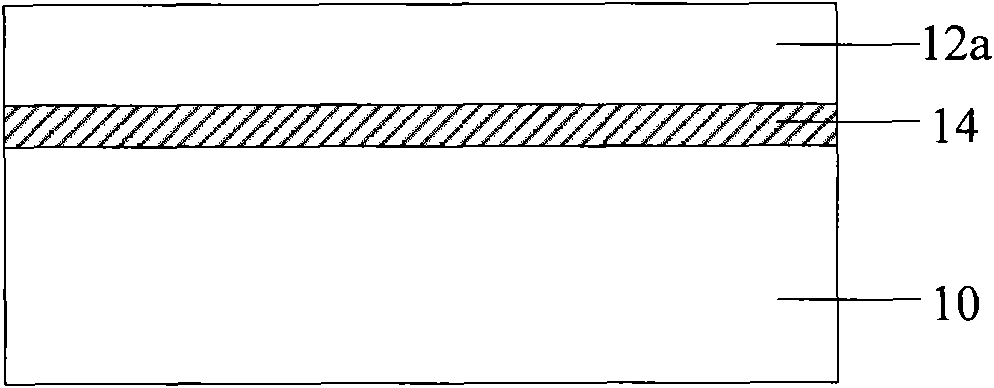

[0031] Several existing methods for manufacturing SOI wafers either cause damage to the crystal lattice of a single crystal silicon wafer, affecting the insulation capability of the SOI wafer, or have complex processes, high manufacturing costs, and poor quality of the formed SOI wafer. Embodiments of the present invention form grooves and cavities in the single crystal silicon wafer, and then form an insulating layer and an insulating material layer in the grooves and cavities as the insulating layer of the SOI wafer, and the insulating material layer in the cavities is made of single crystal silicon Slices are separated into silicon base and top silicon. The insulating silicon oxide of this process is formed by deposition or spin coating process, which not only solves the problem that the oxygen injection and annealing process in the oxygen injection isolation technology destroy the crystal lattice of the single crystal silicon wafer and reduce the insulation performance of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com