Bipolar junction transistor and bipolar CMOS (Complementary Metal Oxide Semiconductor) integrated circuit as well as manufacturing method

A technology of bipolar junction type and manufacturing method, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, circuit, etc., can solve the unfavorable integration of bipolar process and CMOS process, and the large difference in the thickness of bipolar junction transistors. Achieve the effect of improving current voltage and frequency characteristics and reducing series resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

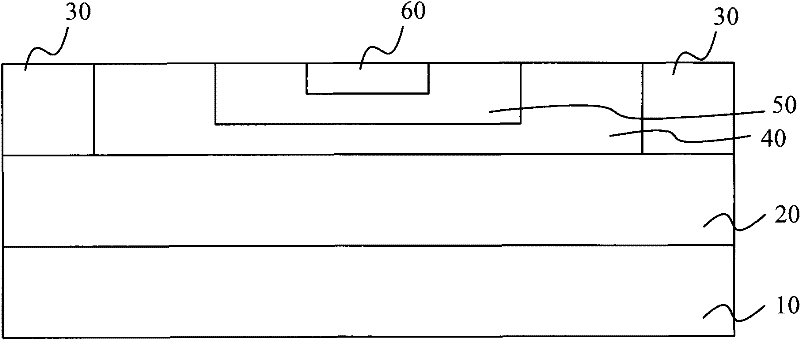

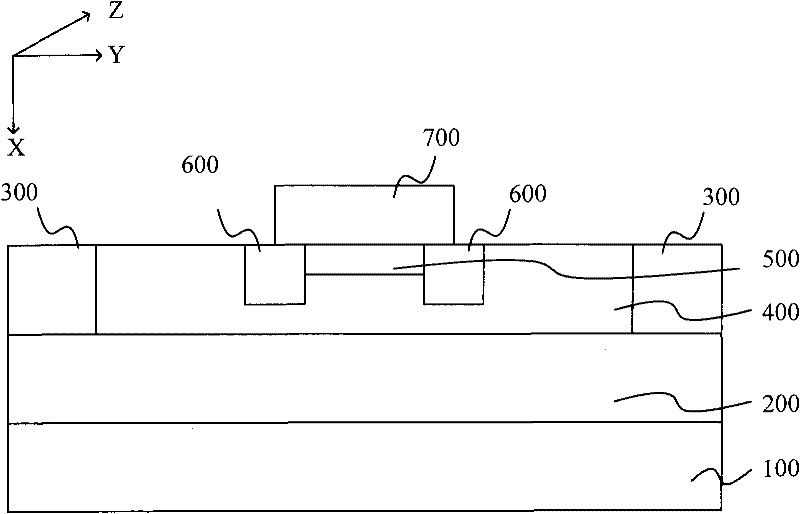

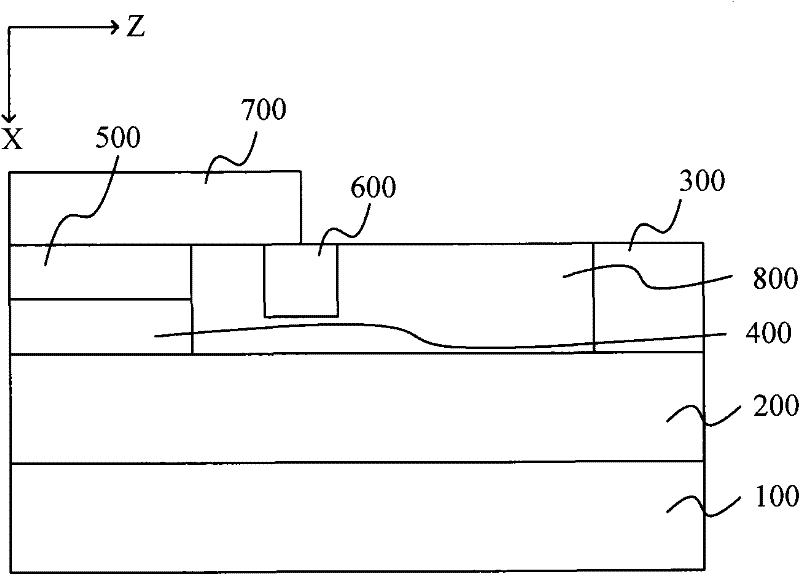

[0052] combine Figure 2a and Figure 2b As shown, an embodiment of the bipolar junction transistor of the present invention includes:

[0053] The first doped region 400 and the second doped region 800 adjacently distributed in the silicon-on-insulator substrate, and the first doped region 400 and the second doped region 800 are surrounded by a first isolation layer 300;

[0054] a third doped region 500 in the first doped region 400, the third doped region 500 is electrically connected to the second doped region 800;

[0055] A second isolation layer 600 surrounding the third doped region 500 in the first doped region 400 and the second doped region 800;

[0056] The doped polysilicon layer 700 on the third doped region 500 and the second isolation layer 600,

[0057] The doped polysilicon layer 700 , the third doped region 500 , and the first doped region 400 serve as the emitter region, the base region, and the collector region of the bipolar junction transistor, respec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More