Static analysis-based method and system for detecting RTL (Resistor Transistor Logic) design errors

A design error and static analysis technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as small processing scale, limited application, explosion, etc., and achieve high automation, shorten verification time, and large design scale.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

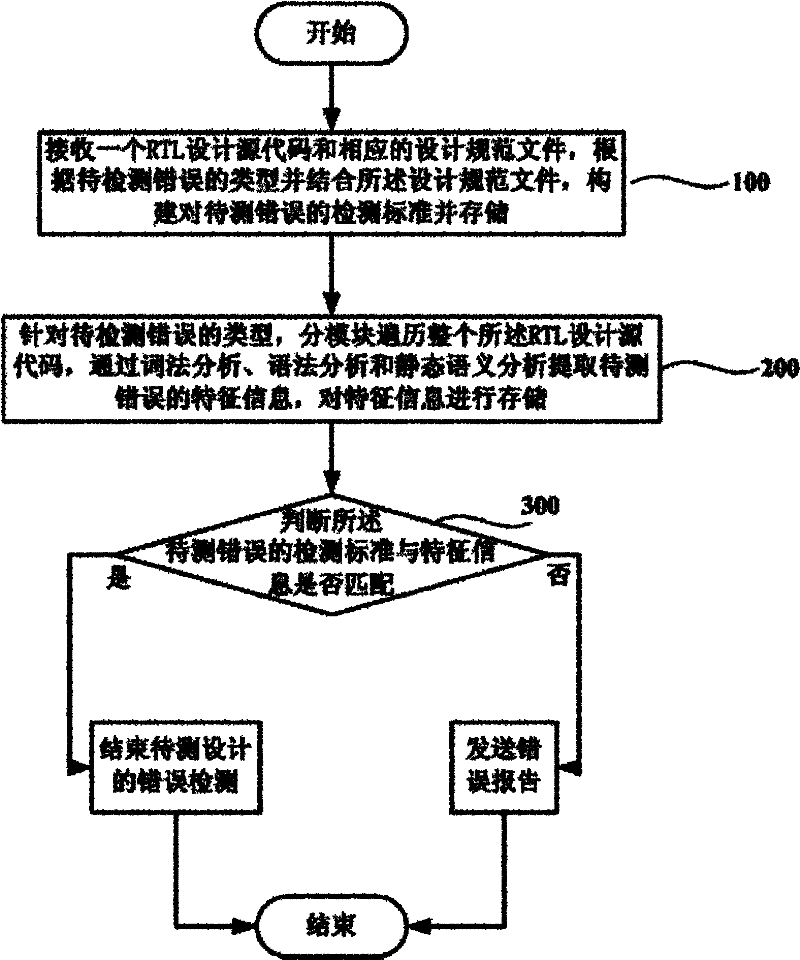

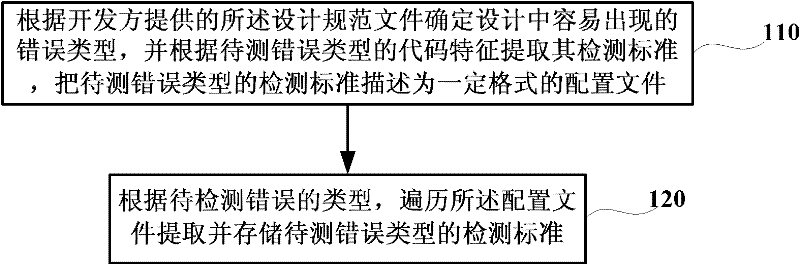

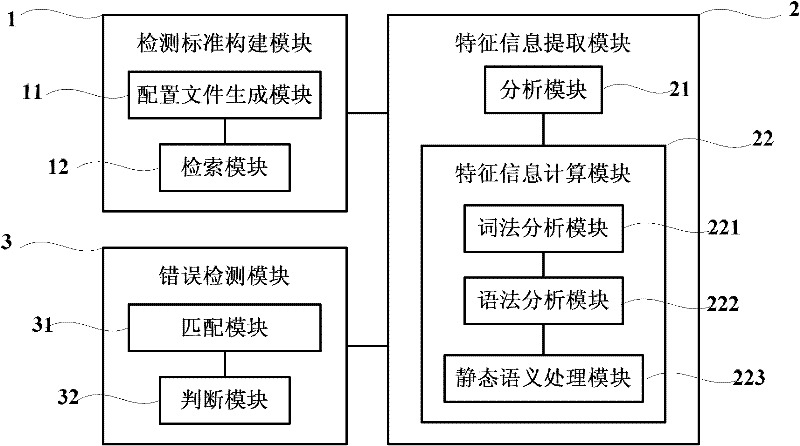

[0054] In order to make the purpose, technical solution and advantages of the present invention clearer, a static analysis-based Register Transfer Level (RTL) design error detection method and system of the present invention will be further described below in conjunction with the accompanying drawings and embodiments. Detailed description. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0055] A static analysis-based RTL design error detection method and system of the present invention, by scanning the source code of the design to be tested, extracts the characteristic information of the error to be tested based on the static analysis technology; detection. Its advantage is that there is no runtime overhead, fast running speed, high degree of automation, reusability between different designs, and common errors in the design can be found before simulation, which can help ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More