Multilayer wiring board

A wiring substrate and wiring technology, which is applied in the manufacture of multilayer circuits, high-current matching devices, waveguides, etc. problems such as transmission of frequency signals to achieve high installation density, suppress the deterioration of transmission signals, and achieve the effect of high density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

[0043] Next, a first embodiment of the present invention will be described based on the drawings.

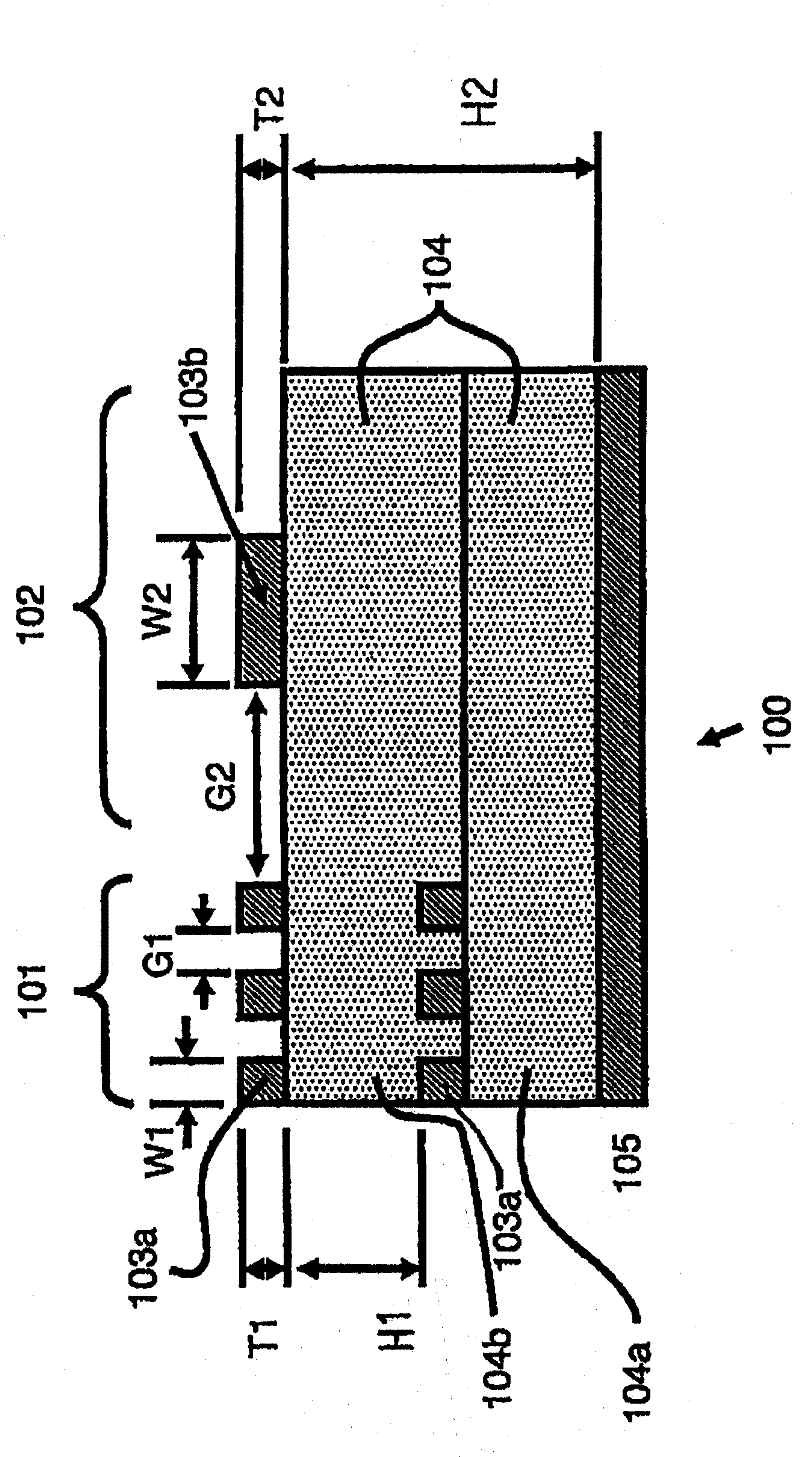

[0044] Such as figure 1 As shown, the multilayer wiring board 100 as the circuit board according to the first embodiment of the present invention has a first wiring region (multilayer wiring region) 101 and a second wiring region (multilayer wiring region) 102 . In the first wiring region (multilayer wiring region) 101, plate-like or film-like insulating layers 104a, 104b and wiring 103a are stacked on each other. The second wiring region (multilayer wiring region) 102 has wiring 103b on an insulating layer 104 having twice the thickness H1 of the insulating layer per one layer of the first wiring region 101. above the insulating layer thickness H2. The wiring width W2 of the wiring 103 b is set to be twice or more than the wiring width W1 of the wiring 103 a of the first wiring region 101 . 105 is a conductive film.

[0045] The multilayer wiring substrate 100 of the first ...

no. 2 approach

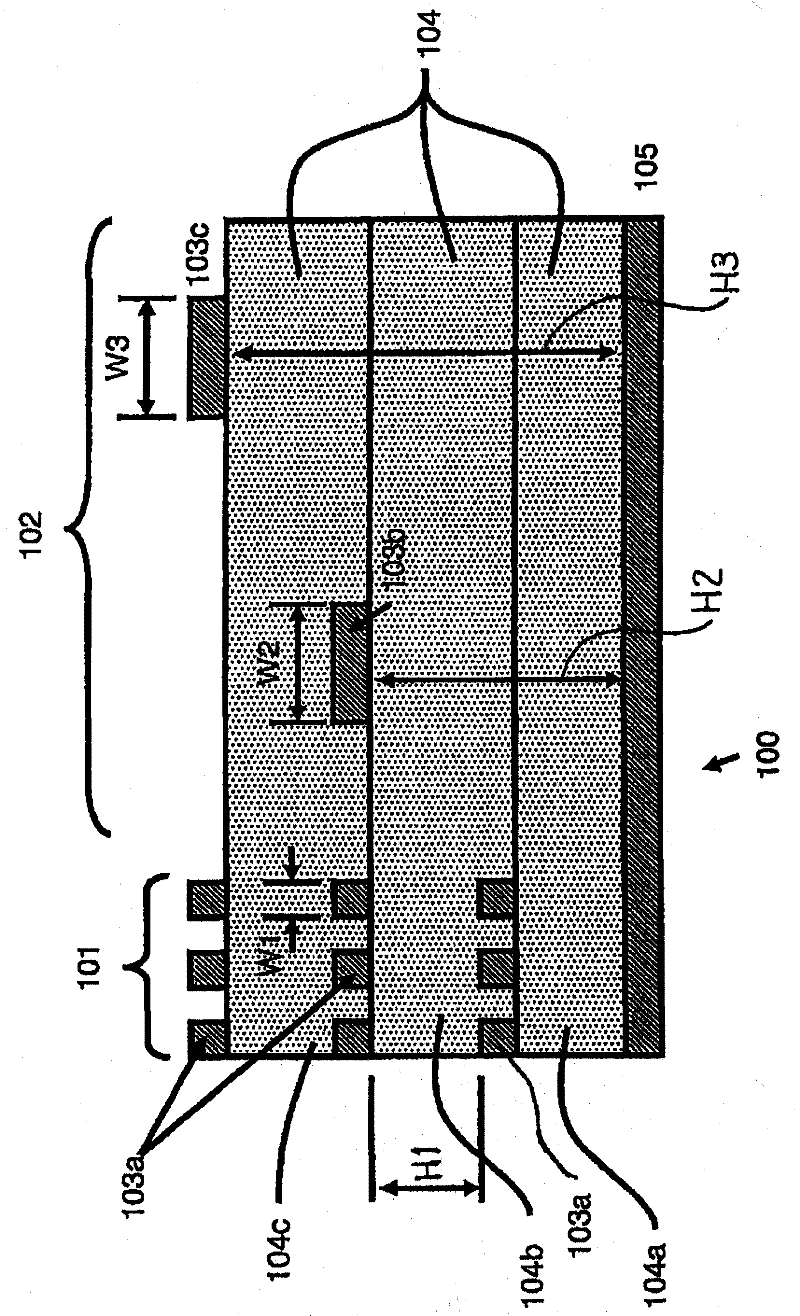

[0057] Below, refer to image 3 A second embodiment will be described.

[0058] Such as image 3 As shown, in the second embodiment, in figure 1 The insulating layer 104c is formed on the uppermost wirings 103a and 103b, and the wiring 103a is formed in the first wiring region 101 on the insulating layer 104c, but the wiring 103b is not formed in the second wiring region 102. The wiring 103c is formed in the second part of the first part. In the second portion of the second wiring region 102, no wiring layer is formed on the insulating layer below the uppermost wiring 103c, and the thickness H3 of the insulating layer becomes more than three times the thickness H1 of the insulating layer. In addition, the width W3 of the wiring 103c is also preferably larger than the width W2 of the wiring 103b of the first portion. In the second embodiment, the second wiring region (multilayer wiring region) 102 has an insulating layer thickness H1 per one layer of the first wiring region...

no. 3 approach

[0062] refer to Figure 4 , to describe the third embodiment.

[0063] With the third embodiment, it is formed so that in the boundary region between the first wiring region 101 and the second wiring region 102, a via hole (via hole), that is, a hole penetrating the insulating layer in the longitudinal direction, is provided, and the conductive The structure is the same as that of the first embodiment except for filling the hole with a conductive body and connecting the wiring 106 to the ground electrode 105 via the conductive body. By arranging the via conductor connected to the ground electrode 105 and the wiring 106, electrical coupling between the signal of the wiring in the first wiring region 101 and the signal of the wiring in the second wiring region 102 can be suppressed, Noise to signals transmitted in the second wiring region 102 can be suppressed.

[0064] Although in Figure 4 Although the wiring 106 is connected to the conductive film 105 as the ground electro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More