Anti-single event effect static random access memory unit

An anti-single event effect, memory cell technology, applied in the field of static random access memory, can solve problems such as pulling down the voltage of the output terminal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

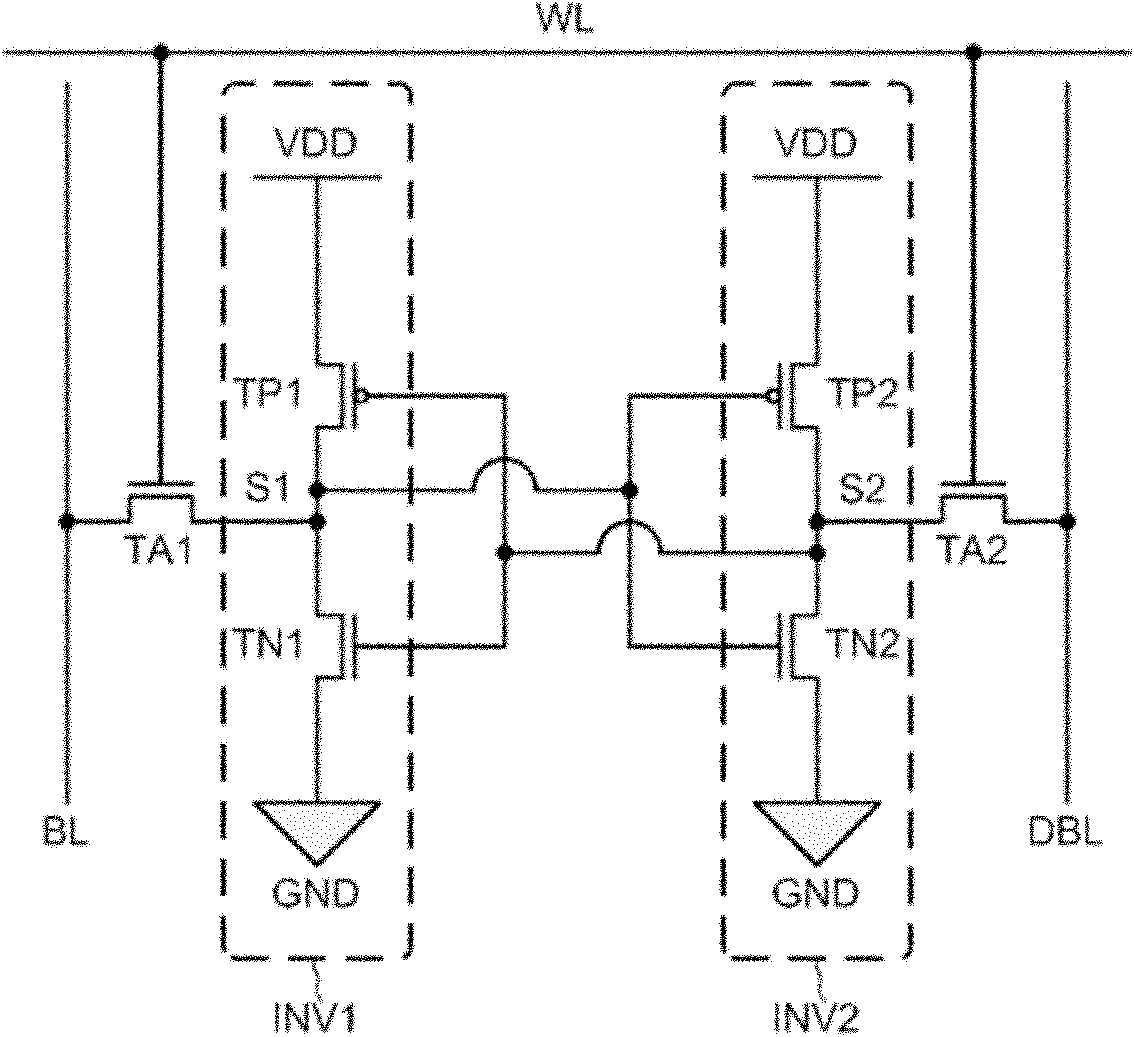

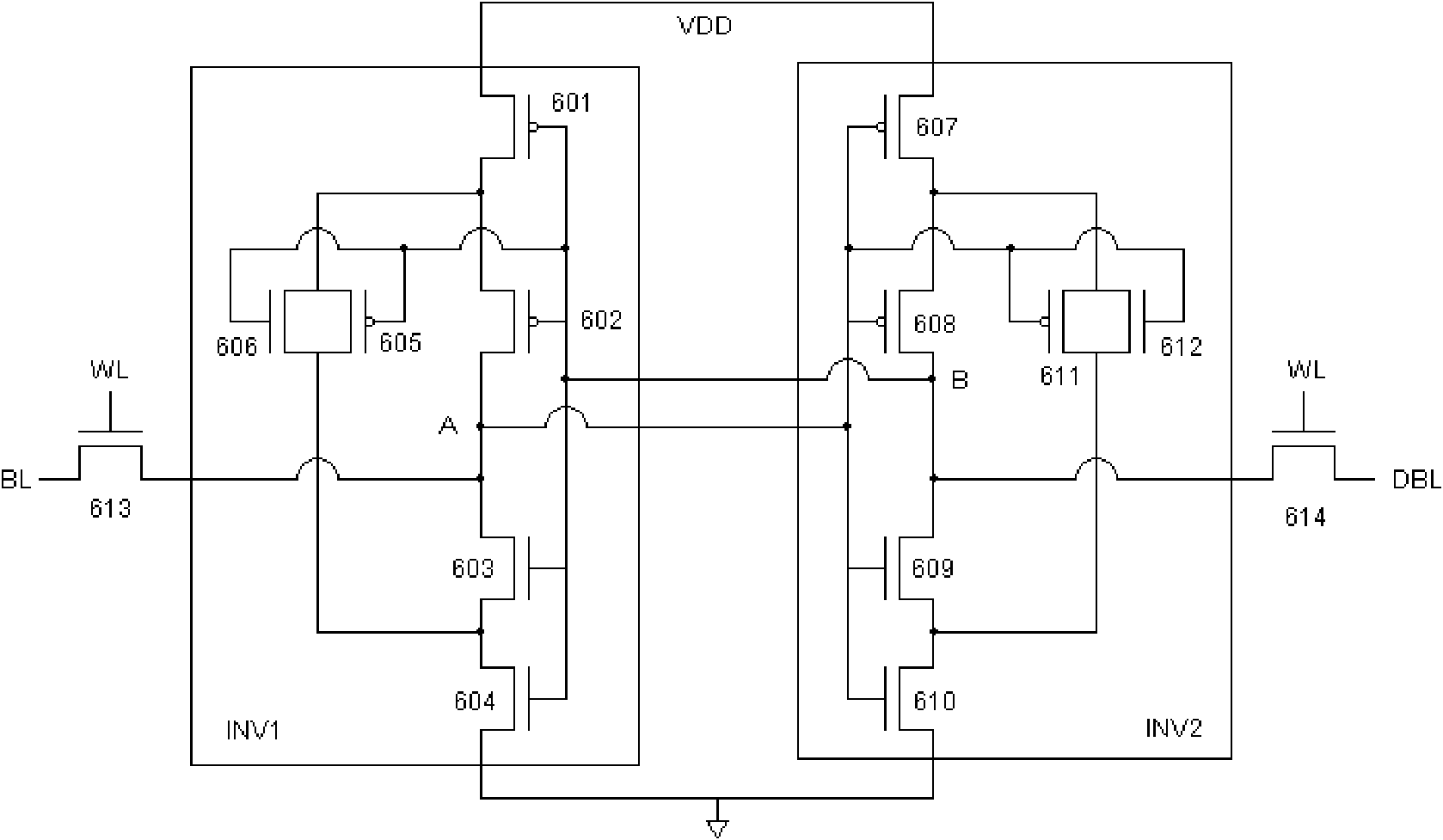

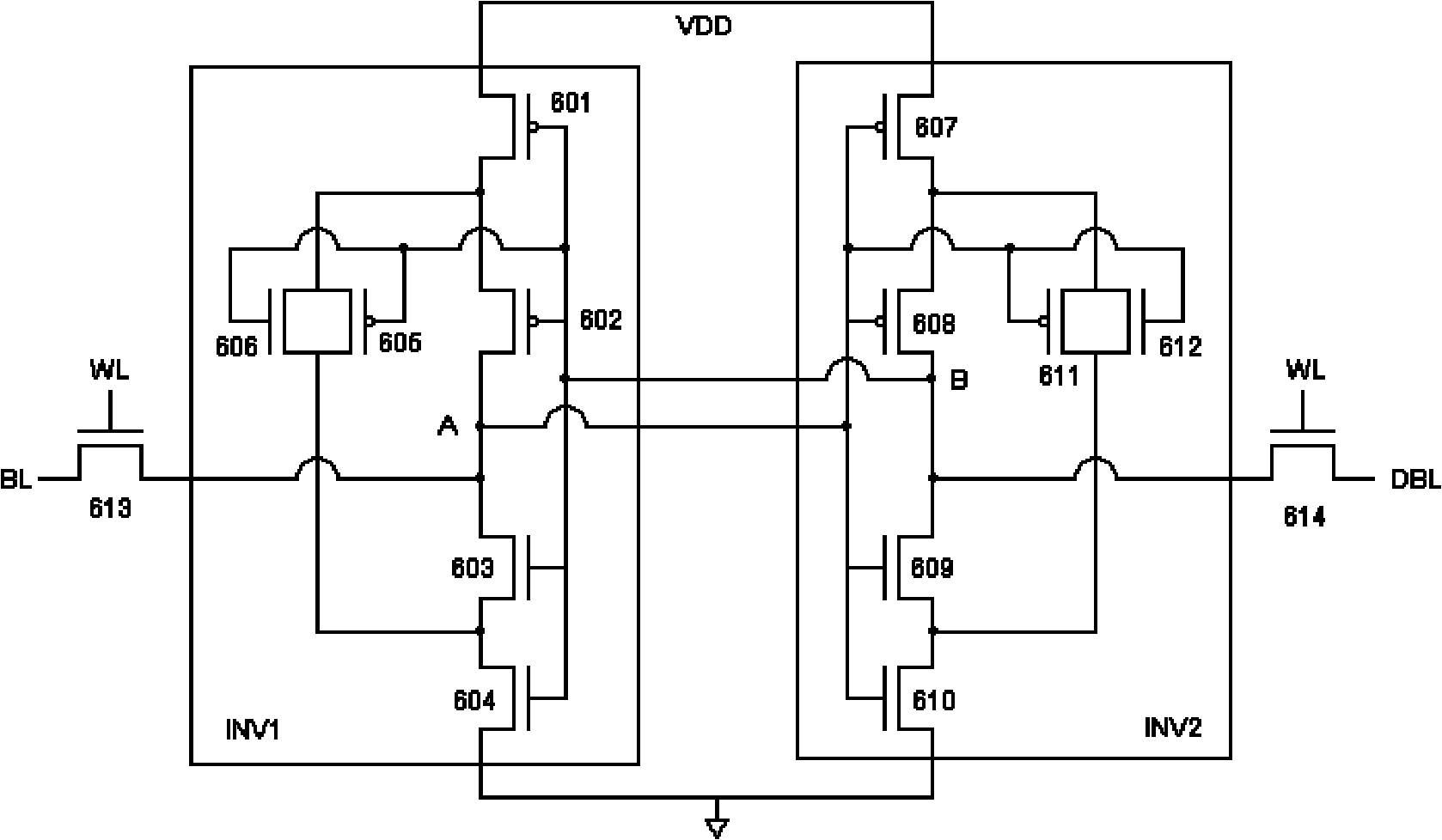

[0025] Such as figure 2 as shown, figure 2 It is the circuit diagram of the anti-single event flipping SRAM unit provided by the present invention, including the first inverter INV1, the second inverter INV2, the first NMOS transmission gate 613, and the second NMOS transmission gate 614, wherein: the first inverter The output terminal A of INV1 is connected to the first NMOS transmission gate 613, the output terminal B of the second inverter INV2 is connected to the second NMOS transmission gate 614, and the gate of the first NMOS transmission gate 613 and the gate of the second NMOS transmission gate 614 are connected to WL , the first NMOS transmission gate 613 corresponds to the unit output BL, the second NMOS tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More