Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems affecting junction depth, impurity concentration changes, device performance degradation, etc., to improve quality, avoid excessive losses, and benefit the process integrated effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

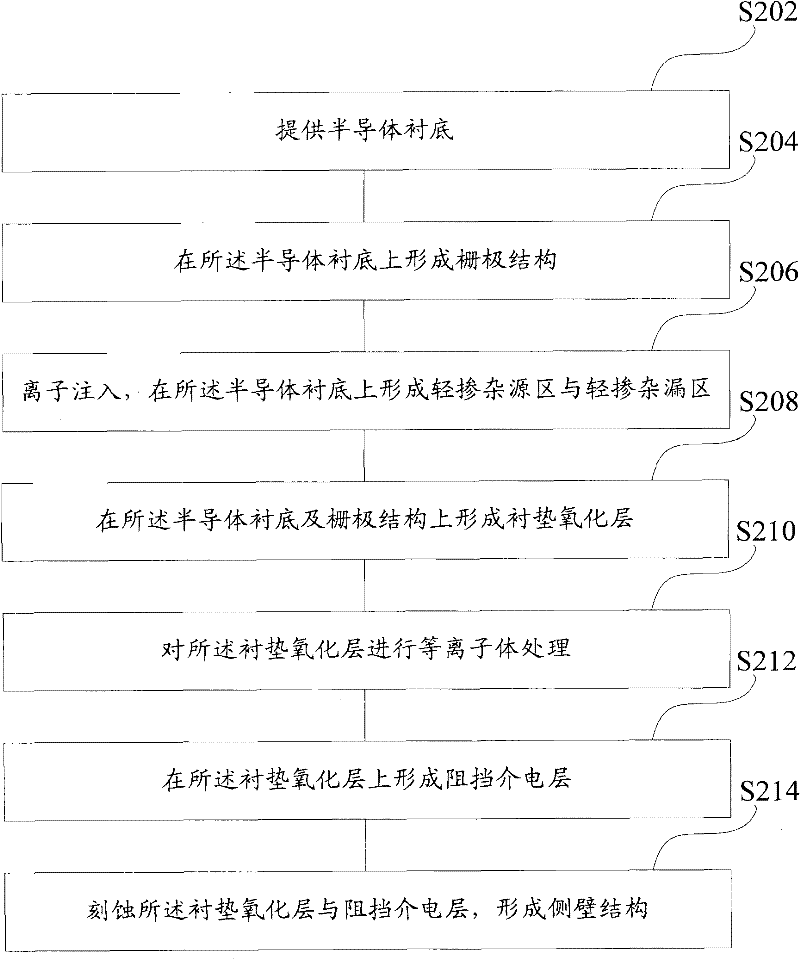

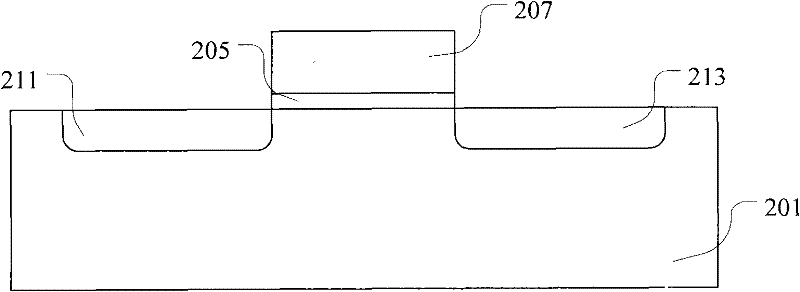

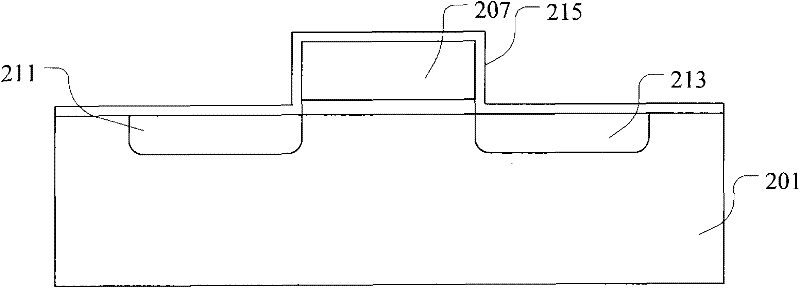

[0025] In the prior art, in the manufacturing process of PMOS transistors and flash memory transistor sidewall structures, ozone and tetraethylsilane (TEOS) are usually used as reaction precursors, and sub-atmospheric pressure chemical vapor deposition is used to form pad oxidation. Floor. Due to the lower reaction temperature of the sub-atmospheric pressure chemical vapor deposition, the content of hydrogen atoms in the pad oxide layer is much higher than that of silicon oxide formed by high temperature and low pressure chemical vapor deposition (LPCVD). The existence of the hydrogen atoms will not only affect the density of the pad oxide layer, but also generate defects (interfacial trap charges) at the silicon-silicon oxide interface, making the quality of the pad oxide layer poor and reducing the pad oxidation. Layer insulation performance. At the same time, for semiconductor devices such as PMOS transistors and flash memory transistors, lightly doped source regions and l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More