Structure and method for testing integrity of grid oxide layer and dielectric layer

A technology for testing structures and gate oxide layers, applied in the direction of semiconductor/solid-state device testing/measurement, electrical components, electric solid-state devices, etc., can solve the problem of short circuit of pads 103 and 104, short circuit of connection pads, and defects in metal interconnection layer 110 and other problems to achieve the effect of improving test accuracy and eliminating interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

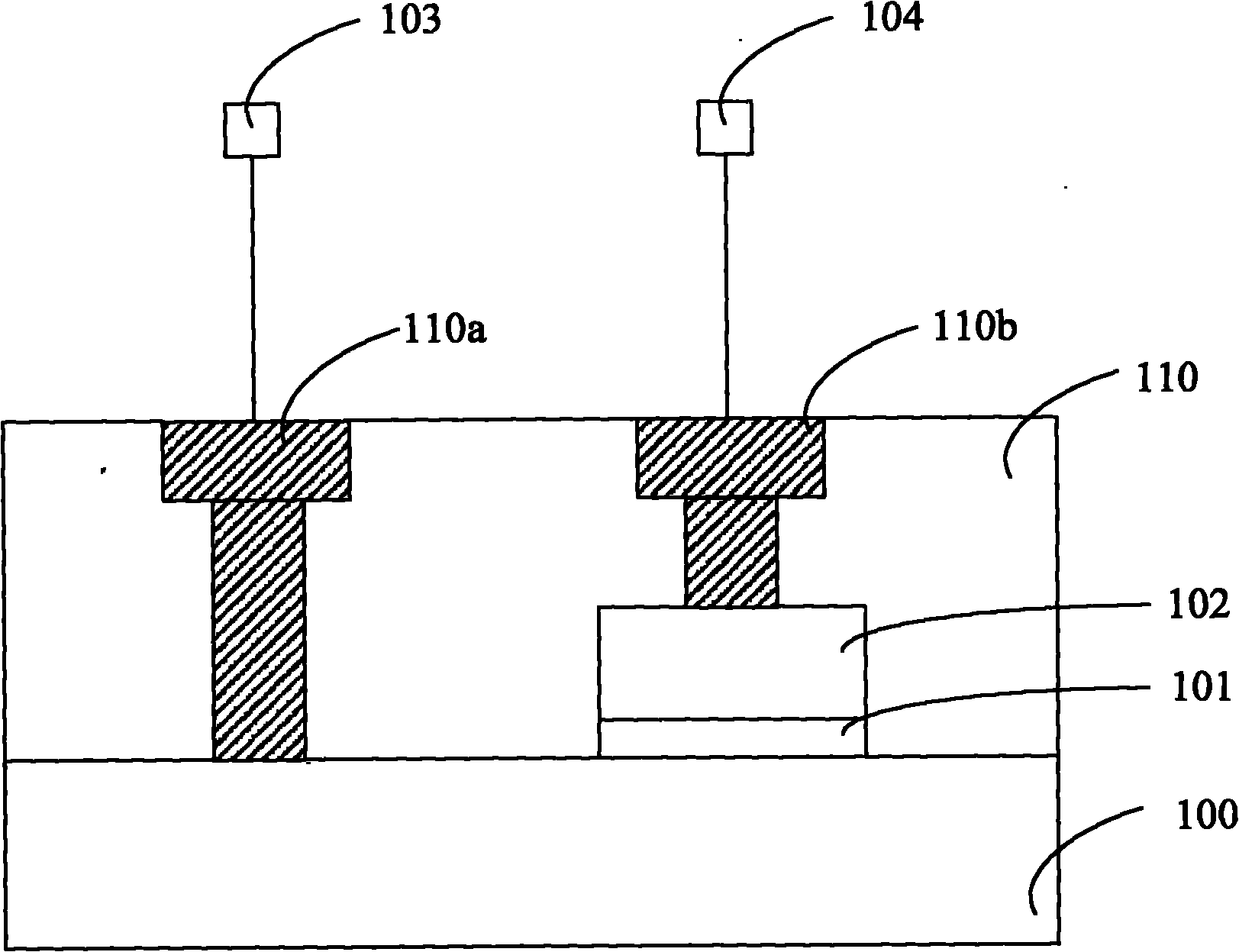

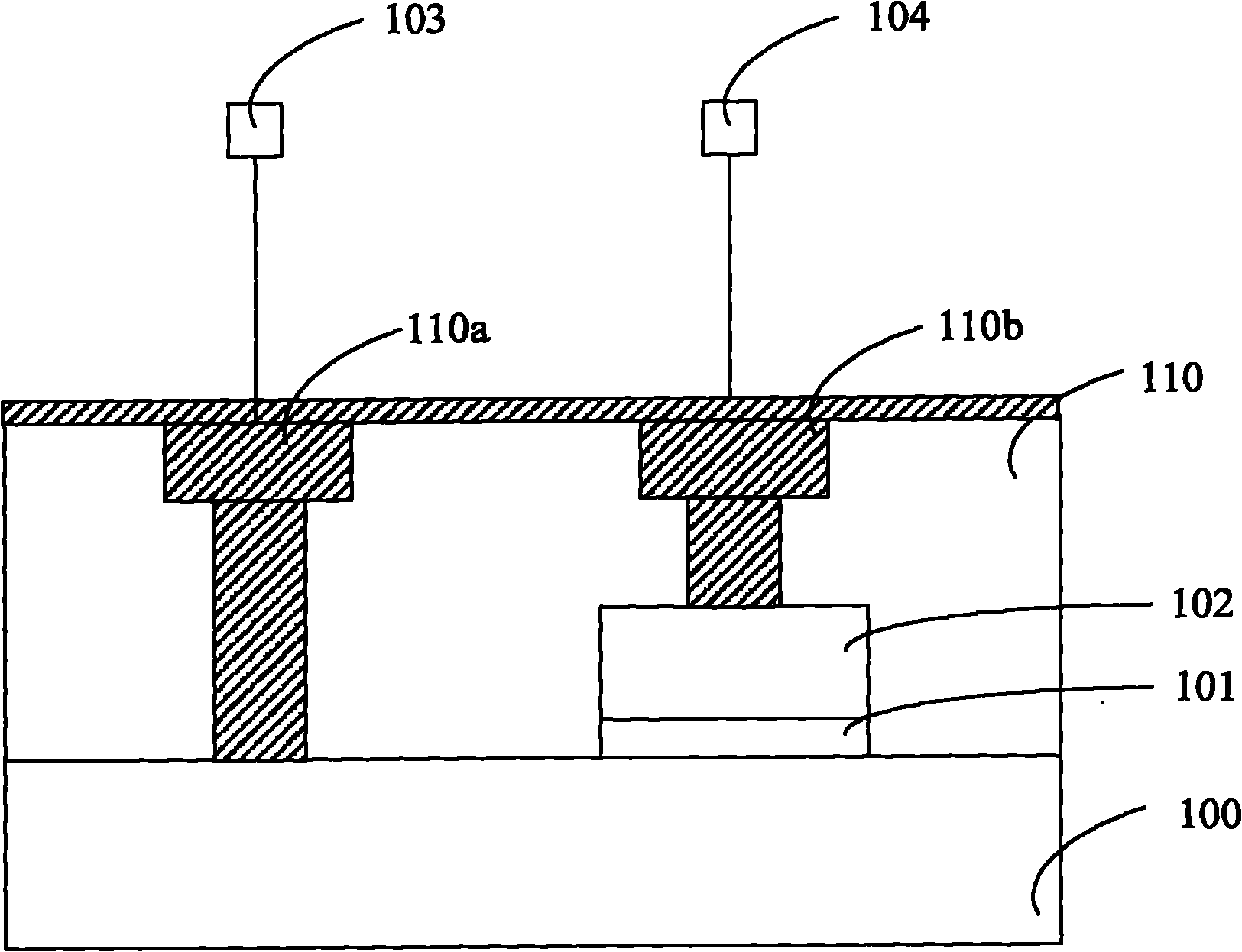

[0031] In actual production, such as image 3As shown, the pads 103 and 104 of the test structure are indirectly connected to the gate electrode 102 of the MOS transistor and the substrate 100 through the connection pads 110a and 110b in the metal interconnection layer. The forming process of the connection pads 110a and 110b mainly includes: forming an opening in the dielectric layer; filling the opening with metal to form a plug and a connection pad on the plug; during the filling process, part of the metal overflows the opening Covering the surface of the dielectric layer; grinding and removing the metal covering the surface of the dielectric layer by chemical mechanical polishing (CMP) to complete the formation process of the metal interconnection layer. During chemical mechanical polishing, if there is residual metal covering the surface of the dielectric layer after polishing, such as image 3 As shown, bridging defects between the connection pads in the metal interconn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More