Time-delay circuit

A delay circuit and circuit technology, applied in the direction of electrical components, pulse processing, single output arrangement, etc., can solve the problems of large deviation and low delay accuracy, and achieve the effect of improving yield and accurate delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

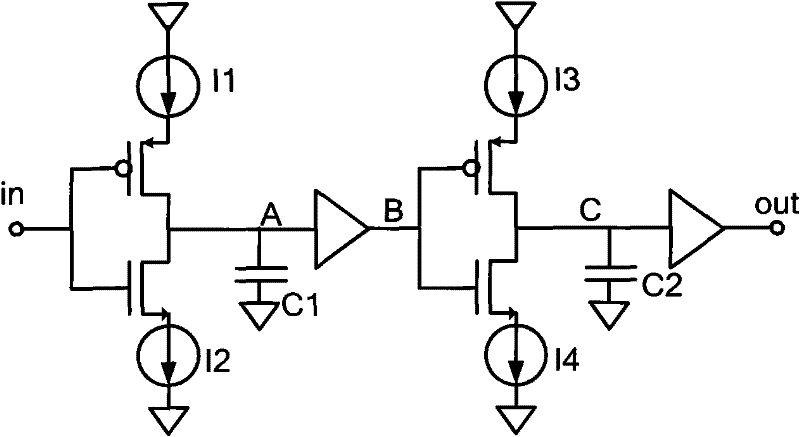

[0017] An embodiment of the delay circuit of the present invention is as image 3 As shown, it includes a first PMOS transistor M1 of a P-type transistor, a second NMOS transistor M2 of an N-type transistor, a third PMOS transistor M3 of a P-type transistor, a fourth NMOS transistor M4 of an N-type transistor, a first buffer, a second buffer, The first capacitor C1, the second capacitor C2, the first current source circuit, the second current source circuit, the third current source circuit, and the fourth current source circuit;

[0018] The gates of the first PMOS transistor M1 and the second NMOS transistor M2 are short-circuited for connecting to the input signal terminal in, the drain of the first PMOS transistor M1 is short-circuited with the source of the second NMOS transistor M2 and connected to the first buffer The input terminal A of the device M1 and one end of the first capacitor C1, the source of the first PMOS transistor M1 is connected to the power supply volta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More