Array substrate, manufacturing method thereof and liquid crystal display

A technology of an array substrate and a manufacturing method, which is applied in the field of liquid crystal display, can solve the problems of reduced public voltage signal load, large delay of RC signal, affecting picture quality, etc., so as to reduce the delay of RC signal, reduce resistance, and improve picture quality. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

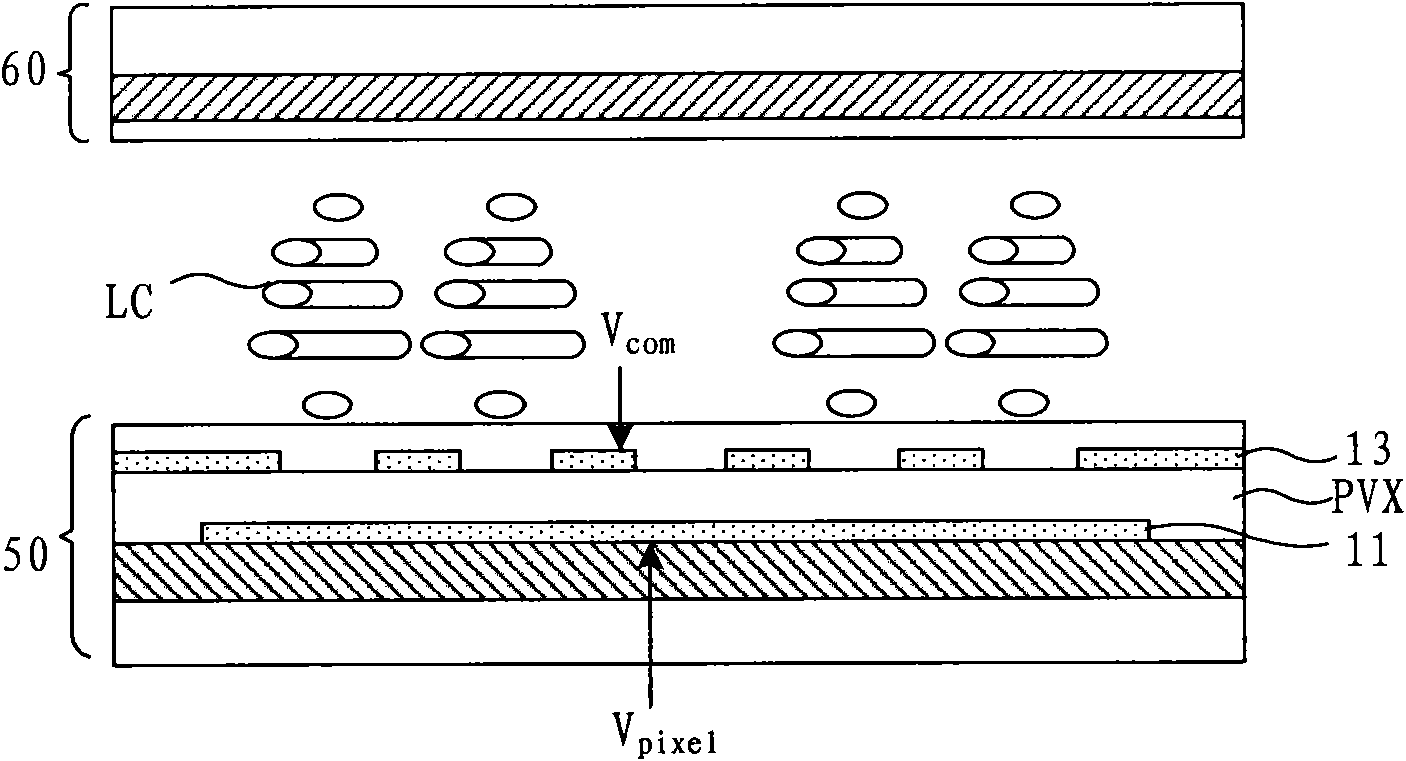

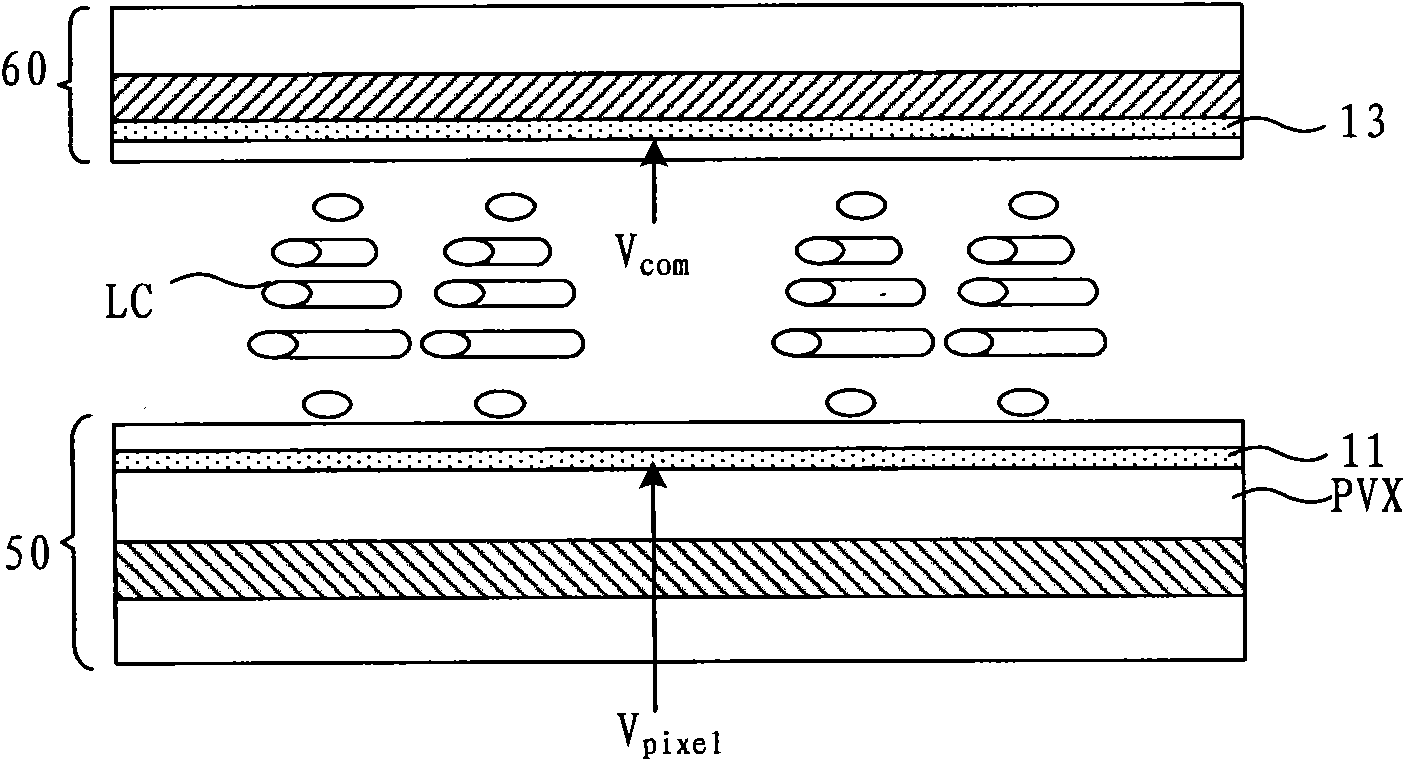

[0054] Figure 5 A schematic structural diagram of the array substrate provided in Embodiment 1 of the present invention, as shown in Figure 5 As shown, the array substrate includes a base substrate 1, and the pixel area 30 of the base substrate 1 is formed with data lines and gate lines that cross horizontally and vertically to form a plurality of pixel units, and each pixel unit includes a switching element, a pixel The electrode and the common electrode 13 , the common electrode 13 is an integral pattern with slits arranged in the pixel area, wherein: the common electrode line 12 is also formed in the pixel area 30 , and the common electrode line 12 communicates with the common electrode 13 .

[0055] In the array substrate of the liquid crystal display of HFFS or HAD-SDS mode, the common electrode line 12 can be formed in the pixel area 30, wherein, the common electrode line 12 and the common electrode 13 can be connected through contact via holes, and can also be directl...

Embodiment 2

[0058] The array substrate provided by Embodiment 2 of the present invention includes a base substrate 1, and the pixel area 30 of the base substrate 1 is formed with data lines and gate lines that cross horizontally and vertically to form a plurality of pixel units, and each pixel unit includes a switch Elements, pixel electrodes and common electrodes 13, the common electrodes 13 are integral patterns with slits arranged in the pixel area 30, wherein: the common electrode lines 12 are also formed in the pixel area 30, the common electrode lines 12 and the common electrodes 13 connected, see Figure 5 .

[0059] Further, the position of the common electrode line formed in the pixel region 30 may include the following methods:

[0060] Method 1: The common electrode line 12 and the data line 5 are arranged on the same layer and parallel to each other, and the common electrode line 12 communicates with the common electrode 13 through the contact via hole 15, such as Figure 6A...

Embodiment 3

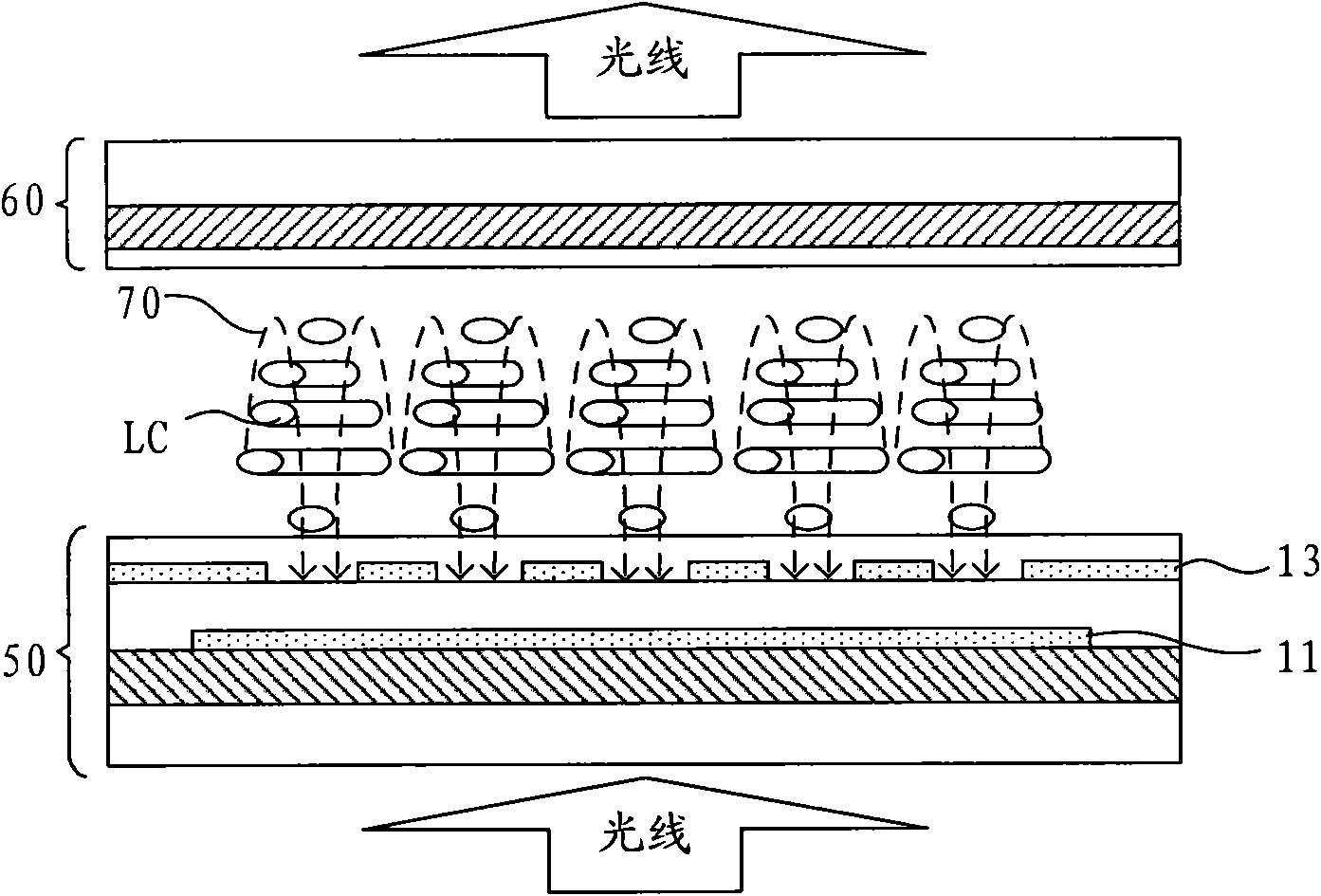

[0079] Figure 7A A flow chart of the method for manufacturing an array substrate provided in Embodiment 3 of the present invention, as shown in Figure 7A As shown, in the manufacturing method of the array substrate, the process of forming gate lines, switching elements, data lines, pixel electrodes, common electrodes and common electrode lines in the pixel area of the base substrate includes:

[0080] Step 101 , forming a pattern including a gate line and a gate electrode on a base substrate through a patterning process.

[0081] Figure 7B It is a schematic diagram of a partial top view structure of the substrate on which gate lines and gate electrodes are formed in the method for manufacturing an array substrate provided in Embodiment 3 of the present invention, Figure 7C for Figure 7B The schematic diagram of the side view section structure along the A-A line, such as Figure 7B and Figure 7C As shown, a gate metal film is deposited on a base substrate 1, a phot...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More