SOI (Silicon On Insulator) type P-LDMOS (Lateral Diffused Metal-Oxide Semiconductor)

A P-LDMOS, semiconductor technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of limiting the vertical breakdown voltage of SOI type P-LDMOS, difficulty in forming dielectric isolation regions, and difficulty in process implementation, etc. High-voltage application range, the effect of increasing the longitudinal breakdown voltage, and improving the withstand voltage capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

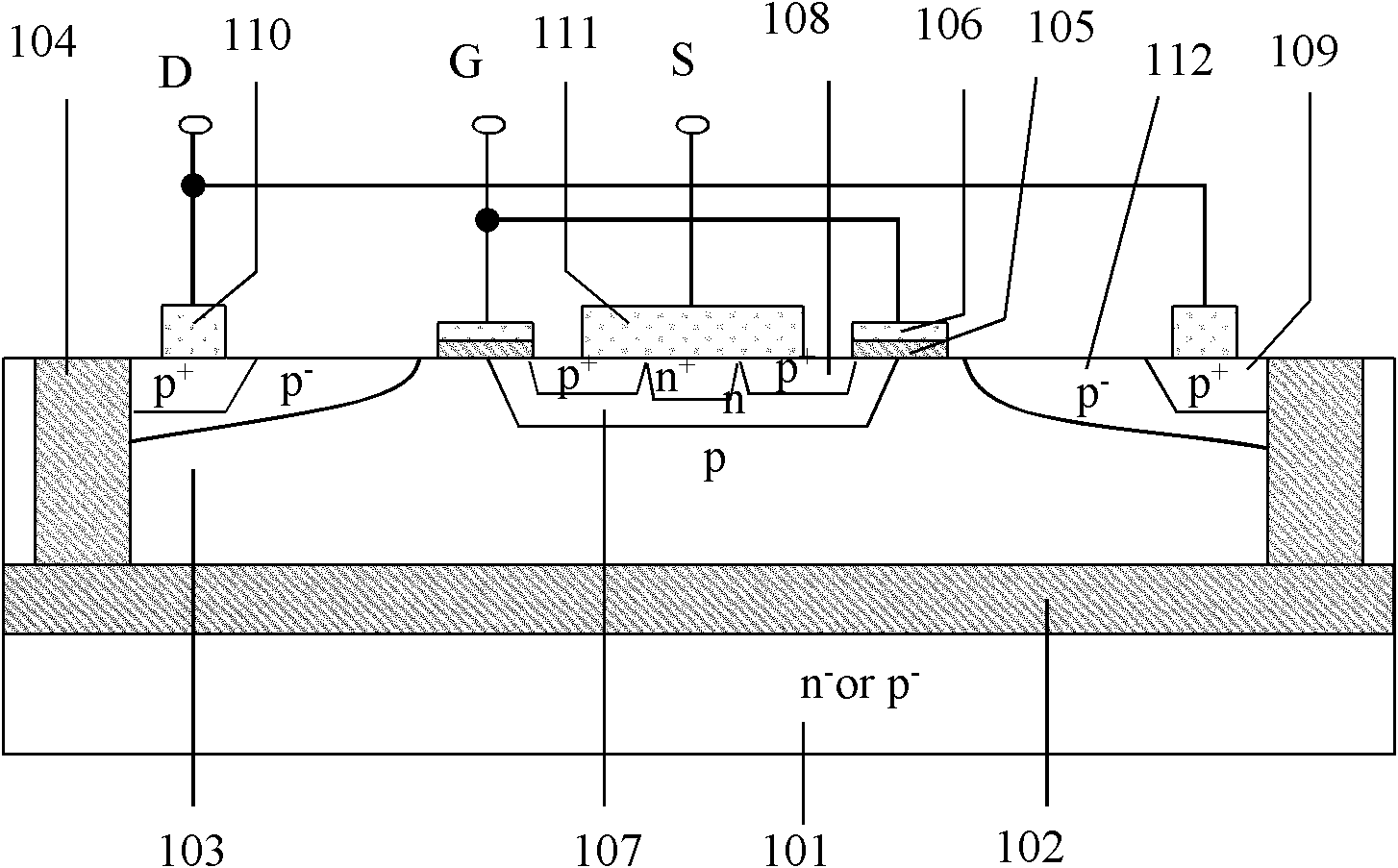

[0069] This embodiment provides an SOI type P-LDMOS, such as Figure 4 As shown, it is a schematic diagram of a local structure of the device, including: a semiconductor substrate layer 101, a dielectric buried layer 102, a semiconductor active layer 103, and a dielectric isolation region 104. The two dielectric isolation regions define the active region of the device. A gate oxide layer 105, a gate electrode 106 on the gate oxide layer 105, an n well 107 in the active region, a p well in the n well 107 + source region 108, p + The drain region 109 is formed on the drain region and the drain electrode 110 is formed on the p + The source electrode 111 on the source region 108 .

[0070] The semiconductor active layer 103 has a plurality of n + The doped region 113 is located on the semiconductor active layer 103 side of the interface between the dielectric buried layer 102 and the semiconductor active layer 103 .

[0071] At the same time, one difference between the P-LDMOS...

Embodiment 2

[0082] In order to solve the self-heating effect of SOI type P-LDMOS, this embodiment provides another structure of SOI type P-LDMOS, such as Figure 9 Shown is a schematic diagram of the local structure of the device.

[0083] The SOI type P-LDMOS includes: a semiconductor substrate layer 101, a dielectric buried layer 102, a semiconductor active layer 103 and n + Doped region 113, n + The doped region 113 is located on the semiconductor active layer 103 side of the interface between the buried dielectric layer 102 and the semiconductor active layer 103 , and a silicon window 114 for heat dissipation may also be provided in the buried dielectric layer 102 .

[0084] Specifically, one or more silicon windows 114 may be provided in the dielectric buried layer 102, and the distribution range of each silicon window may be equal or different.

[0085] This embodiment focuses on the differences from the SOI-type P-LDMOS provided in Embodiment 1, and the similarities can be referr...

Embodiment 3

[0087] Such as Figure 10 Shown is a schematic diagram of a partial structure of the SOI type P-LDMOS provided in this embodiment.

[0088] The SOI type P-LDMOS includes: a semiconductor substrate layer 101, a dielectric buried layer 102, a semiconductor active layer 103 and an n+ doped region 113, and the n+ doped region 113 is located at the interface between the dielectric buried layer 102 and the semiconductor active layer 103 one side of the semiconductor active layer 103;

[0089] the n + A dielectric groove 115 is arranged in the space between the doped regions 113, and the material of the dielectric groove 115 is SiO 2 , Low dielectric constant material or variable dielectric constant material.

[0090] Such as Figure 11 As shown in , it is a schematic diagram of another partial structure of the SOI type P-LDMOS provided in this embodiment.

[0091] The SOI type P-LDMOS includes: a semiconductor substrate layer 101, a dielectric buried layer 102, a semiconductor ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More