Semiconductor assembly, semiconductor device and manufacturing method

A semiconductor and component technology, applied in the field of lead-free solder layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

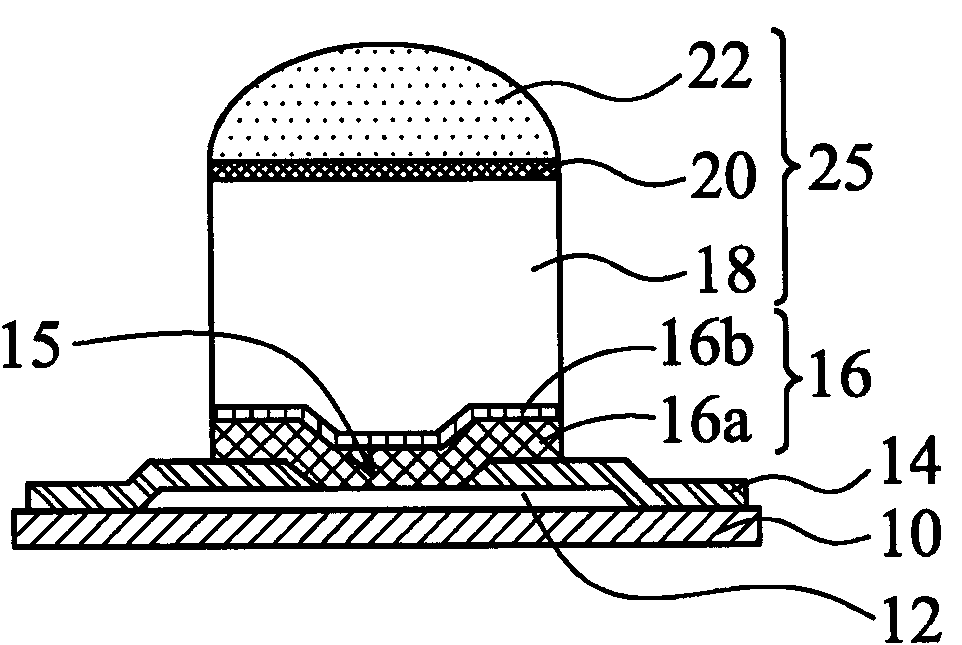

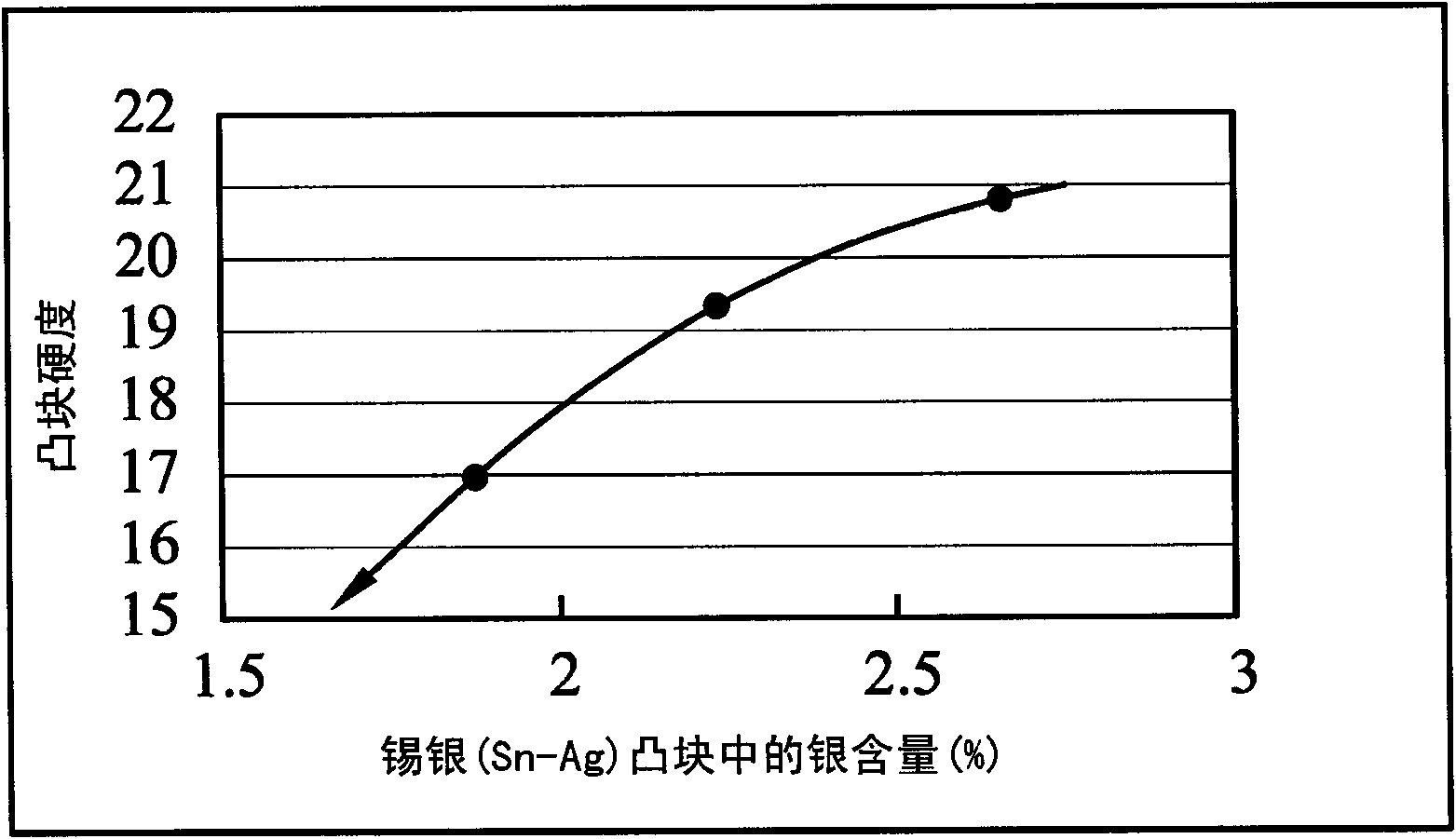

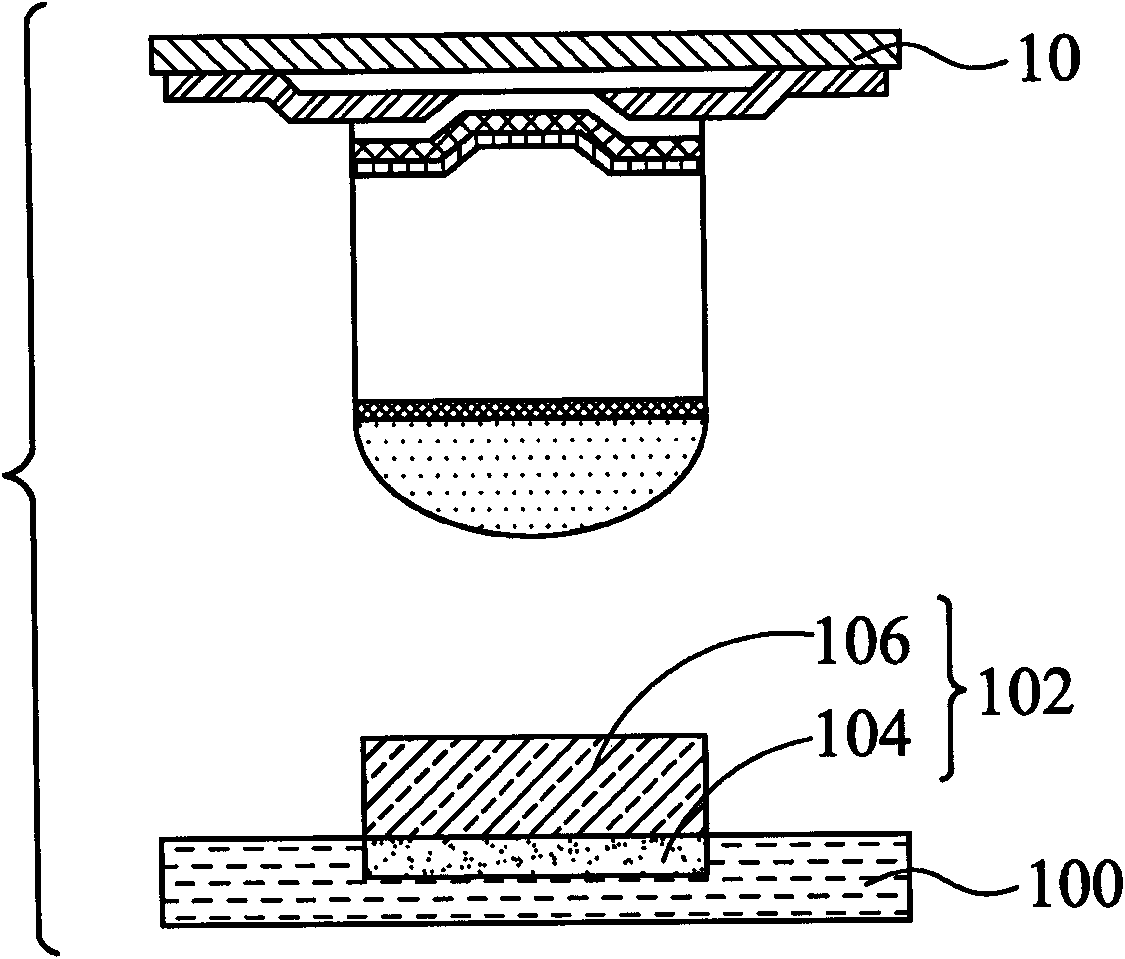

[0062] The present invention provides a lead-free solder (lead-free solder) with controlled silver content and reflow temperature, which is used for post passivation interconnects with copper post, post passivation interconnects and solder bumps , and / or semiconductor elements in which through-silicon vias (TSVs) are formed, and can be applied to flip-chip assembly (flip-chip assembly), wafer level chip scale packaging (wafer level chip scale packaging, WLCSP), three-dimensional integrated circuit stack (3D-IC stack), and / or advanced packaging technologies. In the ensuing description, specific details are set forth in order to fully understand the present invention. However, it will be understood by one of ordinary skill in the art that the present invention may be practiced without these specific details. In some embodiments, well-known structures and processes are not described in detail to avoid obscuring the present invention. "An embodiment" mentioned in the specificati...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| melting point | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More