Semiconductor structure for interconnection process and manufacturing method thereof

A device manufacturing method and semiconductor technology, applied in the field of interconnection, can solve problems such as unsatisfactory uniformity of sheet resistance, influence on electrical properties of interconnection structures, and difficulty in effective control, so as to improve electrical characteristics and reduce interaction or crosstalk , Reduce the effect of RC delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In the following description, numerous specific details are set forth in order to provide a more thorough understanding of the present invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without one or more of these details. In other instances, some technical features known in the art have not been described in order to avoid obscuring the present invention.

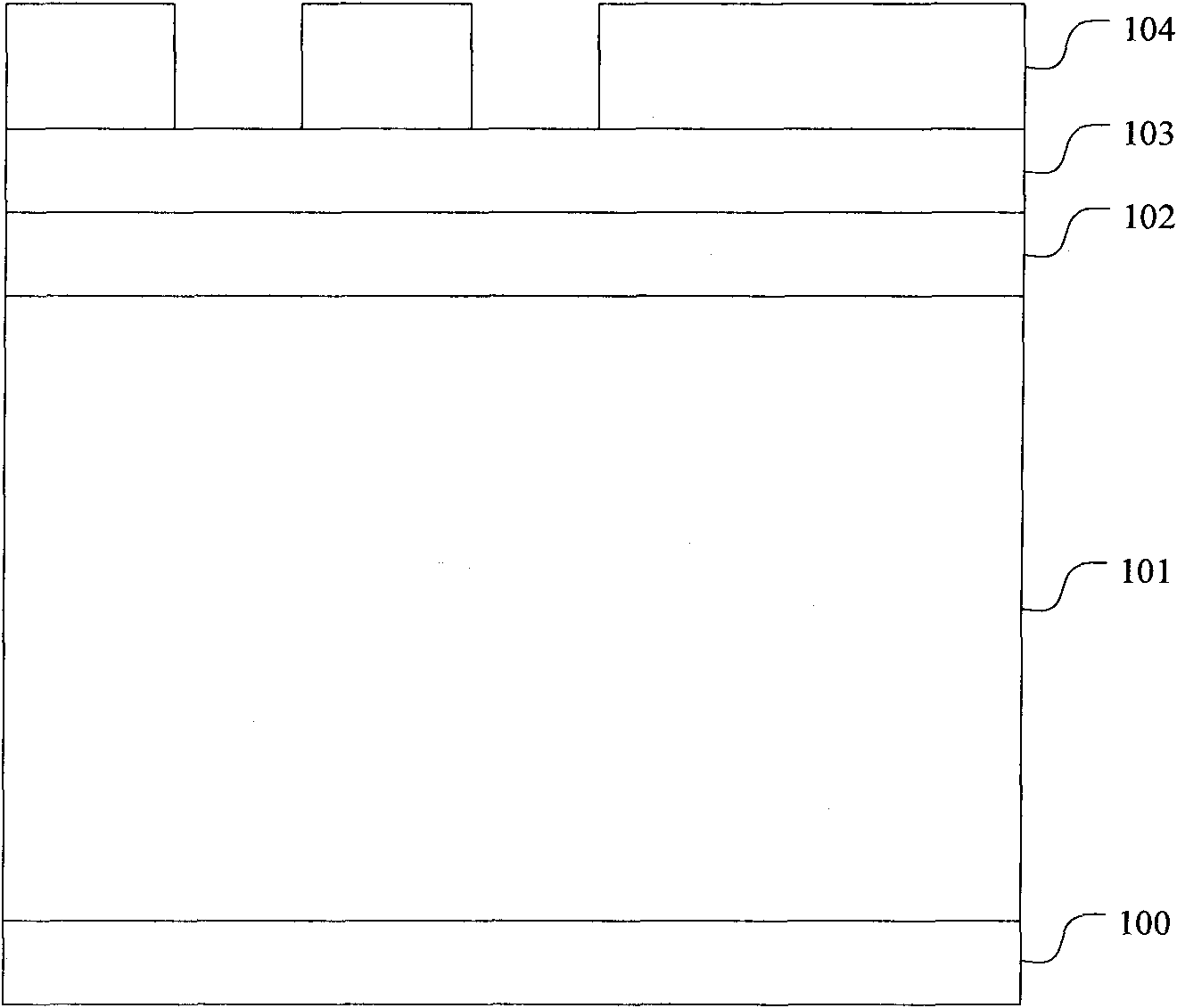

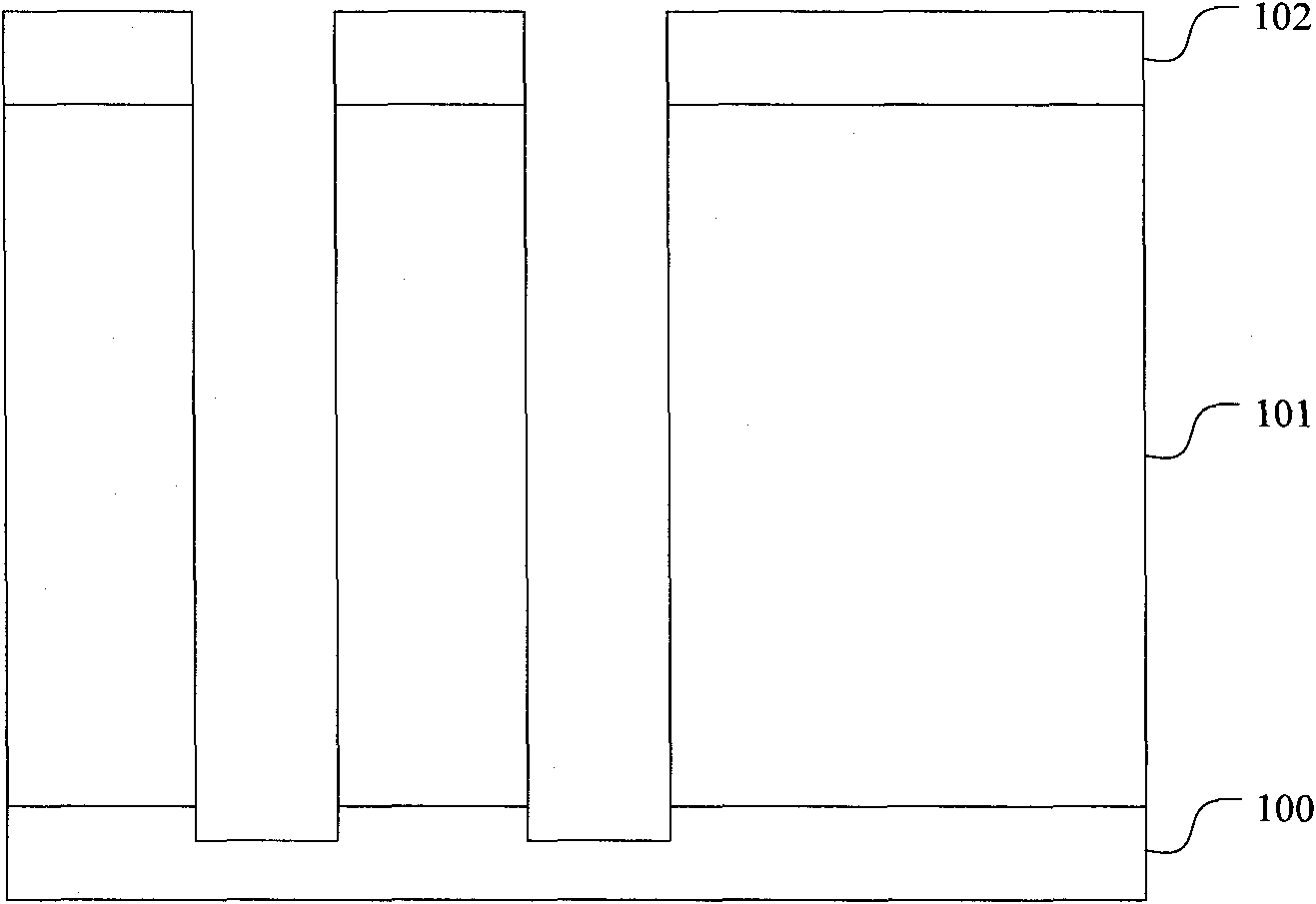

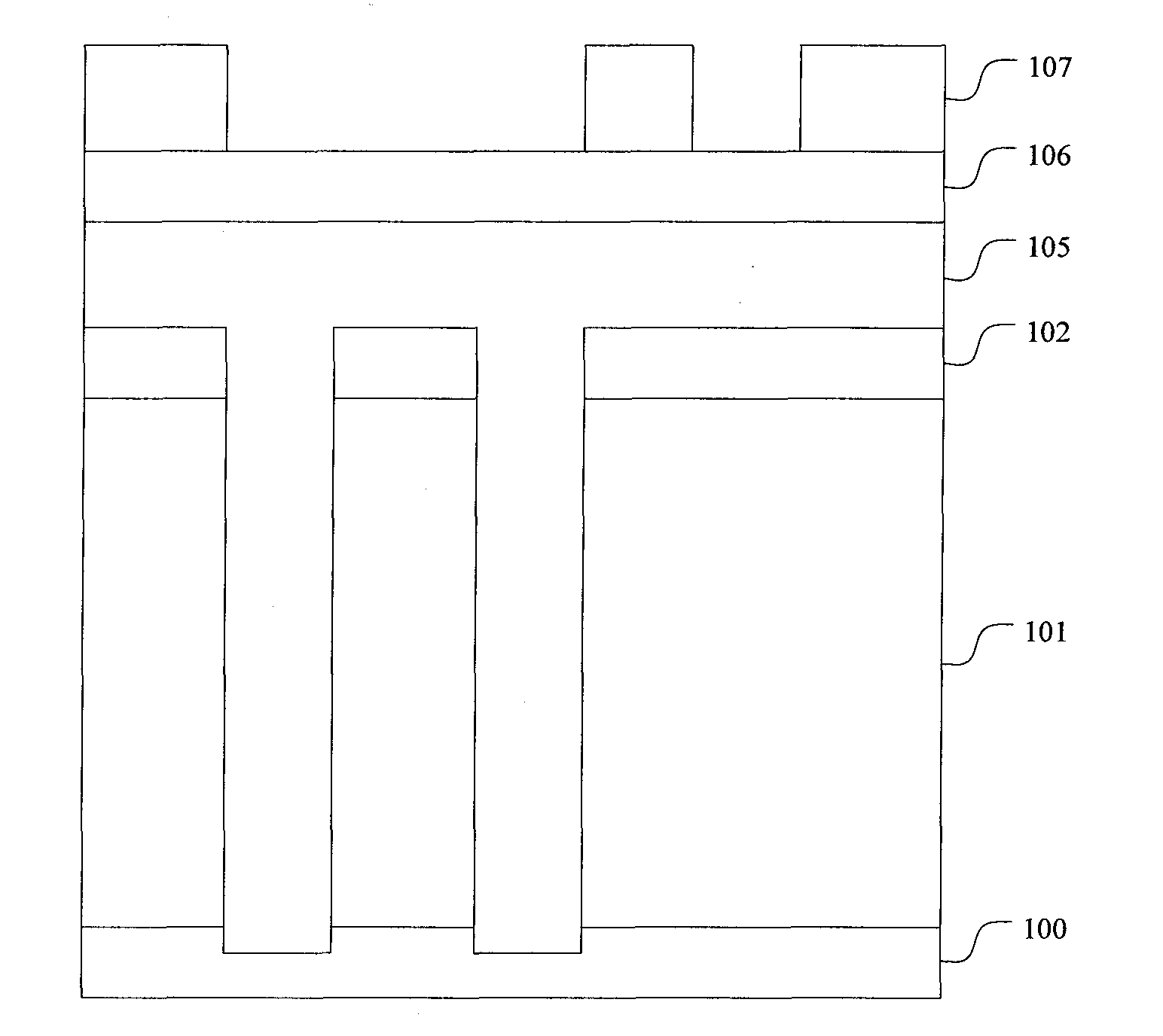

[0023] Figures 2A-2E A process of fabricating a copper interconnect layer with a double damascene structure using the method of the embodiment of the present invention is shown. like Figure 2A As shown, a nitrogen-doped carbide NDC layer 100 is deposited as a via stop layer on the previous interconnect layer or active device layer. In one example, NDC uses C 3 H 10 Si as its precursor.

[0024] After that, the first low-k dielectric layer 101a is covered on the NDC layer 100 by CVD, and the thickness may be between 1000 angstroms and 2000 angstroms. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More