Multilayer on-chip integrated spiral inductor with vertical structure

An integrated spiral and vertical structure technology, applied in the direction of inductors, fixed inductors, fixed signal inductors, etc., can solve the problems of obvious substrate loss and occupying a large chip area, so as to save chip area, reduce area, reduce The effect of induced current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

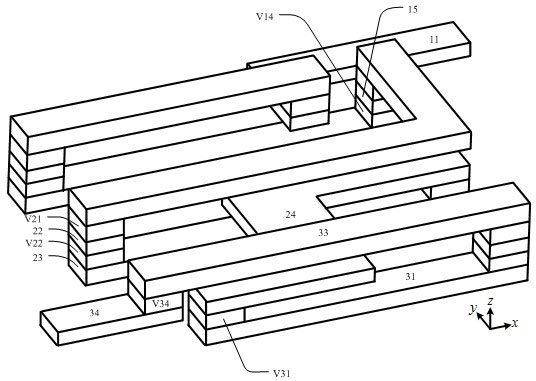

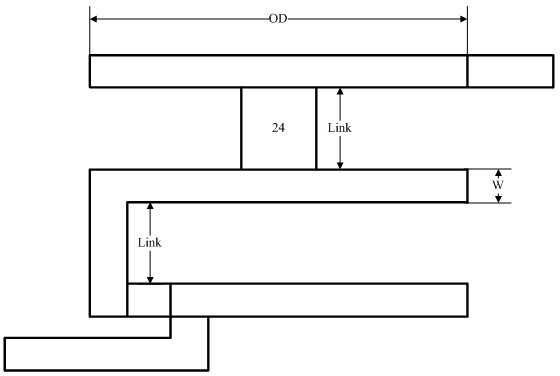

[0022] Figure 4 It is a simulation diagram of the inductance L-frequency relationship of an embodiment of the present invention. In general, the value range of the inductor line width is 4 um~14 um. In order to obtain ideal properties of the inductor, such as image 3 As shown, in this embodiment, the line width of the outer diameter of the inductor is W=8 um, OD=140 um, the length of each through hole along the x direction is also 8 um, and the distance between the inductor coils of each layer perpendicular to the horizontal plane Link=3 um, the dot curve indicates the inductance value of port 1, the triangle curve indicates the inductance value of port 2, and the low frequency inductance value can reach about 1 nH. The area required for a planar spiral inductor to achieve this inductance using the same process is about 12600 um 2 , and the area used by the inductor of the present invention is about 3380 um 2 . At the same time, the self-resonant frequency of the structu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More