Low-power-consumption LDPC (low density parity check) decoder based on optimization of folding structure of memorizer

A memory and decoder technology, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc. Large proportion, complex LDPC decoder structure and other problems, to achieve the effect of reducing read and write power consumption, reducing the number of read and write operations, good applicability and portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

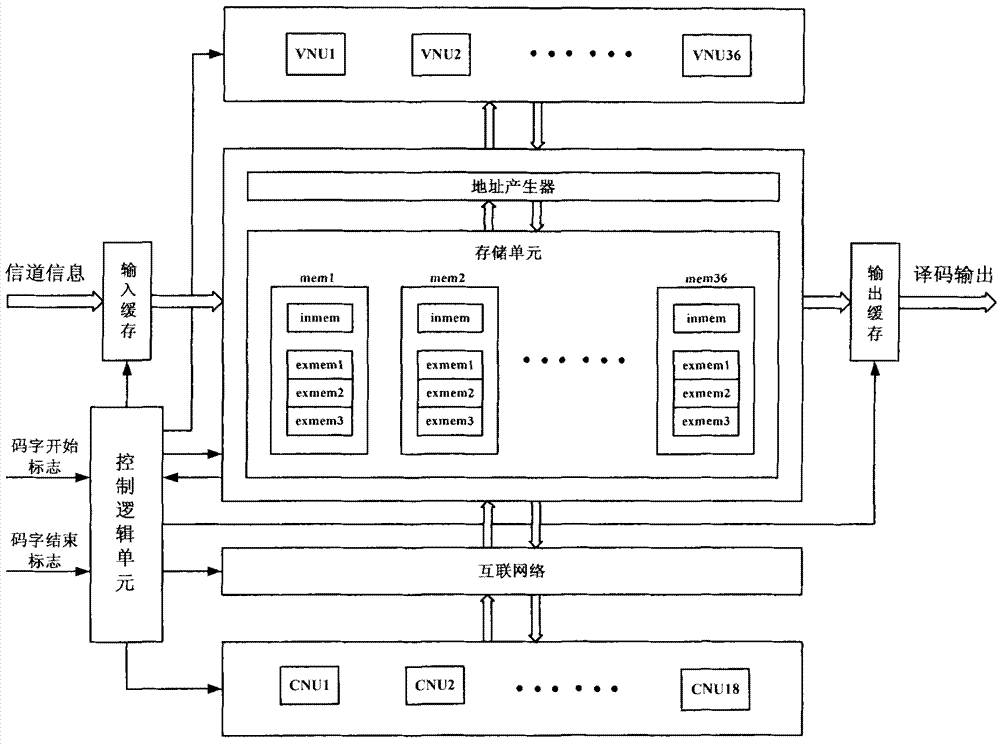

[0043] figure 1 is a schematic structural diagram of a low-power LDPC decoder according to an embodiment of the present invention. The schematic diagram is based on the 1 / 2 code rate LDPC decoder of the CMMB protocol proposed by the State Administration of Radio, Film and Television of China. The check matrix has a row weight of 6 and a column weight of 3. ), variable node operation unit (VNU), storage unit, control unit and interconnection network. Wherein, the input data enters the storage unit through the input buffer; during the iterative decoding period, the check node operation unit, the variable node operation unit and the storage unit transmit information through the interconnection network; When, the decoding r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More