Wafer level packaging structure and packaging method

A wafer-level packaging and wafer technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve problems such as poor product reliability, wafer-level packaging open circuit, etc. High consistency and good thickness uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

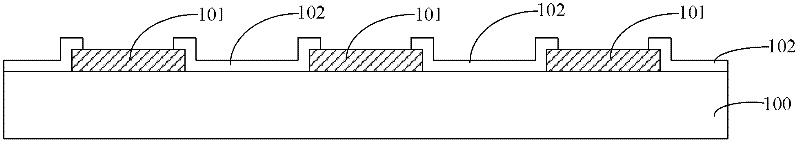

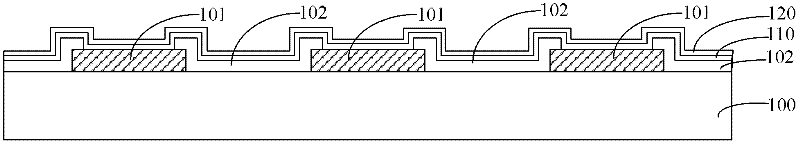

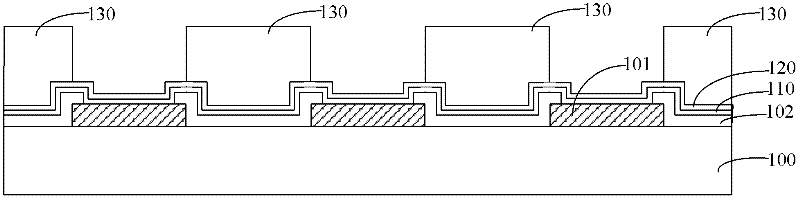

[0031] After a lot of experiments, the inventors of the present invention found that the open circuit phenomenon in the wafer-level packaging of the existing technology is caused by the following reasons: the distance between the chip pads is getting narrower, and the copper metal pillar 131 has a certain Height, so that the opening of the photoresist pattern is small, the aspect ratio of the copper metal column 131 to be formed is large, and bubbles are prone to appear during the electroplating process, resulting in an open circuit in the subsequent packaging process; and the inventor of the present invention also in the experiment It is found that the lower reliability of products packaged by the existing wafer-level packaging process is due to: the electroplating process is used in the existing packaging process, and the surface of the copper metal pillar 131 after electroplating is not flat, so that the solder layer 132 is not in contact with the non-flat surface. The flat ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More