Super-junction semiconductor device with groove-type terminal structure

A terminal structure and semiconductor technology, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems such as forming methods, achieve the effects of reducing grinding time, reducing production costs, and improving filling efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

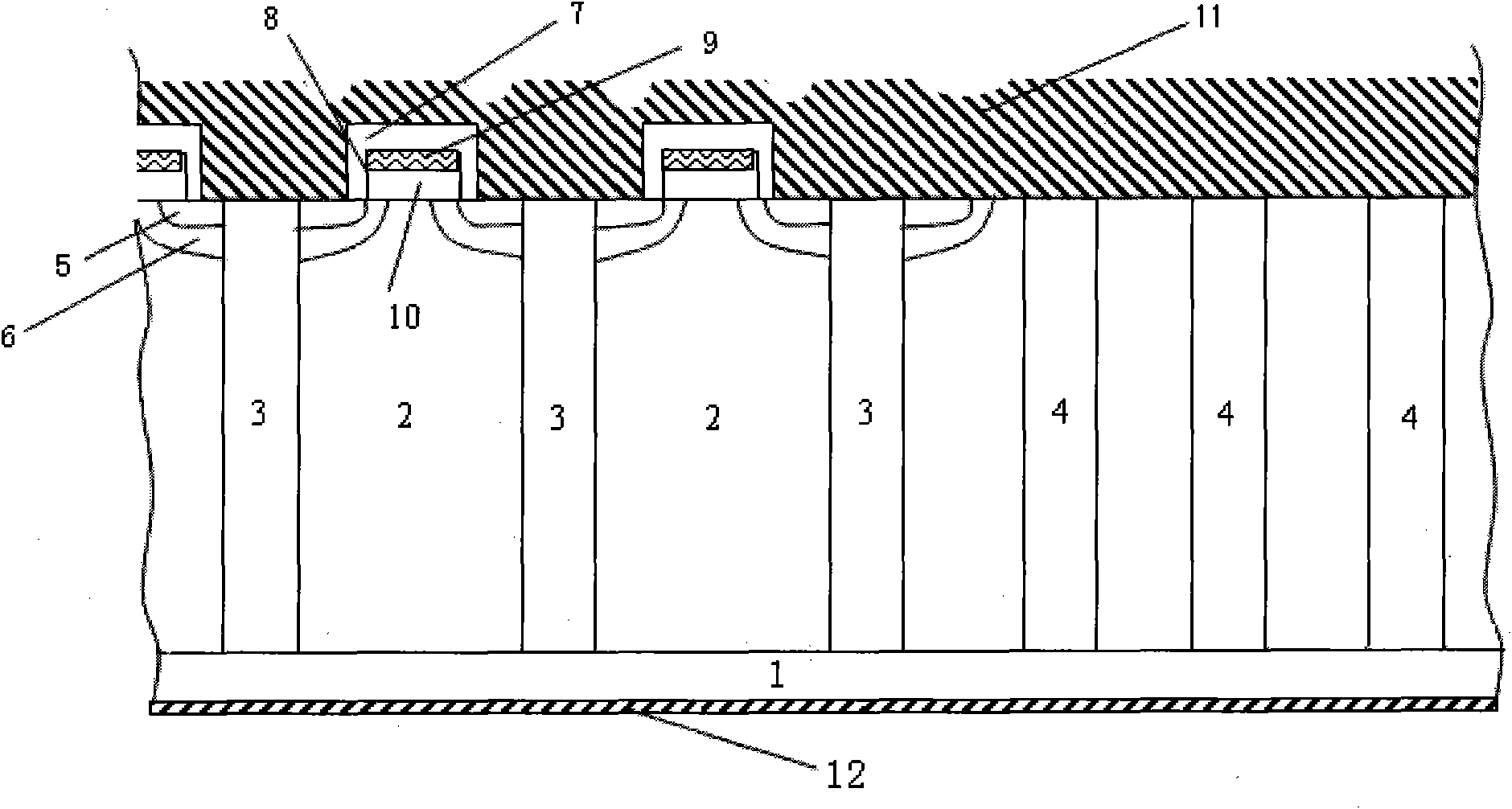

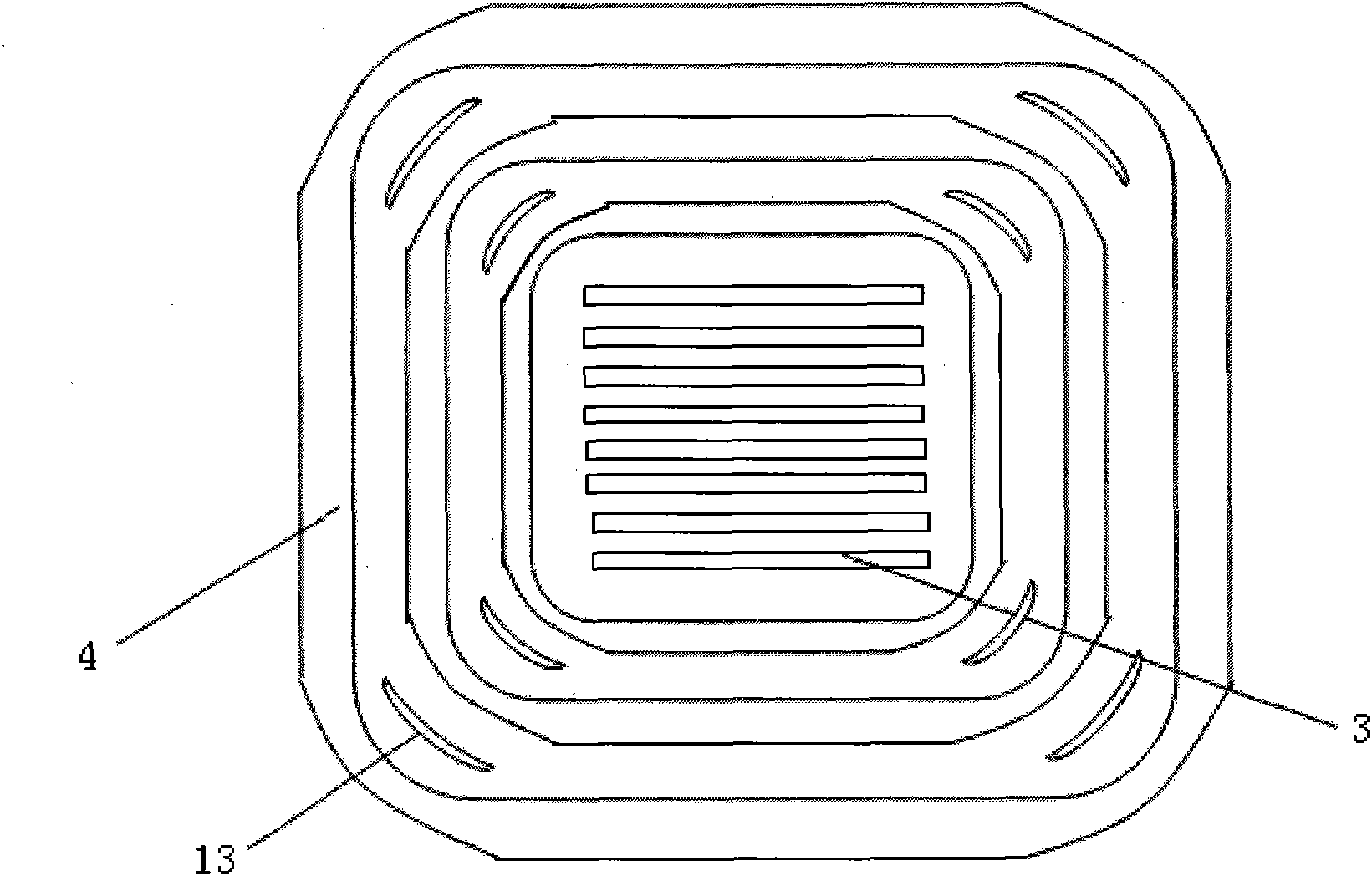

[0040] combine figure 1As shown, an N-type epitaxial layer (semiconductor region 2 ), such as a P-doped low-doped epitaxial layer with a thickness of 50 μm, is grown on a heavily doped silicon substrate (semiconductor substrate 1 ). Subsequently, a source region 5 and a base region 6 are formed on the N-type epitaxial layer. Growth of a deep trench etch stop (hard mask) or a CMP polish stop such as an oxide, nitride or oxynitride layer. The barrier layer can be a single layer or multilayer, such as first oxide+second oxide, or oxide+nitride, or oxide+nitride+oxide. Then define a deep trench etching area, that is, the first trench 3, the second trench 4, and the third trench 13, and perform deep trench etching. The crystal plane of the main sidewall of the trench is (100). For example, the width of the first trench 3 is 5 μm, the width of the second trench 4 is 5 μm at the straight side, the width at the corner is 4 μm, and the width of the second trench 4 is 1 μm. All three...

Embodiment 2

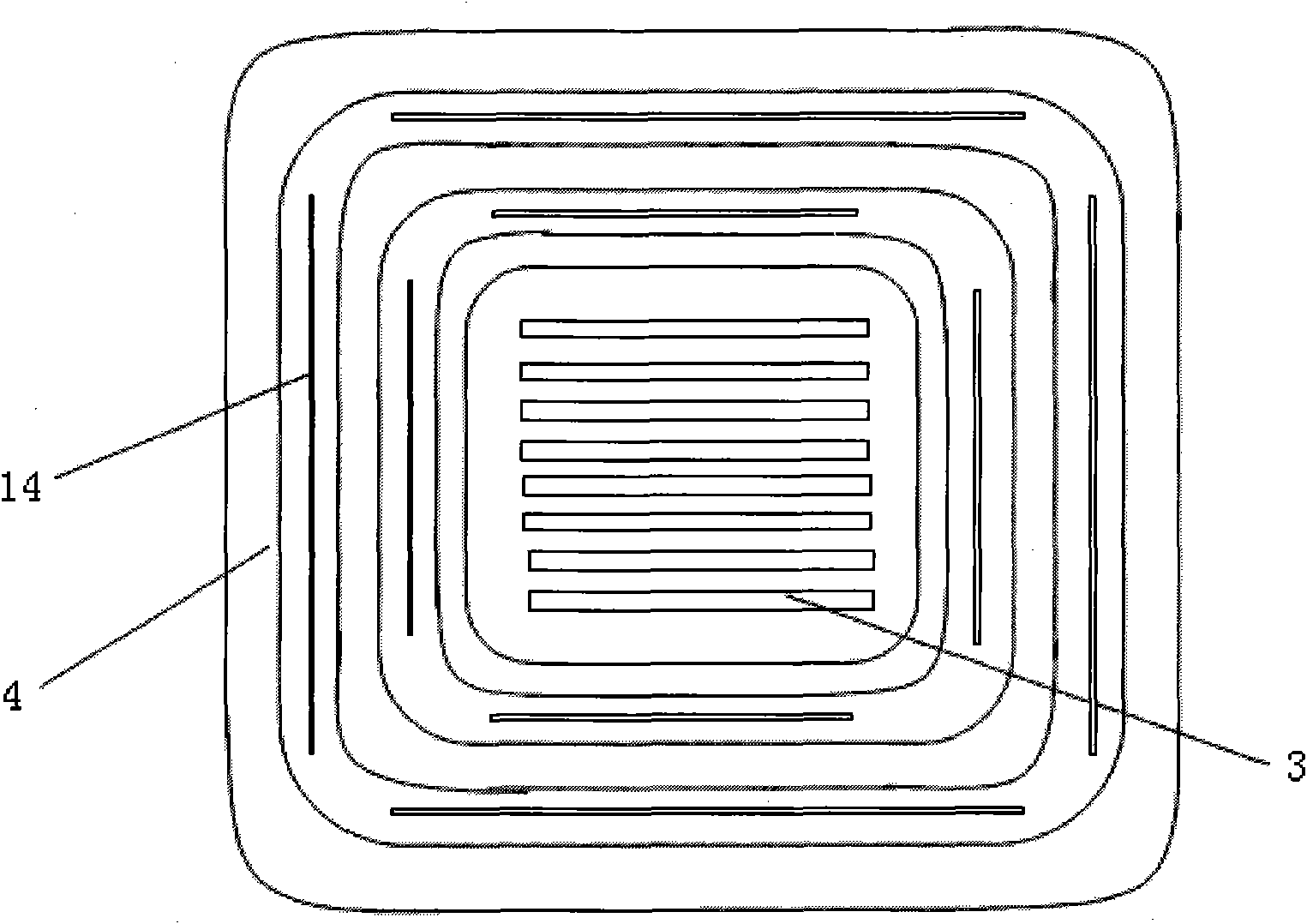

[0042] combine figure 1 As shown, an N-type epitaxial layer (semiconductor region 2 ), such as a P-doped low-doped epitaxial layer with a thickness of 50 μm, is grown on a heavily doped silicon substrate (semiconductor substrate 1 ). Subsequently, a source region 5 and a base region 6 are formed on the N-type epitaxial layer. A deep trench etch stop (hard mask) or CMP polish stop is then grown; such as oxide, nitride or oxynitride. The barrier layer can be a single layer or multilayer, such as first oxide+second oxide, or oxide+nitride, or oxide+nitride+oxide. Then define a deep trench etching area, that is, the area of the first trench 3 , the second trench 4 and the fourth trench 14 , and perform deep trench etching. The crystal plane of the main sidewall of the trench is (110). For example, the width of the first trench 3 is 4 μm, the width of the second trench 4 is 4 μm at the straight side, the width at the corner is 5 μm, and the width of the fourth trench 14 is 1 μm...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More