T type gate high electron mobility transistor (HEMT) device and manufacturing method thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as low breakdown voltage, achieve the effects of increased breakdown voltage, enhanced control capability, and reduced leakage voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

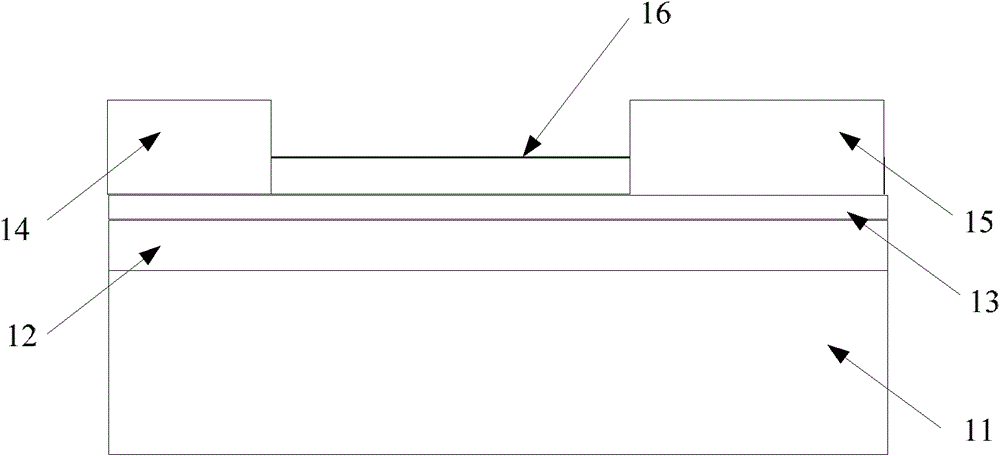

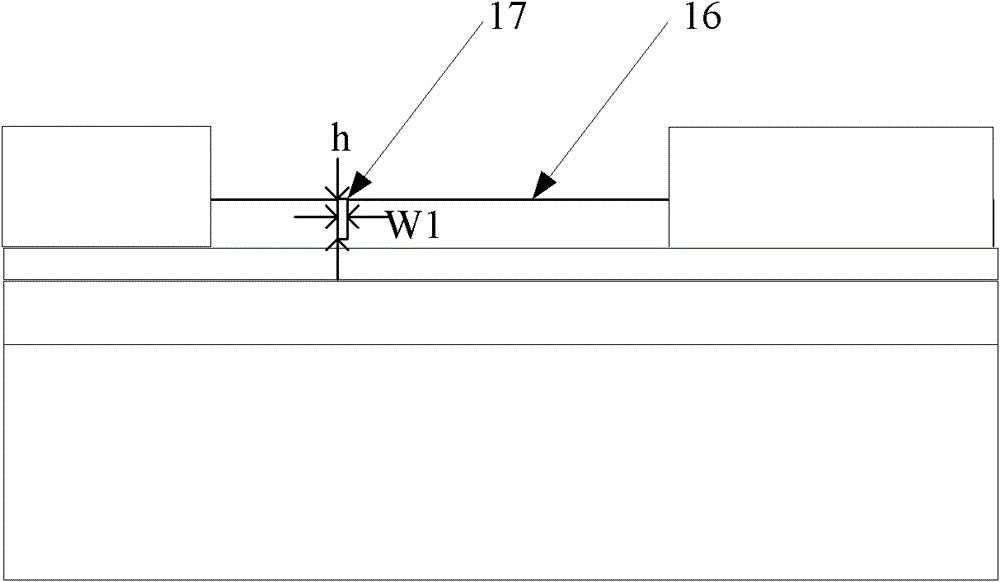

[0049] This embodiment discloses a method for manufacturing a T-shaped gate HEMT device, and the cross-sectional diagram of the device in each step is as follows Figure 2 to Figure 5 shown, including:

[0050] Step S1, providing a substrate.

[0051] Such as figure 2 As shown, the base includes:

[0052] A body layer 11, the body layer 11 is preferably a silicon carbide layer;

[0053] A buffer layer 12 disposed on the surface of the body layer 11, the buffer layer 12 is a gallium nitride layer;

[0054] An epitaxial layer 13 disposed on the surface of the buffer layer 12, the epitaxial layer 13 is selected from an aluminum gallium nitride layer;

[0055] The source electrode 14, the drain electrode 15 and the passivation layer 16 between the source electrode 14 and the drain electrode 15 are arranged on the surface of the epitaxial layer 13, and the passivation layer 16 is a silicon nitride layer.

[0056] Specifically, the bandgap width of the material for making the ...

Embodiment 2

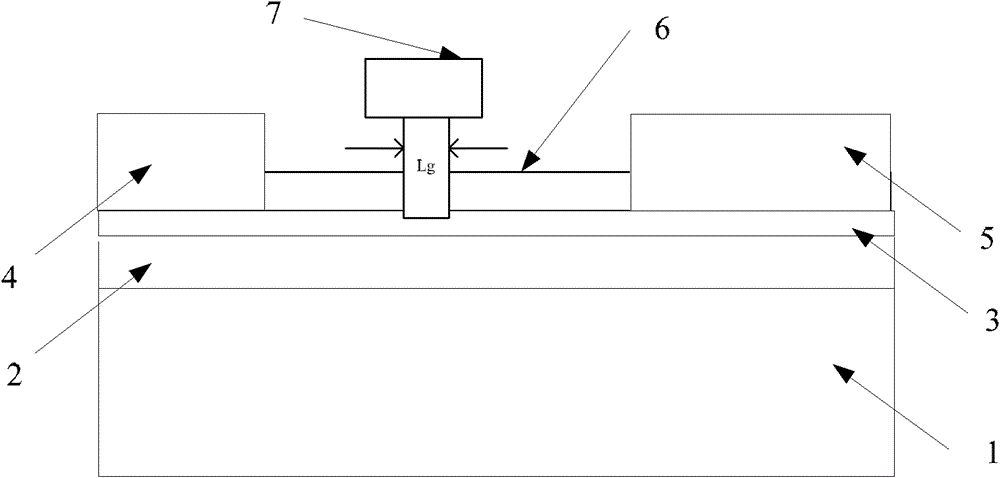

[0078] This embodiment discloses a T-gate HEMT device fabricated by the above embodiment, such as Figure 5 shown, the device includes:

[0079] The substrate, the substrate includes: a body layer 11, the body layer 11 is preferably a silicon carbide layer, a buffer layer 12 arranged on the surface of the body layer 11, the buffer layer 12 is a gallium nitride layer, and is arranged on the buffer layer The epitaxial layer 13 on the surface of the layer 12, the epitaxial layer 13 is selected as an aluminum gallium nitride layer, and the source 14, the drain 15 and the passivation between the source 14 and the drain 15 are arranged on the surface of the epitaxial layer 13. A layer 16, the passivation layer 16 is a silicon nitride layer;

[0080] T-shaped gate 21, the gate foot part of the T-shaped gate 21 penetrates the passivation layer 16 deep into the surface of the epitaxial layer 13, and the bottom of the gate foot is divided into two parts arranged in a ladder shape, Where...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More