Single Damascus method used for reducing square resistance of copper interconnection

A technology of sheet resistance and copper interconnection, which is applied in the manufacture of circuits, electrical components, semiconductor/solid-state devices, etc., can solve the shape and size of unfavorable etching process etching, reduce interconnect reliability, and increase sheet resistance, etc. problem, to achieve the effect of reducing chip interconnection sheet resistance, interconnection sheet resistance, and signal delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

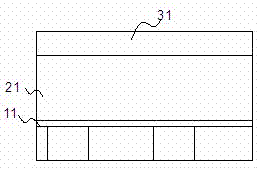

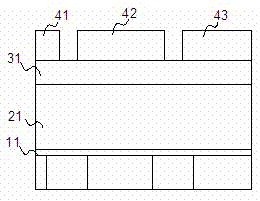

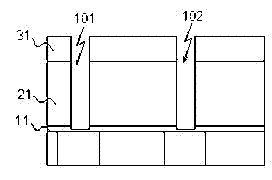

[0034] The invention provides a single damascene method for reducing the sheet resistance of copper interconnects. The single damascene process is used to add the lower half of the copper interconnection that needs to reduce the sheet resistance in the through-hole layer. This layer requires two photolithographic etching processes. Then, metal filling and chemical mechanical polishing are performed to obtain the first part of the copper interconnection with reduced sheet resistance. Then, a single damascene process is used to construct a metal trench, and the thickness of the trench of all metal wires in this layer is the same. Due to the alignment of the upper and lower layers, there are also copper interconnects pre-set in the first layer under some metal wires. Therefore, compared with ordinary interconnects, this part of the copper interconnects has a thicker metal thickness. , Or there are two interconnections in parallel, so a lower sheet resistance is obtained.

[0035] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More