Distributed parallel minimum cost flow method and device for integrated circuit design

An integrated circuit and distributed technology, applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as increased access conflicts in the central queue, impact on parallel processing performance, and reduced practicability, and achieve fast speed improvement , reduce task queue access conflicts, and improve the effect of speedup

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

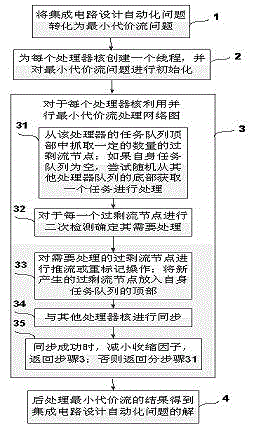

Method used

Image

Examples

Embodiment 1

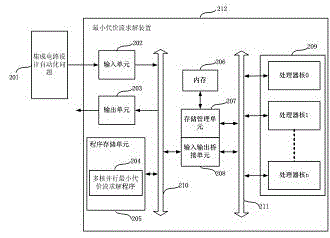

[0048] Such as figure 2 As shown, the present invention is based on a multi-processor core parallel distributed minimum cost flow solving device (212), including an input unit (202), an output unit (203), a program storage unit (205), an external bus (210), a memory (206), a storage management unit (207), an input-output bridge unit (208), a system bus (211), and a CPU (209) including n processor cores, the n processor cores may belong to one CPU or Belonging to multiple CPUs, multiple processor cores share the same memory unit ( 206 ) and communicate through the shared memory.

[0049] When the device solves the integrated circuit design automation problem, it first inputs the integrated circuit design automation problem (201) to the memory (206) through the input unit (202), and the input unit can be a keyboard, an external storage device or a network connection; at the same time, the multi-core The parallel minimum cost flow solving program (204) is also loaded into the me...

Embodiment 2

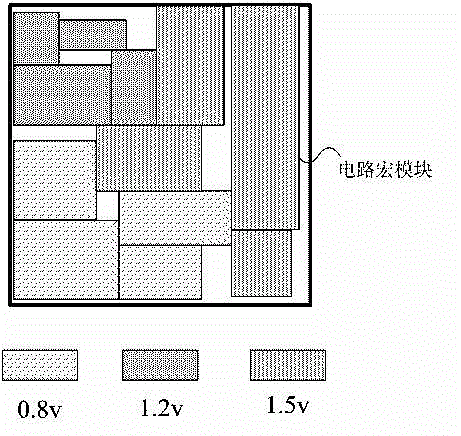

[0083] The present invention performs optimal voltage distribution under time sequence constraints on layout planning test instances n200-n1600. The numbers in the test examples indicate the number of macroblocks in the circuit. The multi-core processing device used in this example is a computer with four Intel dualcore CPUs and 2G memory, and supports up to 8 processor cores to run simultaneously.

[0084] Such as Figure 5 As shown, the results of the voltage distribution are shown in the figure and Y. Lu, H. Zhou, L. Shang and X. Zeng et al. published the paper "Multicore Parallel Min-Cost Flow for CAD Applications in IEEE / ACM Design Automation Conference 2009 "Compared with the speed-up of the traditional serial voltage distribution method. From Figure 5 As a result, it can be observed that the distributed parallel method proposed by the present invention is compared to the paper "Multicore Parallel Min-Cost Flow for The speed of the central queue scheduling method pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More