Method for forming dual damascene structure and semiconductor device

A dual damascene structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, etc. Problems such as poor layer adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] After a long period of research, the inventor found that due to the large stress difference between the second nitrogen-doped silicon carbide layer and the low-k second dielectric layer, the gap between the second nitrogen-doped silicon carbide layer and the low-k second dielectric layer Poor adhesion, prone to delamination problems.

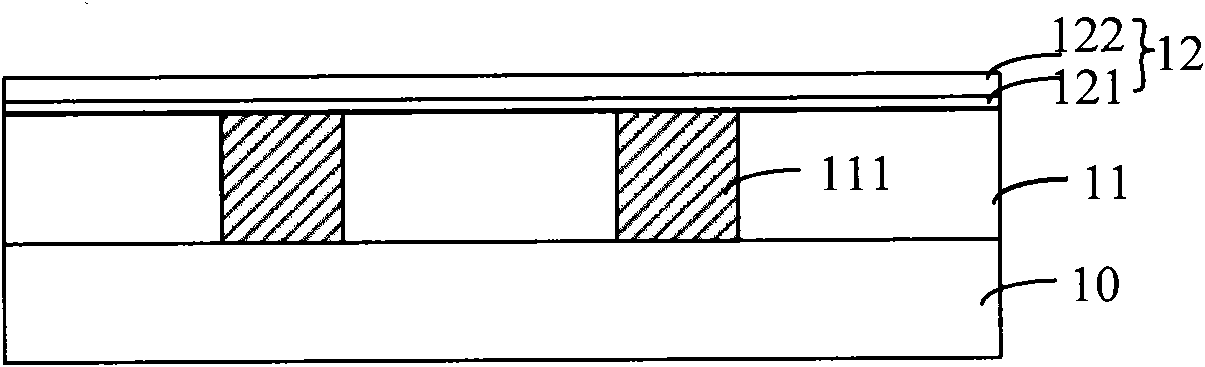

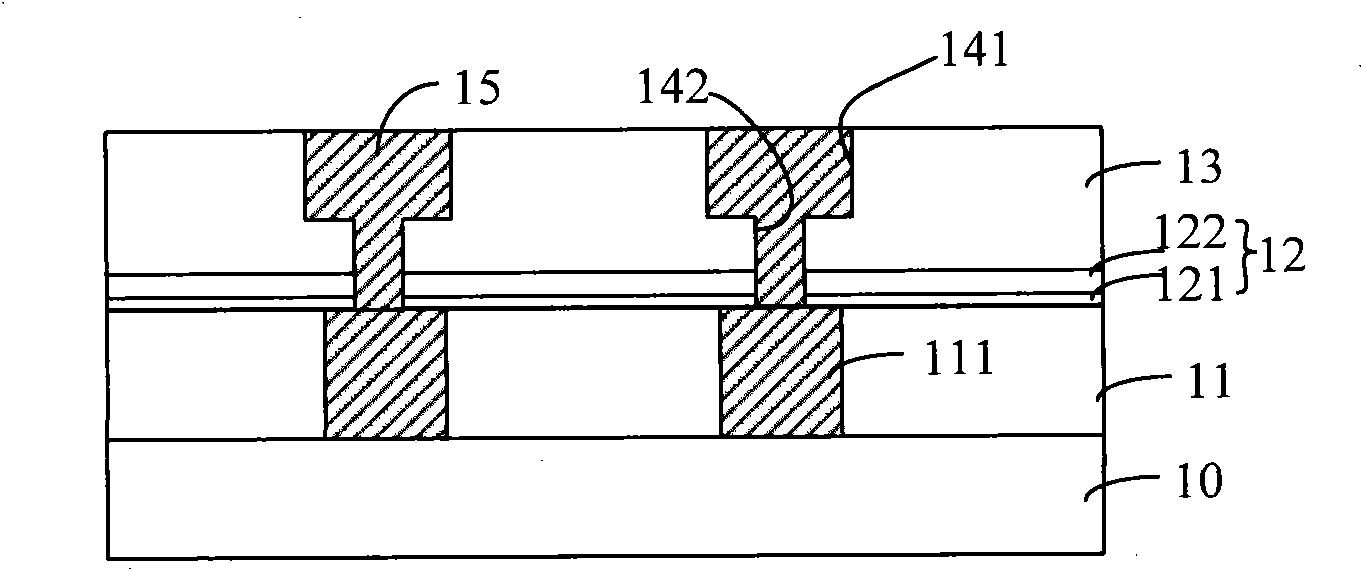

[0045] According to the method for forming a dual damascene structure and the method for forming a semiconductor device according to the specific embodiment of the present invention, a stress buffer layer is formed between the nitrogen-doped silicon carbide layer and the low-k second dielectric layer, and the stress buffer layer and the nitrogen-doped The stress difference between the silicon carbide layer and the low-k second dielectric layer is small, and the adhesion between them is good.

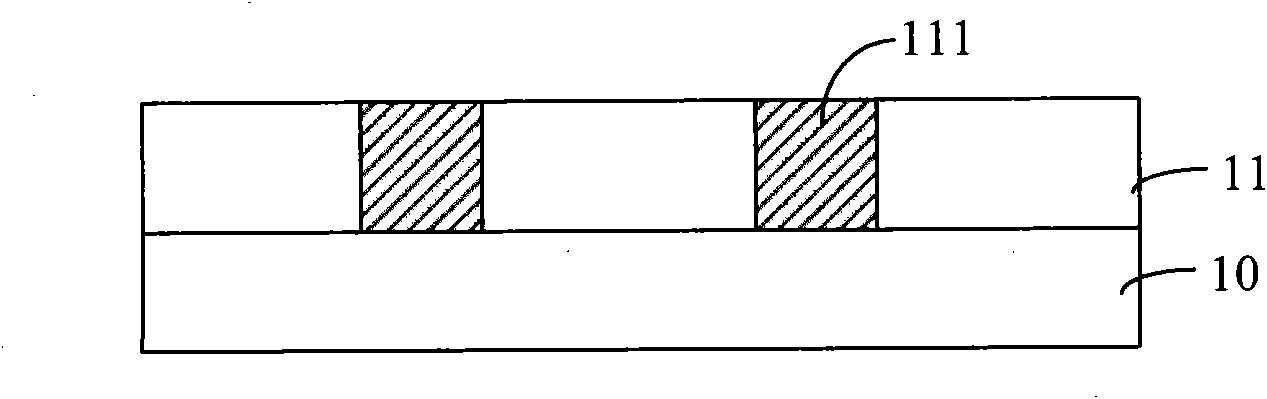

[0046] In order to enable those skilled in the art to better understand the present invention, specific embodiments of the present invention will b...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More