Method for forming semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve problems such as reducing the probability of carriers being trapped, and achieve the effect of suppressing hot electron effects and reducing interface defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

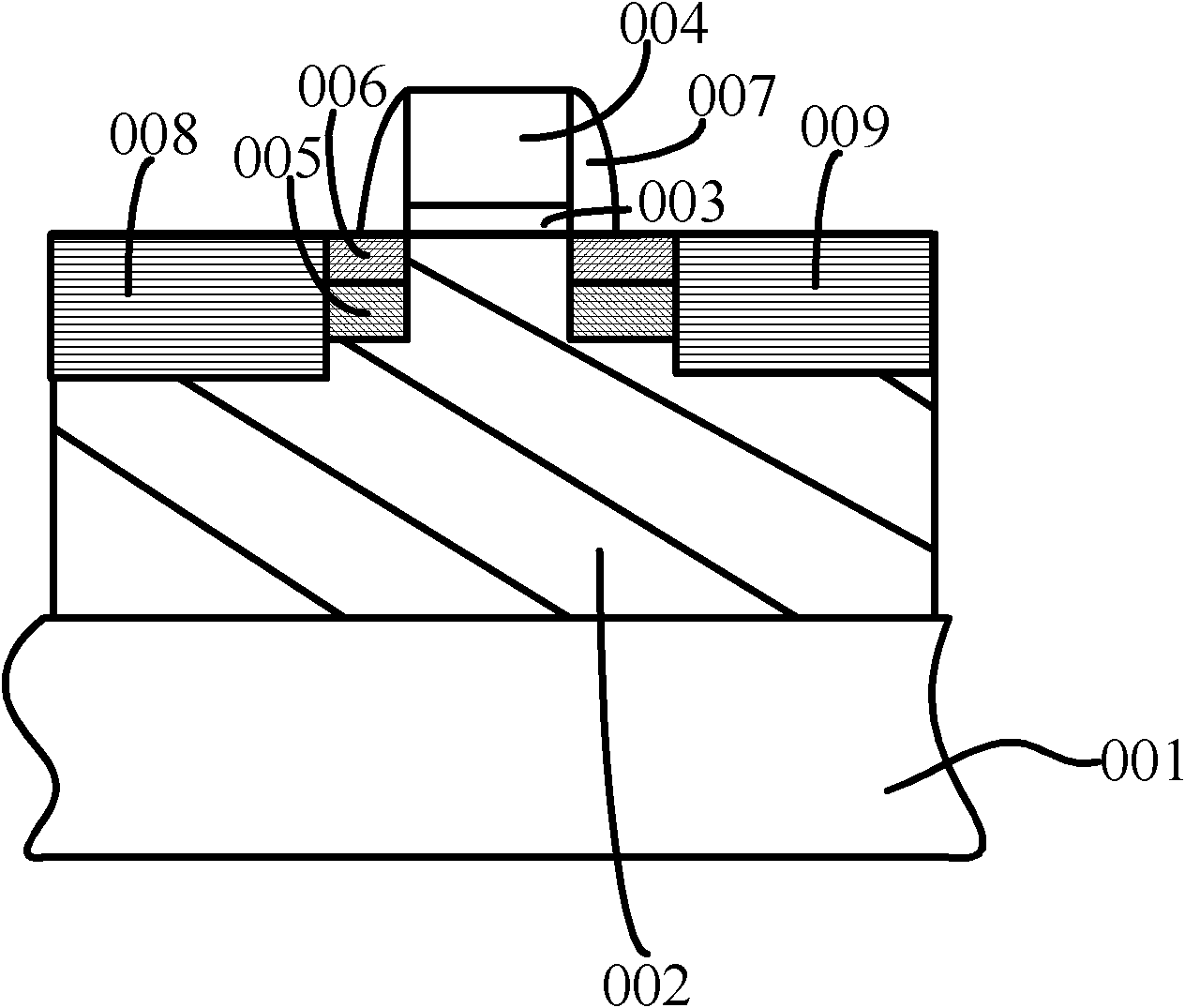

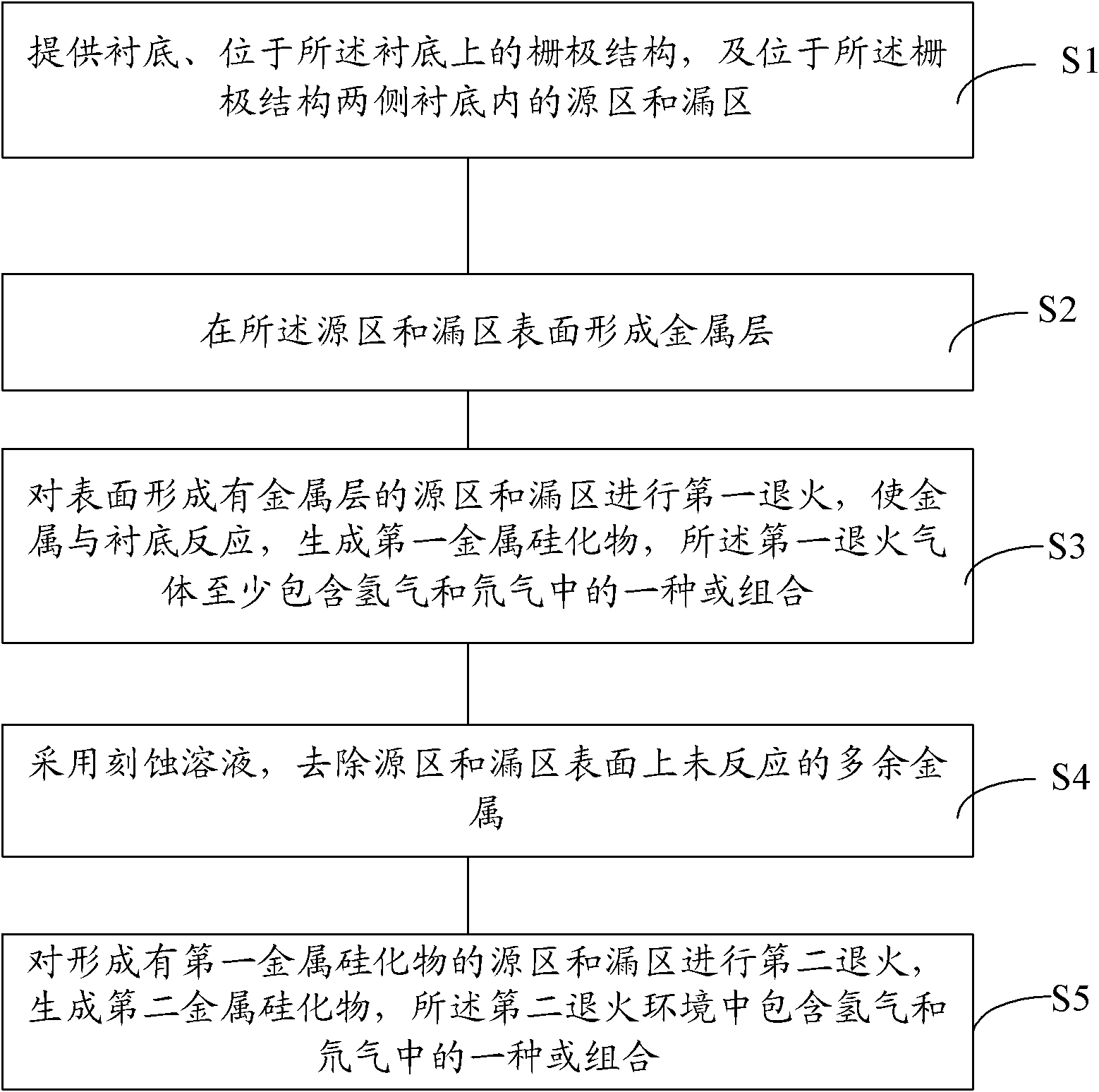

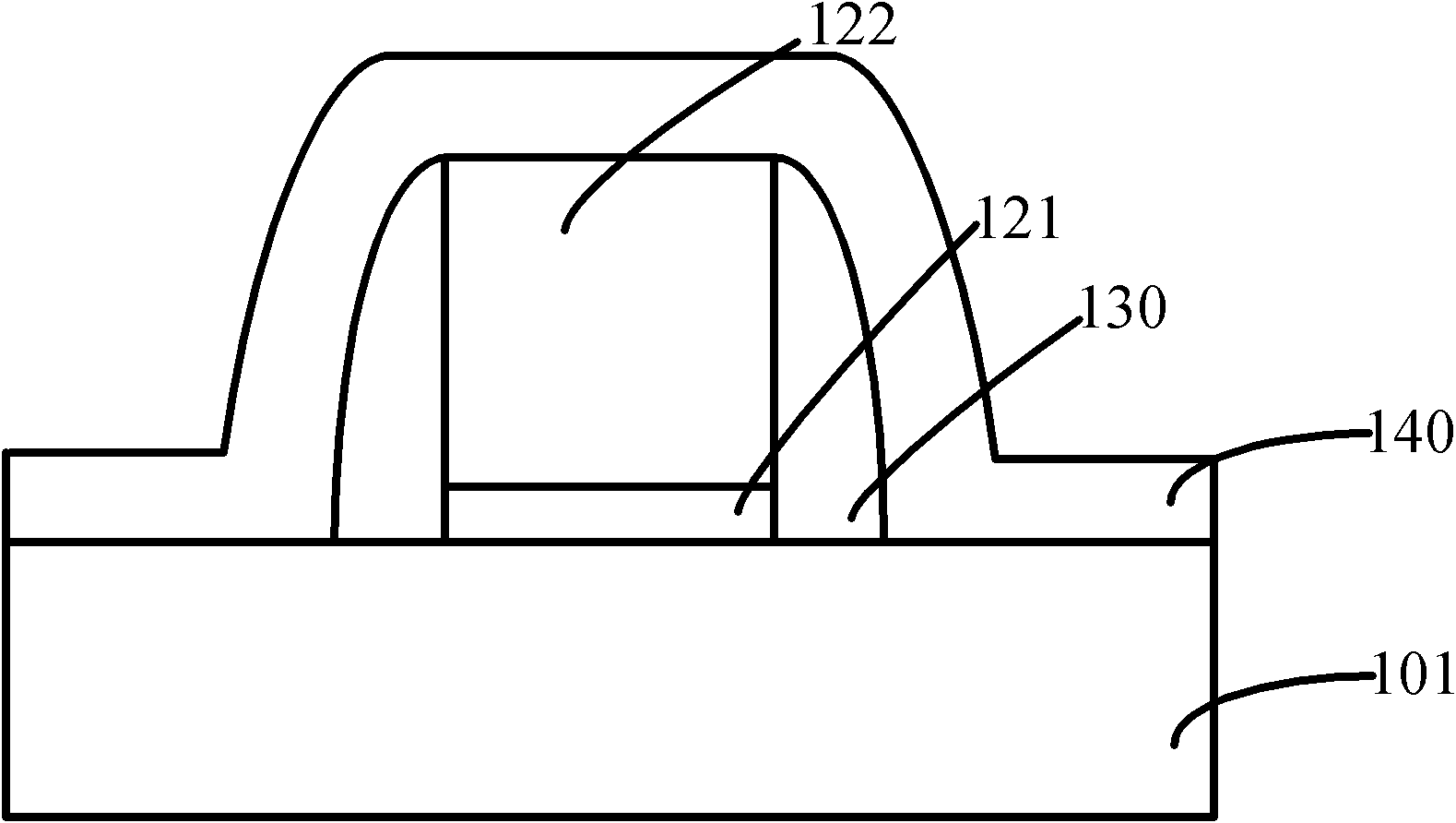

[0028] The invention provides a method for forming a semiconductor structure, including: providing a substrate, a gate structure on the substrate, and source regions and drain regions in the substrate on both sides of the gate structure; A metal layer is formed on the surface of the region and the drain region; an annealing process is performed on the source region and the drain region with the metal layer formed on the surface, and a metal silicide is formed in the source region and the drain region, wherein the annealing gas contains at least hydrogen and One or a combination of deuterium gases.

[0029] In the present invention, one or a combination of hydrogen and deuterium is added to any one or more annealing processes of the metal layer, so that the silicon dangling bonds in the substrate are bonded to one or a combination of hydrogen and deuterium combination, reduce the silicon dangling bonds located in the substrate, especially the silicon dangling bonds near the sub...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More