Device and method for processing clock-domain-crossing asynchronous data, chip and operating method of chip

An asynchronous data, cross-clock domain technology, applied in the field of data processing, can solve the problems that affect the data processing accuracy of the data processing device, the clock signal has not been processed synchronously, and the clock signal has no timing relationship, so as to achieve good data processing accuracy , Work stability is good, the effect of improving work stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

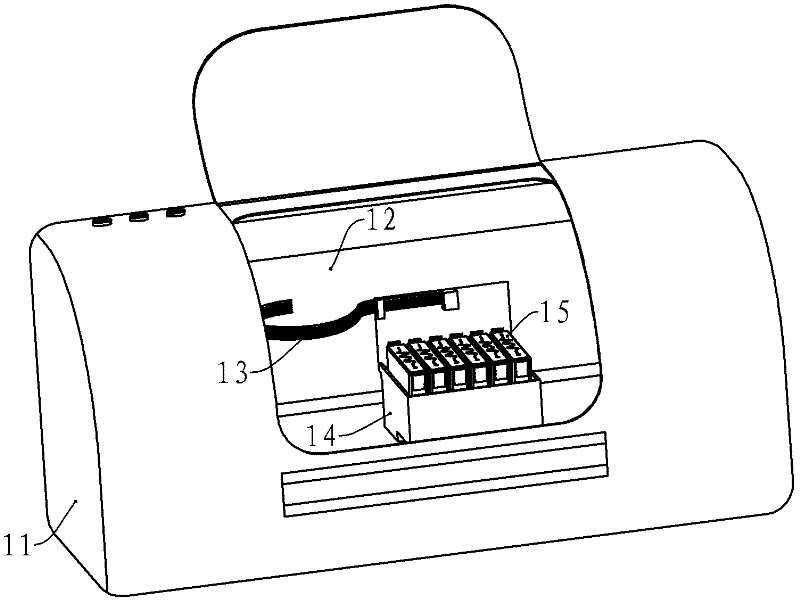

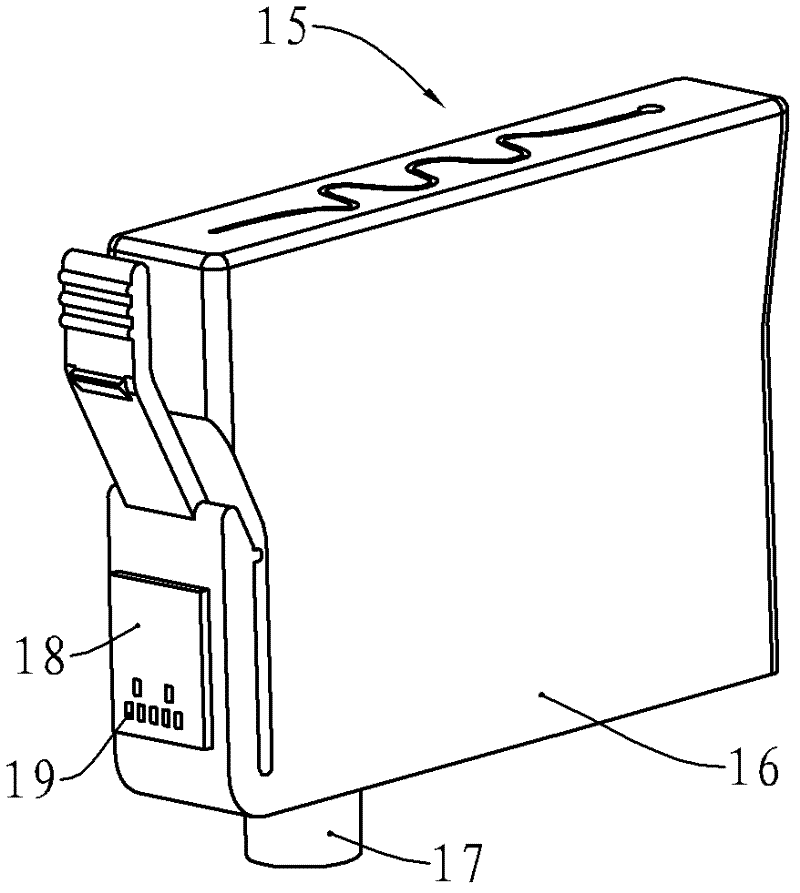

[0041] The chip of this embodiment is an ink cartridge chip, which has a substrate, and one side of the substrate is provided with a plurality of electrical contacts as a communication unit for connecting with the electrical contacts of the inkjet printer. Of course, if wireless communication is performed between the inkjet printer and the consumable chip, the communication unit is an antenna for wireless communication. The other side of the substrate is provided with an electronic module connected with the electrical contacts, and the electronic module has a microcontroller and peripheral circuits of the microcontroller, including a filter circuit, a delay circuit, and the like.

[0042] The electronic module needs to process data in multiple clock domains, so a cross-clock domain asynchronous data processing device is provided. The electrical schematic diagram of the data processing device in this embodiment is as follows Image 6 shown.

[0043] The cross-clock domain asyn...

no. 2 example

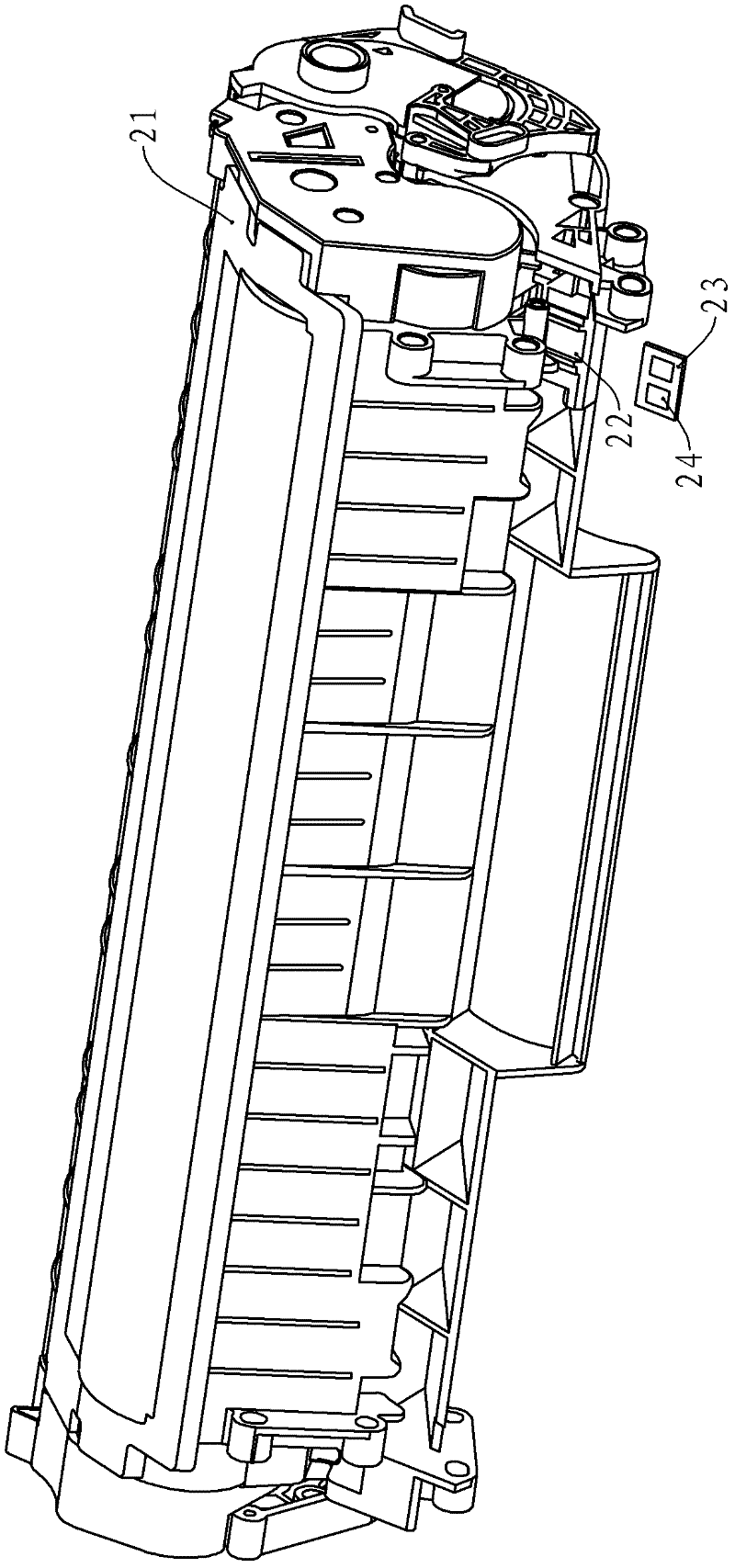

[0055] This embodiment has a substrate on which electrical contacts and an electronic module are arranged. The electronic module has a microcontroller and peripheral circuits, and is also provided with a cross-clock domain asynchronous data processing device. The electrical schematic diagram of the device is shown in the figure below. Figure 8 shown.

[0056] The cross-clock domain asynchronous data processing device has a reference clock signal generating unit CLK, which generates a reference clock signal CK. The signal CK21 and the second clock signal CK22 of the second clock domain are sampled to obtain the first synchronization clock signal CK1B and the second synchronization clock signal CK2B, respectively.

[0057] The data sampling units DFF21 and DFF24 respectively sample the data D21 and the data D under the reference clock signal CK to obtain the sampled data signals D2A and D2B, and the data signal D2A is sampled by the data sampling unit DFF23 under the first sync...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More