Clock generation circuit used in analog-to-digital converter (ADC) with high speed and high precision

A technology of clock generation circuit and analog-to-digital converter, which is applied in the direction of analog conversion, code conversion, electrical components, etc., can solve the problems of interference signal sampling, precision drop, etc., and achieve the effect of improving precision and avoiding requirement improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

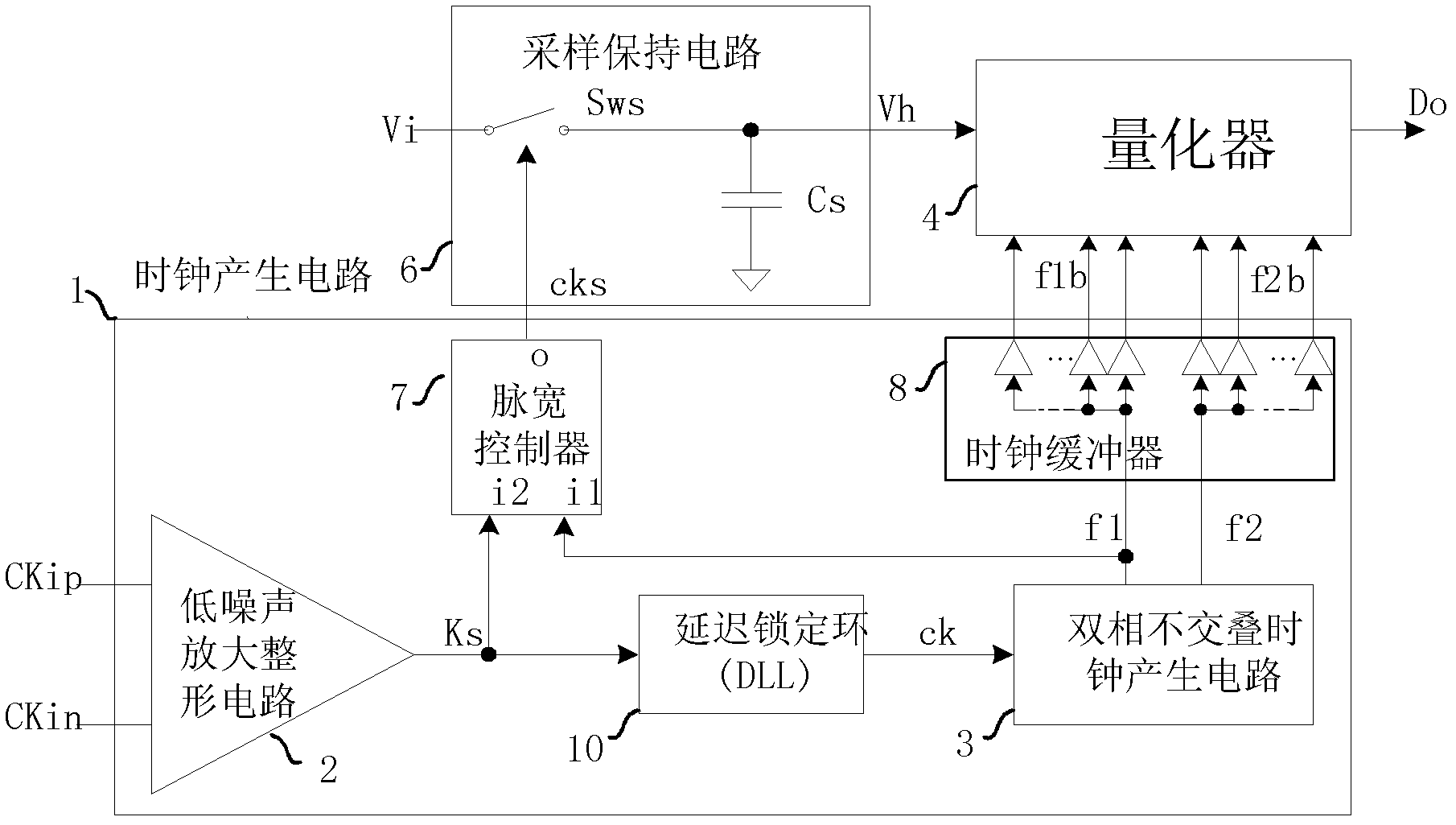

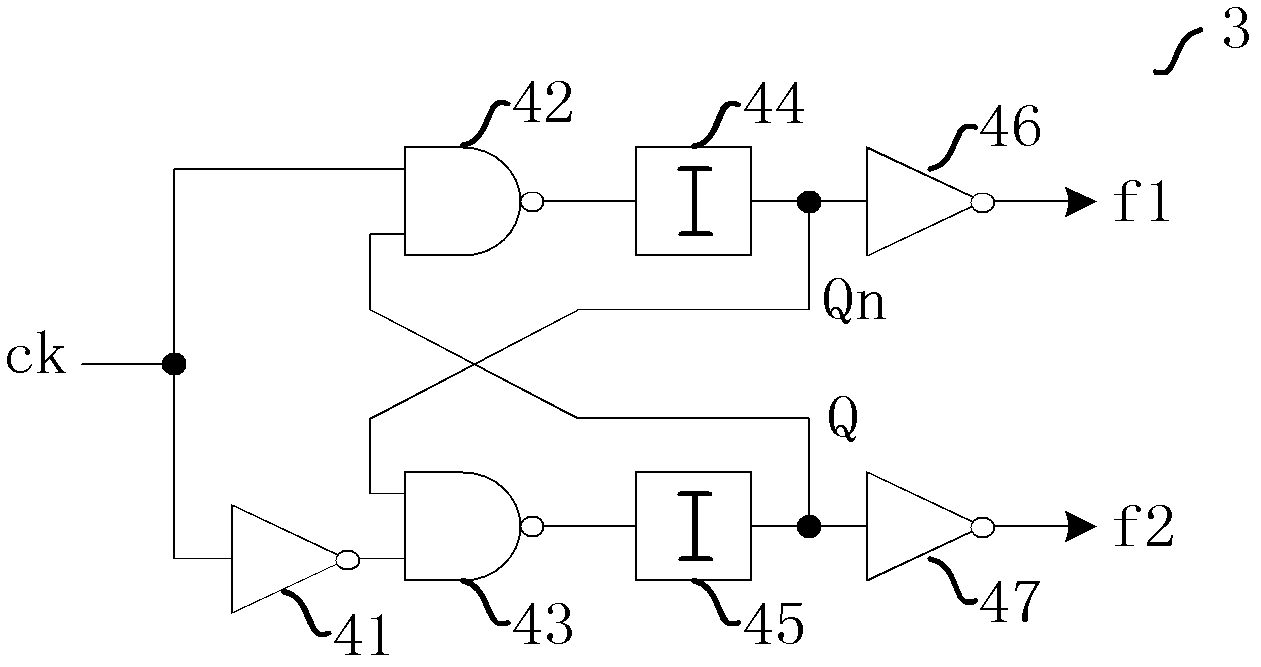

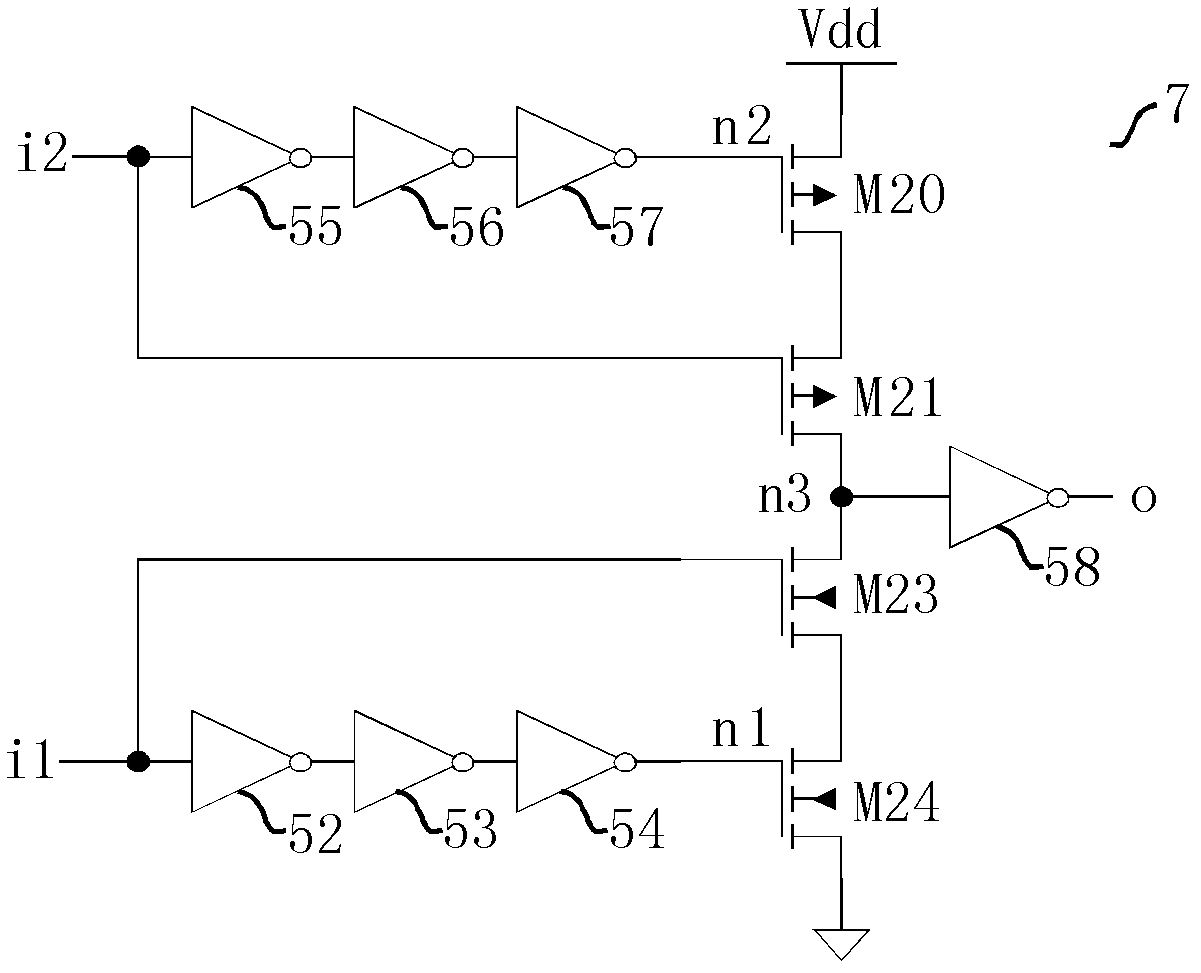

[0047] Figure 7 The block diagram of the high-speed ADC clock generation circuit provided by the embodiment of the present invention. Such as Figure 7 As shown, the entire ADC circuit is composed of a sample-and-hold circuit 6 , a quantizer 4 , and a clock generation circuit 5 . The sample and hold circuit 6 performs tracking sampling and holding on the analog input Vi to obtain the held voltage Vh, and the quantizer 4 performs quantization conversion on the voltage Vh to obtain the A / D conversion digital output Do. The clock generation circuit 5 is the core control module of the high-speed ADC, which provides the required control clock for the sample-and-hold circuit 6 and the quantizer 4 . The clock generation circuit 5 includes: a low-nois...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More