SRAM (static random access memory) and forming method thereof

A memory and storage unit technology, which is applied in the manufacture of electric solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of SRAM memory reading and writing stability to be improved, and achieve the effect of reducing complexity and simplifying process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

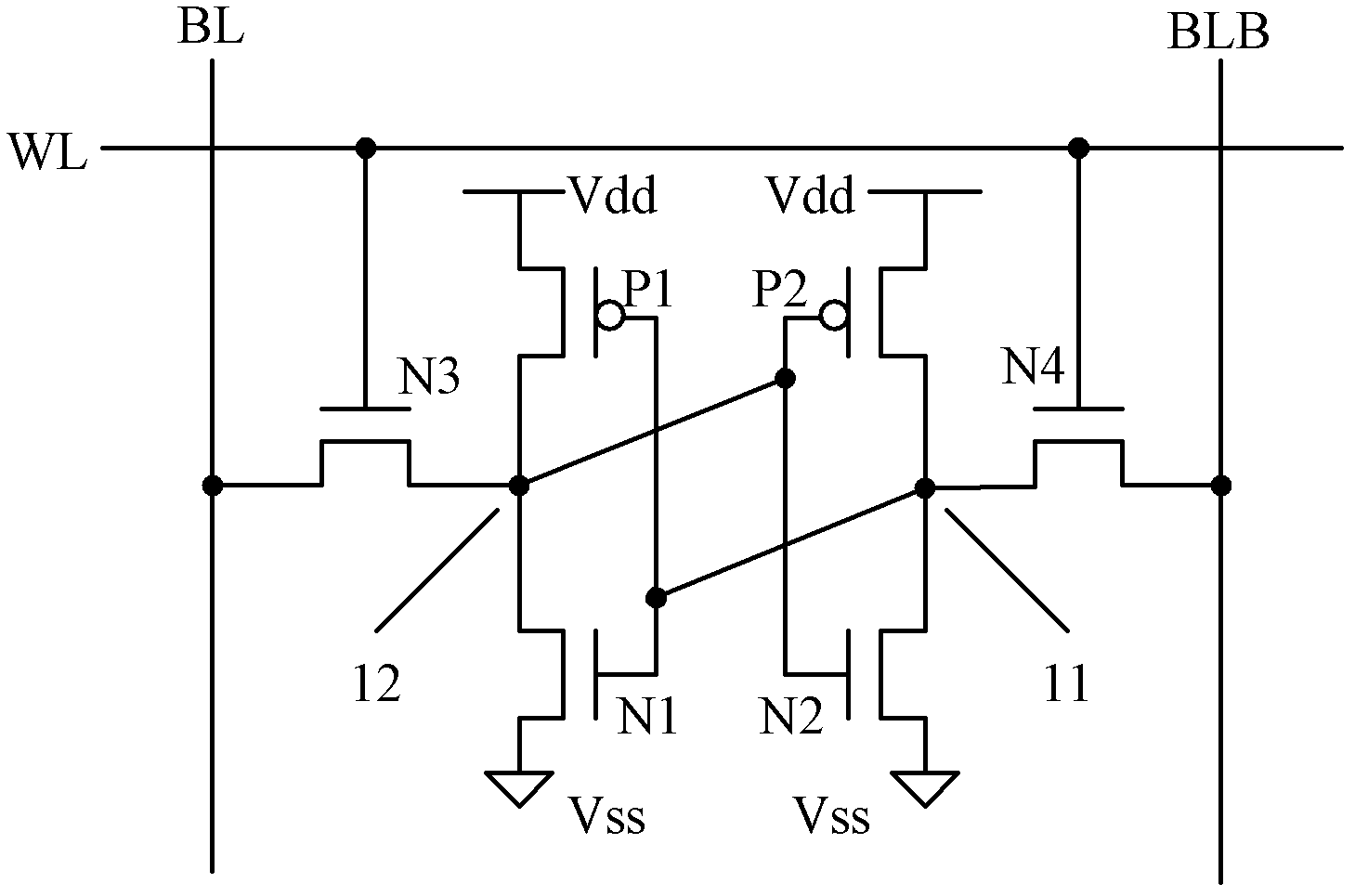

[0045] The read and write stability of SRAM memory is measured by the two parameters of read margin and write margin. Generally speaking, the higher the value of these two parameters, the read and write margin of SRAM memory The better the write stability, where the write margin is the ratio between the saturated source-drain current value of the transfer NMOS transistor and the saturated source-drain current value of the pull-up PMOS transistor; the read margin is the saturated source-drain current value of the pull-down NMOS transistor value to the saturation source-drain current value of the pass NMOS transistor.

[0046] The inventor found in the existing process of manufacturing SRAM memory that the existing SRAM memory forms a tensile stress layer on the surface of the NMOS transistor and a compressive stress layer on the surface of the PMOS transistor, although the transfer of carriers in the NMOS transistor and the PMOS transistor can be improved rate, but the improvem...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Stress | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More