Single electron transistor (SET)/metal oxide semiconductor (MOS) mixed structure multiplier unit based on threshold logic

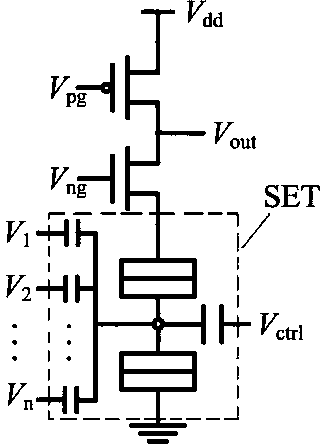

A technology of threshold logic and hybrid structure, applied in logic circuits, electrical components, pulse technology, etc., can solve the problems of consuming multiple CMOS transistors, short channel effects, strong field effects, etc., and achieve the reduction of the number of tubes, the simplification of the circuit structure, The effect of increasing the degree of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

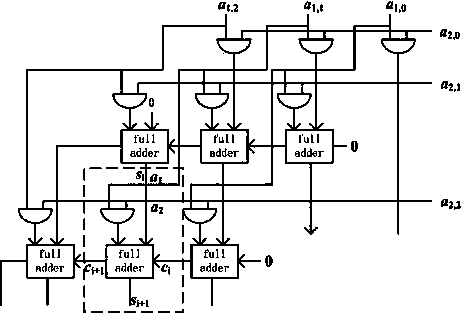

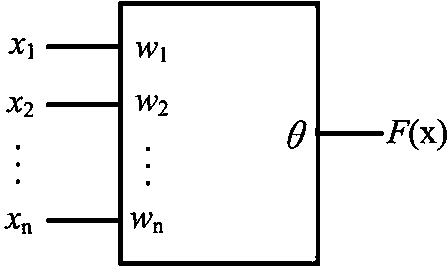

[0017] Such as image 3 As shown, the present invention provides a SET / MOS hybrid structure multiplier unit based on threshold logic, including first, second, third, and fourth signal sources, four input threshold logic gates, five input threshold logic gates, and an inverter; The first signal source a 1 Connected with the first input end of the four-input threshold logic gate and the first input end of the five-input threshold logic gate; the second signal source a 2 Connected with the second input end of the four-input threshold logic gate and the second input end of the five-input threshold logic gate; the third signal source s i Connected with the third input end of the four-input threshold logic gate and the third input end of the five-input threshold logic gate; the fourth signal source c i It is connected with the fourth input end of the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More