Thin film transistor liquid crystal display array substrate and manufacturing method thereof

A thin-film transistor and liquid crystal display technology, which is applied in semiconductor/solid-state device manufacturing, instruments, electrical components, etc., can solve the problems of easy breakpoints in signal lines and poor TFT-LCD array substrates, etc., to reduce the chance of drilling, The effect of reducing the slope angle and reducing the probability of signal line disconnection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

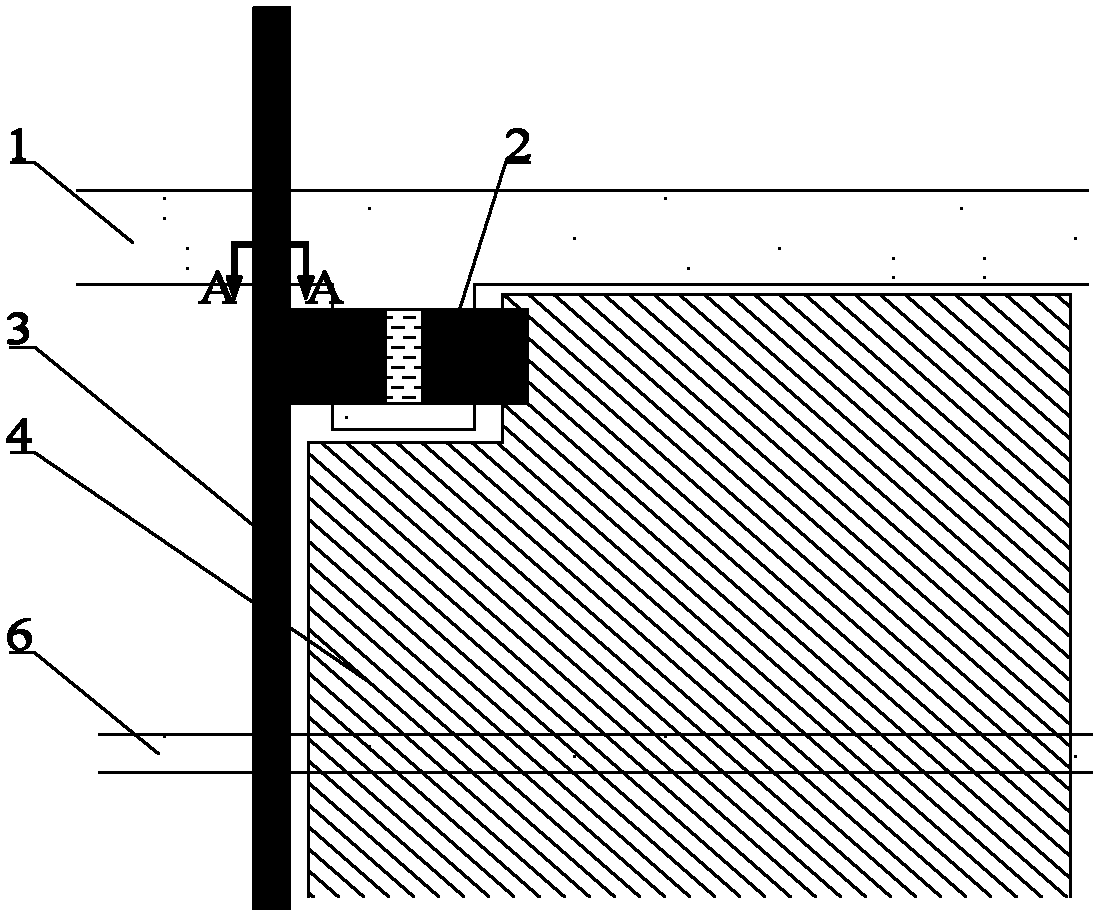

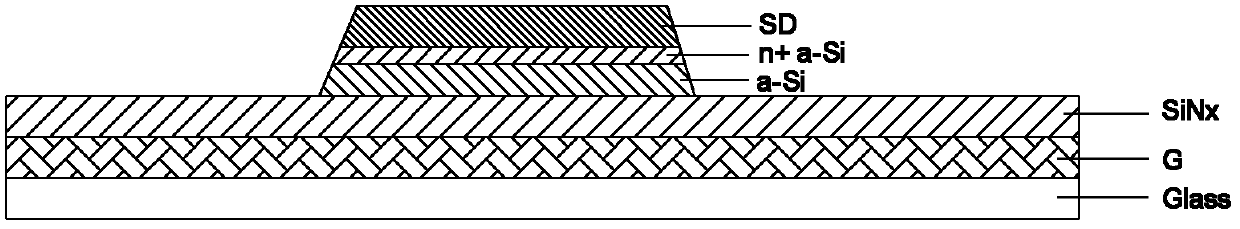

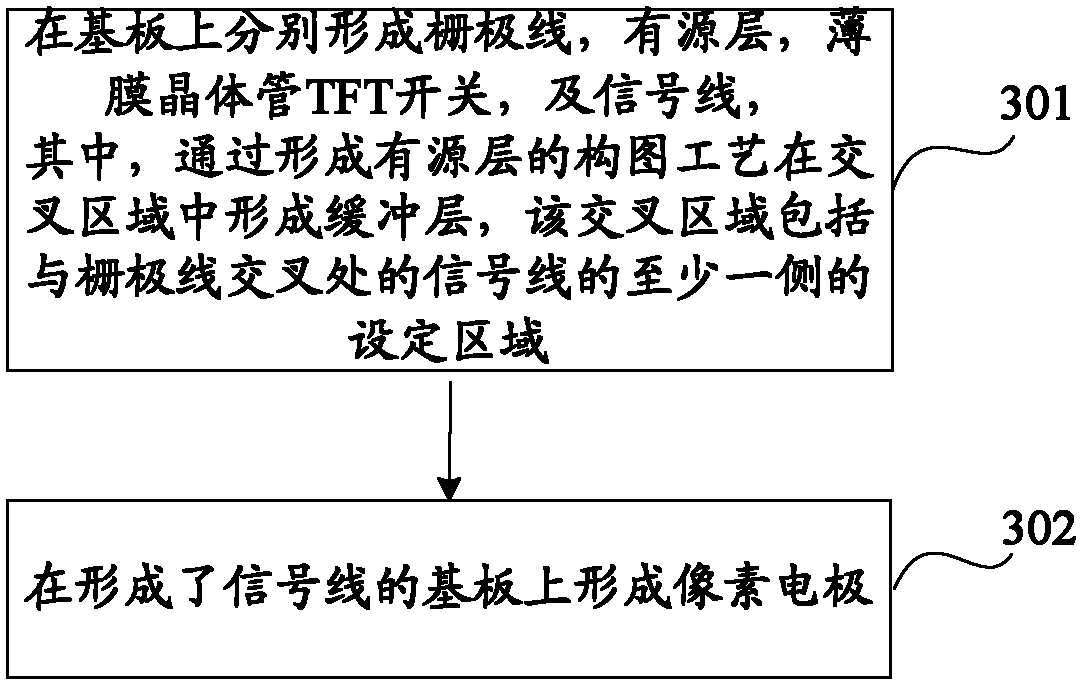

[0046] Embodiment 1. In this embodiment, forming a TFT-LCD array substrate through four patterning processes includes: forming gate lines on the substrate through the first patterning process. The substrate of the TFT-LCD array substrate is generally a glass substrate. , Using sputtering or thermal evaporation method to deposit a layer of gate metal layer on the substrate, then, after applying photoresist on the gate metal layer, the photoresist is exposed through a mask with gate line patterns , Development, and formation of gate lines through processes such as etching and stripping. Here, the etching is wet etching, and the metal that is not covered by the photoresist is etched away by the chemical solution. The material of the gate metal layer includes one or more of Al, Mo, Cu, MoW, and Cr.

[0047] The active layer, the thin film transistor TFT switch, and the signal line are formed on the substrate on which the gate line is formed through the second patterning process. Amo...

Embodiment 2

[0071] Embodiment 2. In this embodiment, forming a TFT-LCD array substrate through five patterning processes includes: forming gate lines on the substrate through the first patterning process; depositing a semiconductor layer and doping on the substrate where the gate lines are formed. In the hetero semiconductor layer, the active layer and the TFT channel are formed by the second patterning process; the signal lines and the TFT source and drain electrodes are formed on the substrate with the TFT channel formed by the third patterning process; and the TFT source and drain electrodes are formed by the fourth patterning process The process forms a passivation layer and a passivation layer via hole is formed on the drain electrode of the TFT switch; finally, the pixel electrode is formed through the fifth patterning process, and the pixel electrode is connected to the drain electrode of the TFT switch through the via hole. Wherein, a buffer layer is formed in the intersection area ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| transmittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More