Alignment mark structure of medium substrate zero layer

A technology of zero-layer alignment marks and dielectric substrates, which is applied in the fields of optics, instruments, and photoplate-making on patterned surfaces, etc., can solve problems such as inconvenient alignment, easy confusion, and difficulty in searching for alignment marks, and achieves easy Search, easy alignment effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

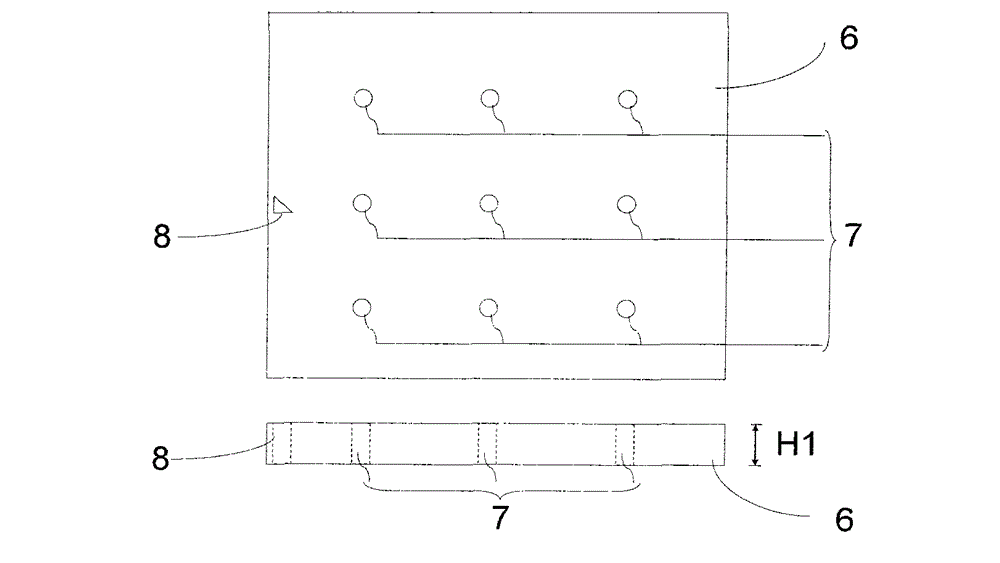

[0029] See figure 2 The zero-layer alignment mark structure 8 of the dielectric substrate is a longitudinal through hole arranged at the edge of the dielectric substrate 6 and is a right triangle. In this embodiment, the dielectric substrate 6 where the zero-layer alignment mark structure 8 of the dielectric substrate is located is made of 99.6% or more alumina ceramics, the plane size is 5.08 mm×5.08 mm, and the thickness H1 is 0.635 mm.

Embodiment 2

[0031] See image 3 The zero-layer alignment mark structure 9 of the dielectric substrate is a longitudinal through hole provided on the edge of the dielectric substrate 6 and is a rectangle. In this embodiment, the dielectric substrate 6 where the zero-layer alignment mark structure 9 of the dielectric substrate is located is made of 99.6% or more alumina ceramics, the plane size is 5.08 mm×5.08 mm, and the thickness H2 is 0.254 mm.

Embodiment 3

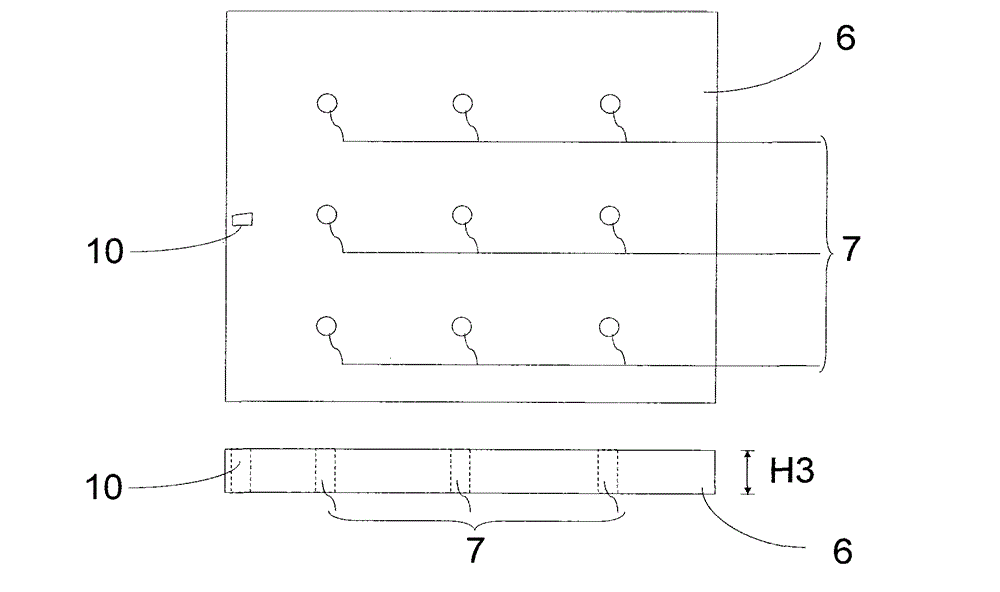

[0033] See Figure 4 The zero layer alignment mark structure 10 of the dielectric substrate is a longitudinal through hole arranged on the edge of the dielectric substrate 6 and is a right-angled trapezoid. In this embodiment, the dielectric substrate 6 where the zero-layer alignment mark structure 10 of the dielectric substrate is located is made of sapphire, the plane size is 5.08 mm×5.08 mm, and the thickness H3 is 0.508 mm.

[0034] In the manufacturing process of microwave thin film hybrid integrated circuits, use Figure 2 to Figure 4 The zero-layer alignment mark structures 8, 9, and 10 of the dielectric substrate can ensure that the microwave thin film hybrid integrated circuit on the dielectric substrate is manufactured at its preset position.

[0035] To sum up, the zero-layer alignment mark structure of the dielectric substrate of the present invention is a right-angled longitudinal through hole arranged on the edge of the dielectric substrate, which can ensure that the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More