Method for fabricating a semiconductor power device

A technology of power semiconductors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as incomplete contact of contact surfaces, uneven junctions in depletion regions, and reduction of super interface withstand voltage capacity, etc., to achieve The effect of improving the pressure resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

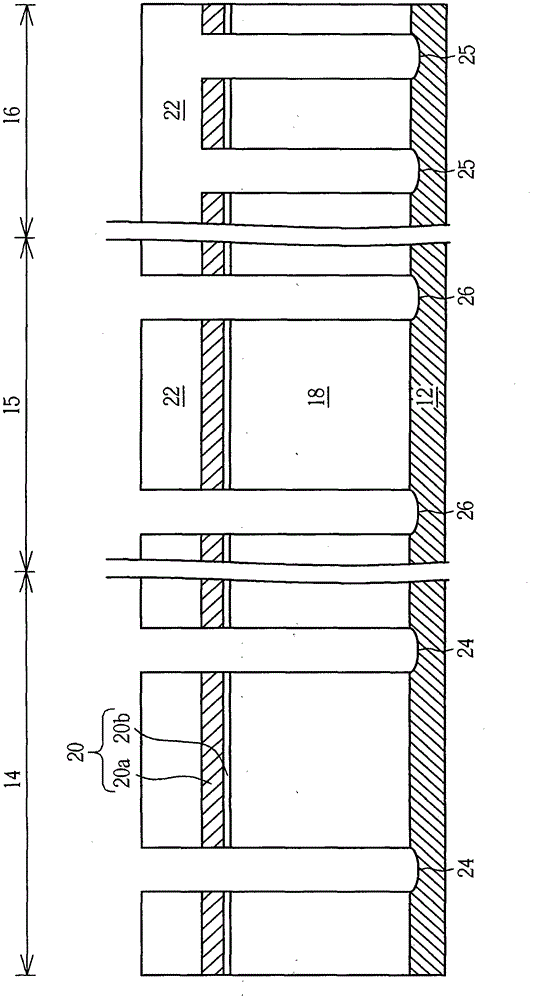

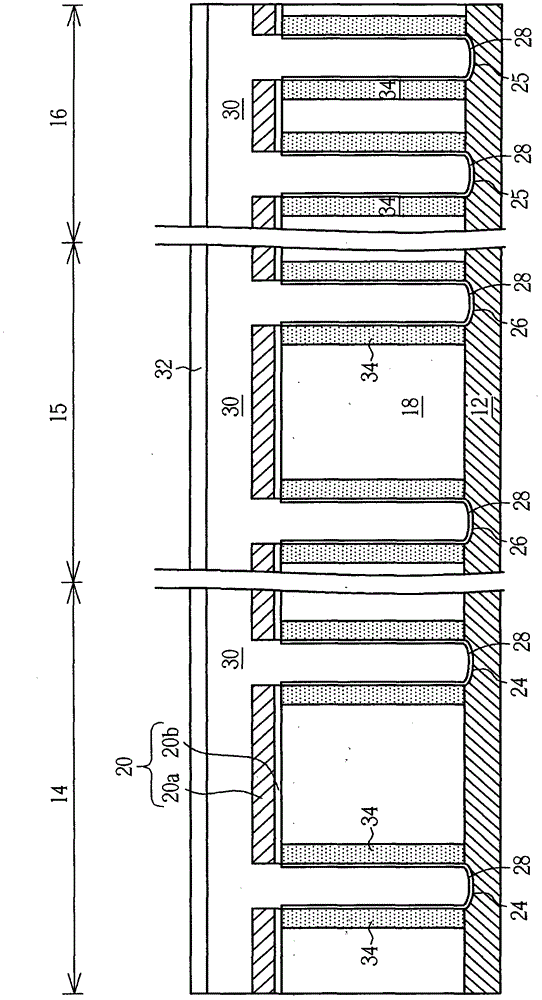

[0030] Please refer to Figure 1 to Figure 16 , which is characterized in that the manufactured power device may include trench power MOSFETs, and the same devices or parts in the drawings are represented by the same symbols. It should be noted that the drawings are for illustration only and are not to scale.

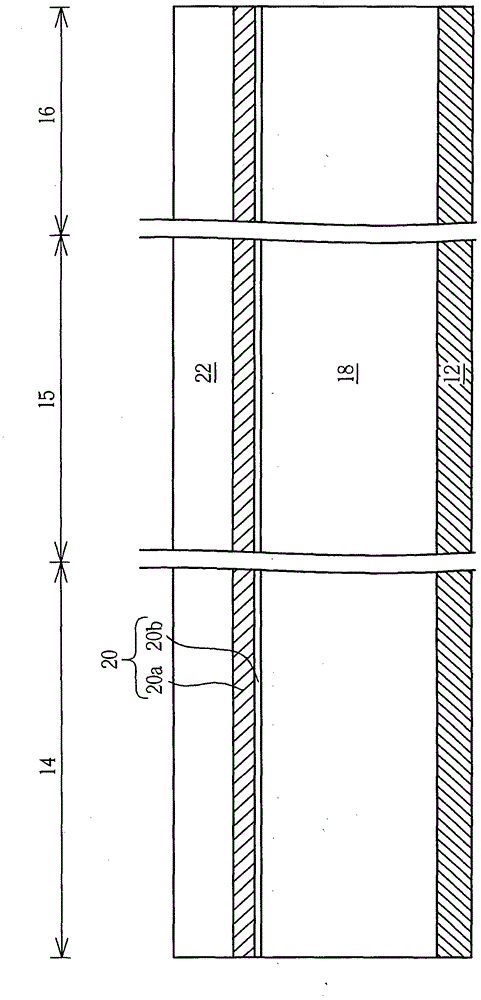

[0031] Please refer to figure 1 Firstly, a substrate 12 of the first conductivity type is provided, and the substrate 12 of the first conductivity type is an N+ type doped silicon substrate, which can be regarded as a drain of a power MOSFET. A cell region (cell region) 14 is defined on the substrate 12 of the first conductivity type, a peripheral voltage-resistant region (termination region) 16 surrounding the cell region 14, and a termination region (termination region) 16 disposed between the cell region 14 and the peripheral voltage-resistant region 16 are defined. The transition region (transition region) 15 is characterized in that the transistor device with swi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More