Longitudinal power device for low-ratio on-resistance employing groove structure with high dielectric constant

A technology with high dielectric constant and specific on-resistance, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of application limitation, accumulation effect limitation, low constant, etc., and achieve the effect of increasing carrier concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

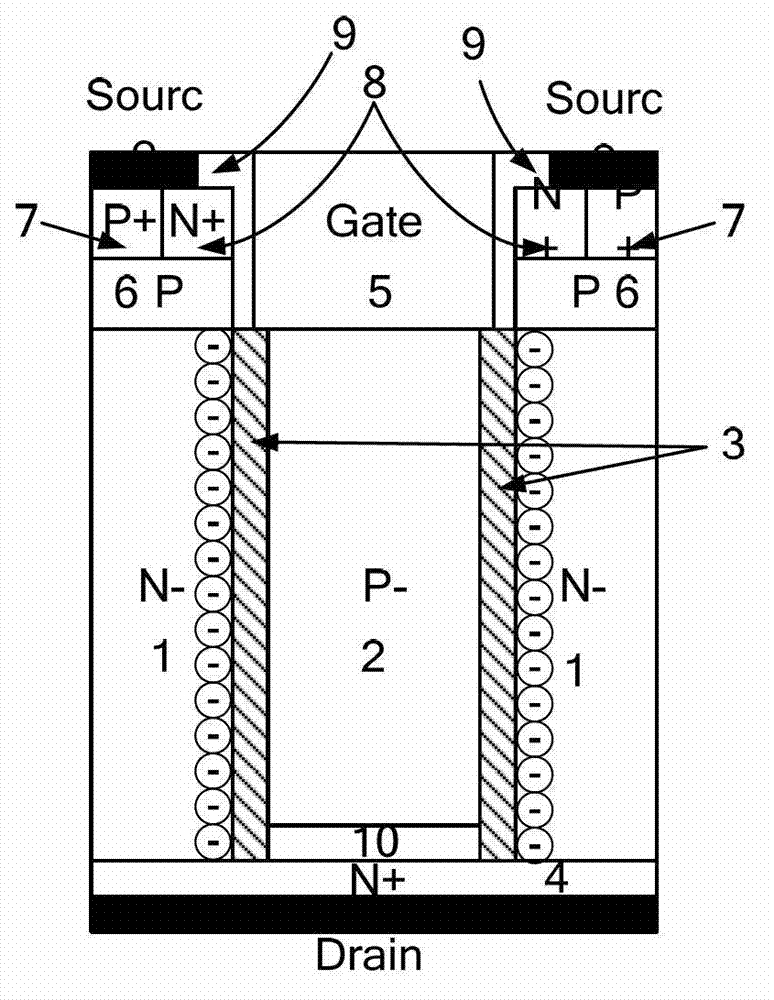

[0030] see figure 1 . In this embodiment, N+ is used as the silicon substrate 4 , N− is used as the drift region 1 , and P− is used as the second filling material 2 inside the high dielectric constant column. In addition, it also includes a P-type doped channel region 6, an ohmic contact heavily doped region 7, a source 8, a polysilicon gate 5, a silicon dioxide insulating gate dielectric 9, a high dielectric constant material column 3, and an isolation insulating dielectric 10, and the isolation insulating medium 10 is located at the bottom of the high dielectric constant column. 10 may use the same material as the high dielectric constant material column 3, or other insulating materials.

[0031] When the device is in the off state, although there are high dielectric constant material columns 3, the alternation of the drift region 1 and the second filling material 2 will still produce the charge balance of the Super Junction, and the introduction of the high dielectric ma...

Embodiment 2

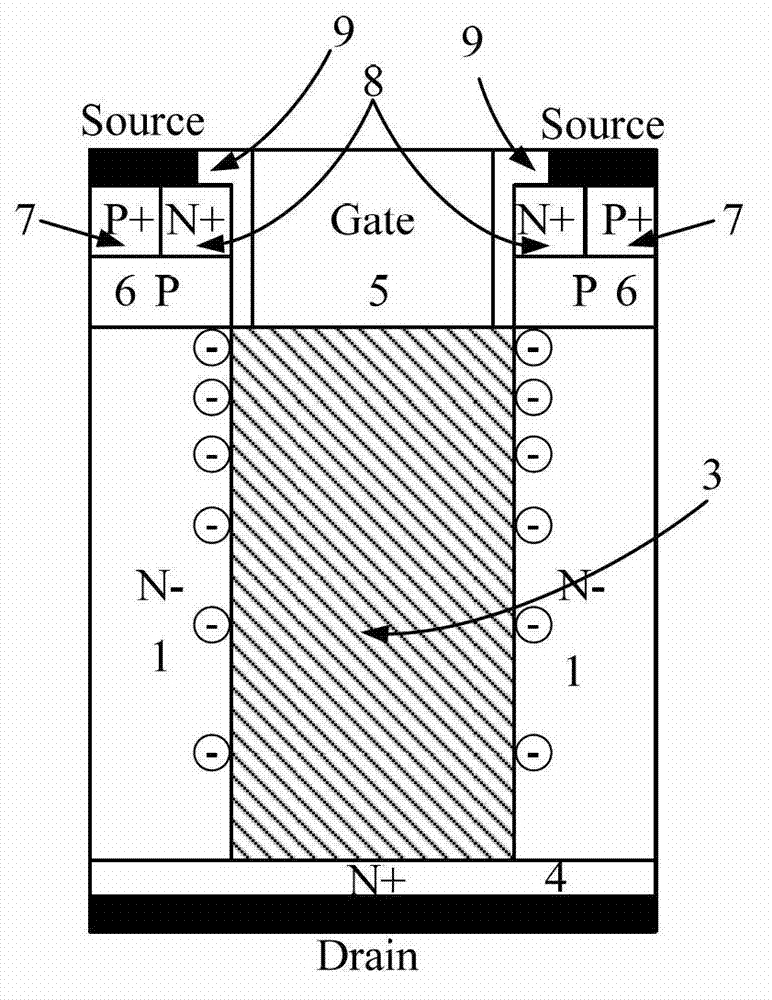

[0033] see figure 2 . In this embodiment, N+ is used as the silicon substrate 4 , N− is used as the drift region 1 , and P− is used as the second filling material 2 of the high dielectric constant column. In addition, it also includes P-type doped channel region 6 , ohmic contact heavily doped region 7 , source 8 , polysilicon gate 5 , silicon dioxide insulating gate dielectric 9 , and high dielectric constant material pillar 3 . At the same time, the same material as the high dielectric constant material column 3 is used as the internal filling and isolation insulating medium 10 , that is, the solid high dielectric constant material column 3 . According to the Poisson equation: the slope of the electric field distribution in the N-drift region satisfies: qN D / ε, and in this embodiment, the high dielectric constant occupies a larger proportion of the drift region, so the average dielectric constant ε in the drift region is larger than that of embodiment 1. Although there ...

Embodiment 3

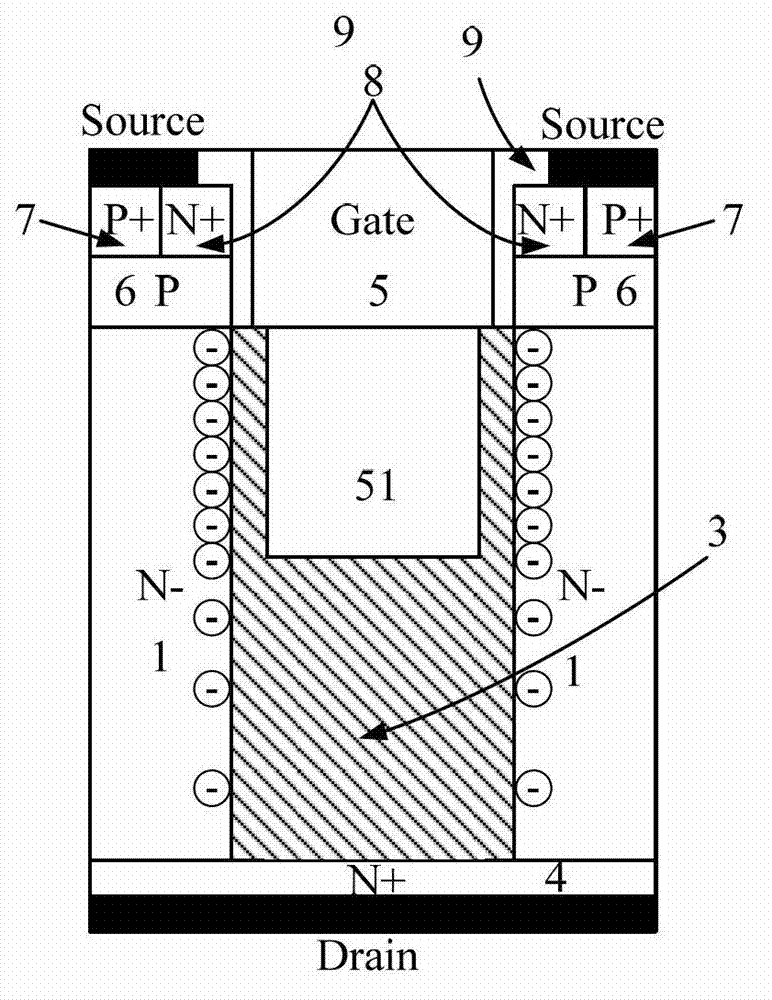

[0035] see image 3 . In this embodiment, N+ is used as the silicon substrate 4 , N− is used as the drift region 1 , and P− is used as the second filling material 2 inside the high dielectric constant column. In addition, it also includes a P-type doped channel region 6, an ohmic contact heavily doped region 7, a source electrode 8, a polysilicon gate 5, a silicon dioxide insulating gate dielectric 9, a high dielectric constant material column 3, and an isolation dielectric 10 located at The bottom of the high dielectric constant pillar. Use the same high dielectric constant material column 3 as the filling material for the lower half of the high dielectric constant column to achieve isolation, and use the material of the gate 5 (polysilicon or metal) as the high dielectric constant material column 3 The top half is filled with material. This embodiment also only uses the electric field modulation effect of the high dielectric material to optimize the distribution of the el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com