Active power factor correction (PFC) control circuit based on complex programmable logic device (CPLD)

A technology for controlling circuits and converting circuits, which is applied in the fields of electrical components, energy industry, sustainable manufacturing/processing, etc. It can solve problems such as the contradiction between sampling frequency and switching frequency, difficulty in setting PI parameters, sensitive circuit parameters, etc., and achieve robustness Good results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

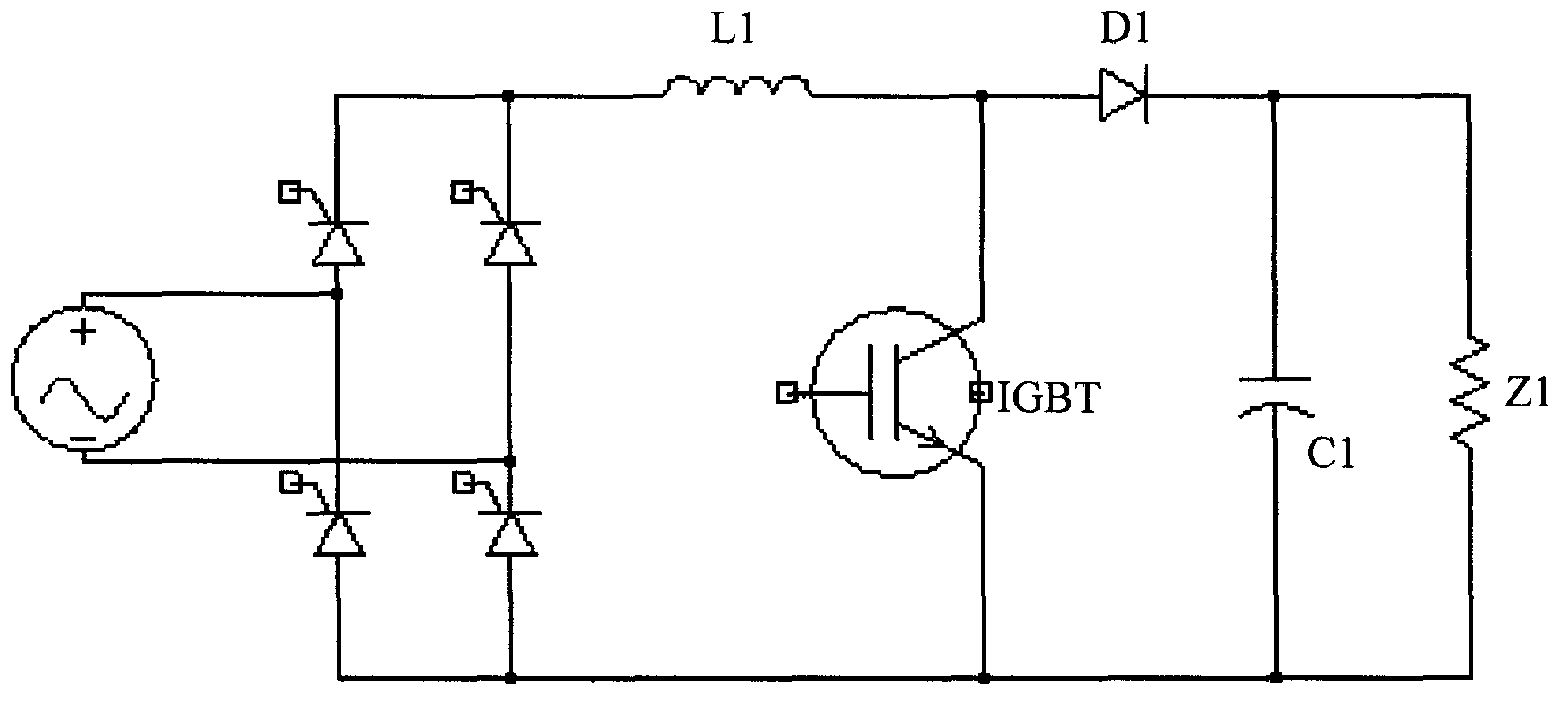

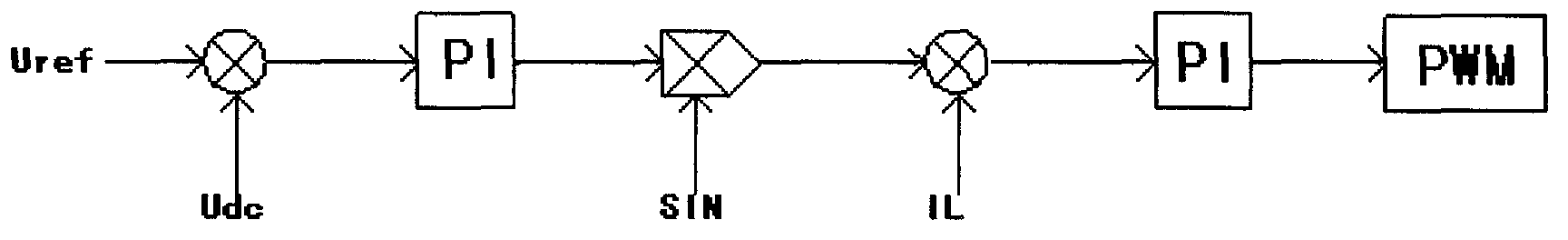

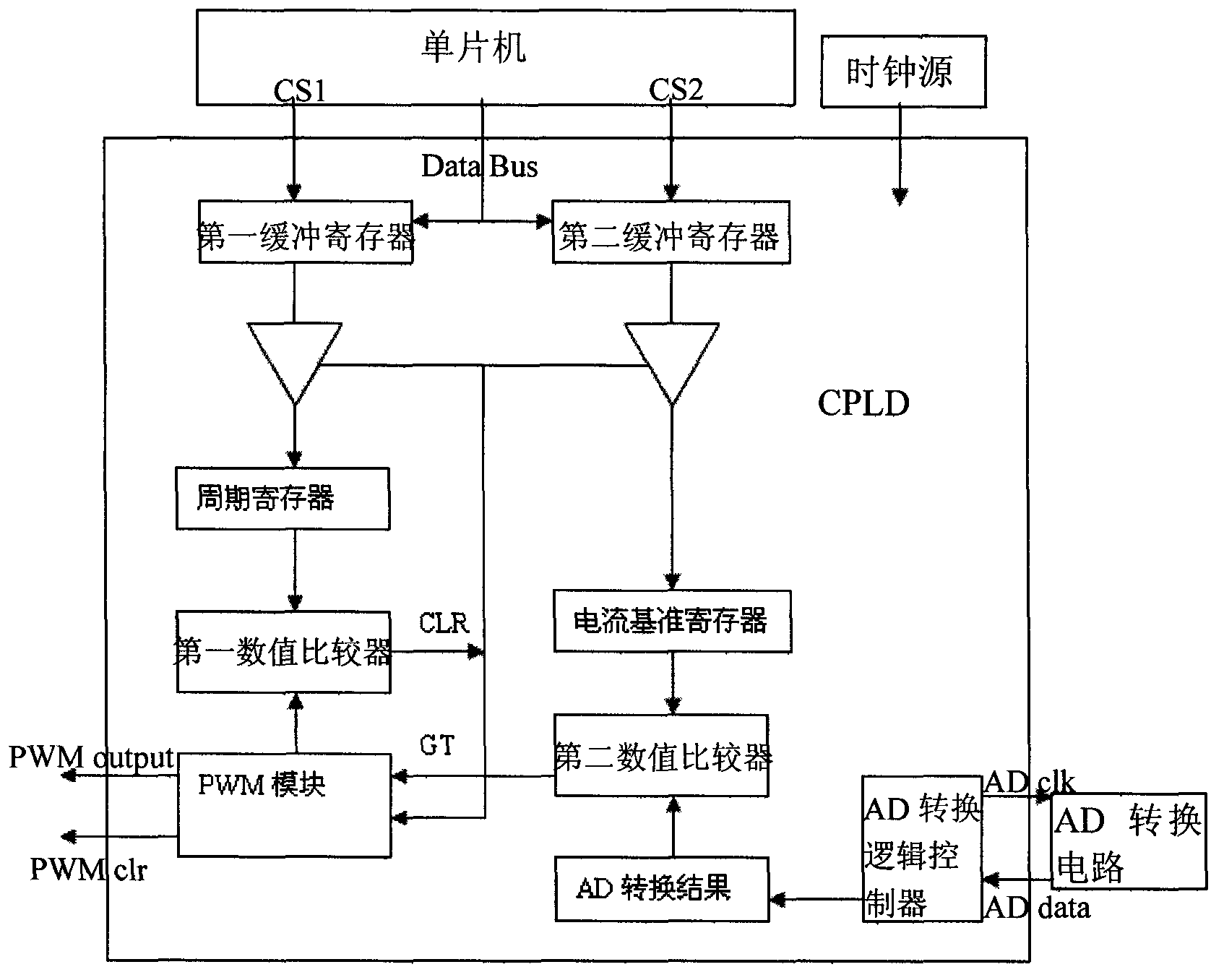

[0021] Such as image 3 A CPLD-based active PFC control circuit is shown, which includes a CPLD, a single-chip microcomputer, an AD conversion circuit, a clock source, and a current sampling circuit for current sampling of an inductor in a BOOST-type PFC circuit topology. The CPLD includes the first A buffer register, a second buffer register, a period register, a first numerical comparator, a second numerical comparator, a current reference register, a PWM module capable of generating a triangular wave reference, and an AD conversion circuit for controlling AD conversion and storing AD conversion results The AD conversion logic controller, the first buffer register is connected with the period register and the first numerical comparator PWM module in turn, the second buffer register is connected with the current reference register, the second numerical comparator, and the AD conversion logic controller in turn, and the single-chip microcomputer has The corresponding data comm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com