Method for manufacturing shallow trench isolation

A manufacturing method and shallow trench technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as device performance degradation and STI sidewall roughness, and achieve the effect of reducing roughness.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

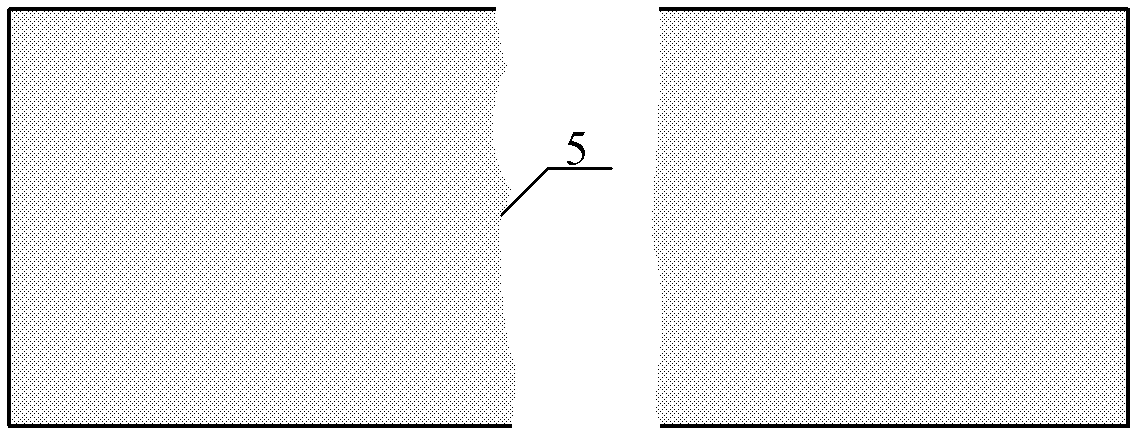

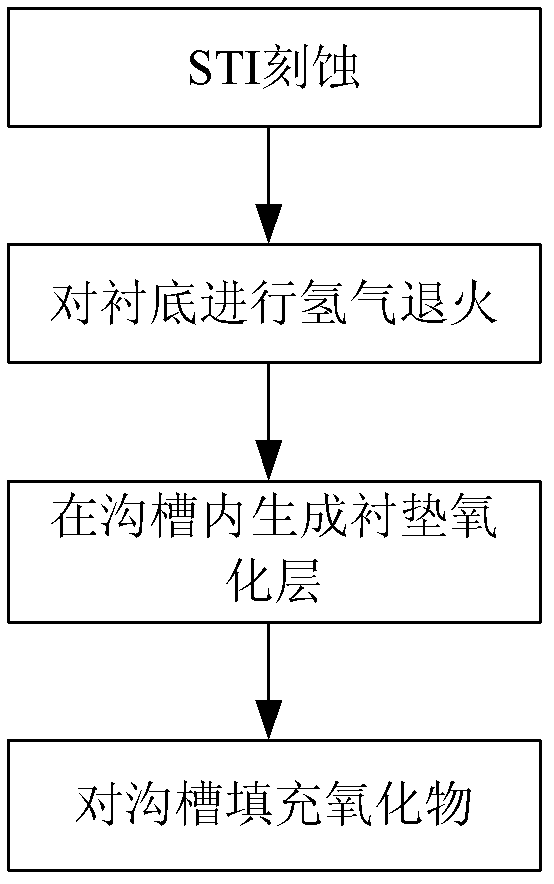

[0022] In the present invention, in order to solve the problems in the prior art, in the process of manufacturing the STI structure, the substrate is subjected to hydrogen annealing treatment after the shallow trenches are formed by etching, so that the rough shallow trench side walls become smooth and shallow. The corners at the bottom of the trench are also rounded, thereby improving the performance of semiconductor devices and integrated circuits.

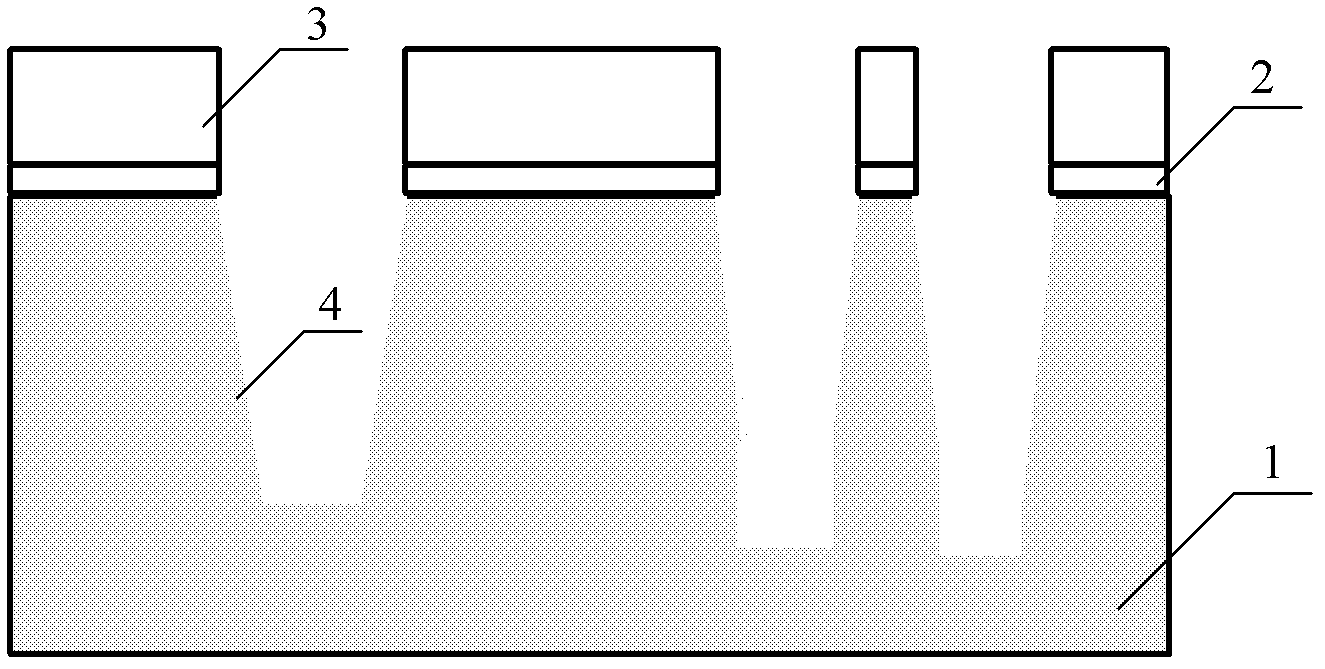

[0023] Such as figure 2 and combine Figure 3a and Figure 3b As shown, as an embodiment of the present invention, when forming shallow trench isolation on the Si substrate 21, a pad oxide layer 22 is first formed on the Si substrate, and a pad oxide layer 22 is de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More